- 1Redis ConnectionException

- 2大数据技术原理与运用习题总结_假设已经配置好环境变量,启动hdfs和关闭hdfs的命令分别是( )和( )

- 3用gitbash提交代码步骤_gitbash提交项目

- 4idea克隆github项目失败:unable to access ‘https://github.com/…’: Failed to connect to github.com port 443 a_idea克隆失败

- 5Vue-Ci搭建项目

- 6Android群英传-拼图游戏puzzle-代码设计和实现

- 7微信小程序生成分享二维码,自定义内容二维码_uniapp微信小程序将数据生成二维码并分享

- 8Python 用Ursina 3D引擎做一个太阳系行星模拟器_ursina获取鼠标准心

- 9Java 生成X.509 V3证书_java生成数字证书

- 10【QML 底层依赖机制】入门 QML:核心机制与灵活选择_qml 设置ui样式 全局设置

F460 CLK配置功能模块说明_f460 tmera

赞

踩

F460CLK配置功能模块说明

目录

14. DDL_EVENT_PORT——作为触发源和触发对象触发

15. DDL_EXINT_NMI_SWI——外部中断输入/外部非可屏蔽中断/软件中断

34. DDL_TIMER4_CNT——通用控制定时器TIMER4计数处理

35. DDL_TIMER4_EMB——通用控制定时器TIMER4 刹车控制

36. DDL_TIMER4_OCO——Output Compare

39. DDL_TIMER6——高级控制定时器( Timer6)

在配置clk的过程中——F460启动过程分析2-f460启动分析和时钟配置,需要了解各模块功能,才能知道需要用到哪些模块,将其clk打开

工作时钟规格

CLK配置:

- /**

- *******************************************************************************

- ** \brief This is the list of modules to be used in the device driver library

- ** Select the modules you need to use to DDL_ON.

- **

- ** \note DDL_ICG_ENABLE must be turned on(DDL_ON) to ensure that the chip works

- ** properly.

- **

- ** \note DDL_UTILITY_ENABLE must be turned on(DDL_ON) if using Device Driver

- ** Library.

- **

- ** \note DDL_PRINT_ENABLE must be turned on(DDL_ON) if using printf function.

- ******************************************************************************/

- #define DDL_ICG_ENABLE (DDL_ON) //打开 初始化配置模块

- #define DDL_UTILITY_ENABLE (DDL_ON) //打开 基础功能函数

- #define DDL_PRINT_ENABLE (DDL_ON) //

-

- #define DDL_ADC_ENABLE (DDL_ON) //打开

- #define DDL_AES_ENABLE (DDL_OFF) //

- #define DDL_CAN_ENABLE (DDL_OFF) //

- #define DDL_CLK_ENABLE (DDL_ON) //打开

- #define DDL_CMP_ENABLE (DDL_OFF) // 电压比较器

- #define DDL_CRC_ENABLE (DDL_OFF) //

- #define DDL_DCU_ENABLE (DDL_OFF) // 数据计算单元

- #define DDL_DMAC_ENABLE (DDL_OFF) // DMA 控制器

- #define DDL_EFM_ENABLE (DDL_ON) //打开 嵌入式 FLASH

- #define DDL_EMB_ENABLE (DDL_OFF) // 紧急刹车模块

- #define DDL_EVENT_PORT_ENABLE (DDL_OFF) // 作为触发源和触发对象触发

- #define DDL_EXINT_NMI_SWI_ENABLE (DDL_ON) //打开 外部中断输入_外部非可屏蔽中断_软件中断 部分

- #define DDL_GPIO_ENABLE (DDL_ON) //打开

- #define DDL_HASH_ENABLE (DDL_OFF) // 安全散列算法

- #define DDL_I2C_ENABLE (DDL_ON) //打开

- #define DDL_I2S_ENABLE (DDL_OFF) //

- #define DDL_INTERRUPTS_ENABLE (DDL_ON) //打开 中断

- #define DDL_INTERRUPTS_SHARE_ENABLE (DDL_ON) //打开 中断

- #define DDL_KEYSCAN_ENABLE (DDL_ON) //打开 键盘扫描控制模块

- #define DDL_MPU_ENABLE (DDL_ON) //打开 存储保护单元

- #define DDL_OTS_ENABLE (DDL_OFF) // 温度传感器

- #define DDL_PWC_ENABLE (DDL_ON) //打开 电源控制

- #define DDL_QSPI_ENABLE (DDL_ON) // 四线式串行外设接口

- #define DDL_RMU_ENABLE (DDL_OFF) // 复位控制

- #define DDL_RTC_ENABLE (DDL_OFF) // 实时时钟

- #define DDL_SDIOC_ENABLE (DDL_OFF) // SDIO 控制器

- #define DDL_SPI_ENABLE (DDL_OFF) // 串行外设接口

- #define DDL_SRAM_ENABLE (DDL_ON) //打开 内置 SRAM

- #define DDL_SWDT_ENABLE (DDL_OFF) // 专用看门狗计数器

- #define DDL_TIMER0_ENABLE (DDL_OFF) // 通用定时器?TIMER0

- #define DDL_TIMER4_CNT_ENABLE (DDL_ON) //打开 通用控制定时器TIMER4计数?

- #define DDL_TIMER4_EMB_ENABLE (DDL_OFF) // 通用控制定时器TIMER4 刹车控制?

- #define DDL_TIMER4_OCO_ENABLE (DDL_OFF) // TIMER4 Output Compare

- #define DDL_TIMER4_PWM_ENABLE (DDL_OFF) // TIMER4通用 PWM 输出

- #define DDL_TIMER4_SEVT_ENABLE (DDL_OFF) // TIMER4专用EVT输出

- #define DDL_TIMER6_ENABLE (DDL_OFF) // 高级控制定时器Timer6? ??

- #define DDL_TIMERA_ENABLE (DDL_ON) //打开 通用定时器TIMERA

- #define DDL_TRNG_ENABLE (DDL_OFF) // 真随机数发生器

- #define DDL_USART_ENABLE (DDL_ON) //打开 通用同步异步收发器

- #define DDL_USBFS_ENABLE (DDL_OFF) // USB2.0 全速模块?

- #define DDL_WDT_ENABLE (DDL_ON) //打开 通用看门狗计数器

1. DDL_ICG——初始化配置

ICG是初始化配置,必须要打开,否则不能正常工作。

在《HC32F460系列数据手册Rev1.22》中,有介绍;

2. DDL_UTILITY——基础功能函数

这部分是一些基础功能函数,包括延时,系统滴答等。如果使用库函数,也是必须要打开。

在帮助文档中,可以看到包含哪些功能函数:

3. DDL_PRINT-待细化

打印相关的功能,默认是UART4

如果使用,必须要打开;

帮助文档中,有相关描述;

4. DDL_ADC

模数转换模块,项目中使用的话要打开;在《HC32F460系列数据手册Rev1.22》中,有介绍;

5. DDL_AES——AES 加解密算法处理器

是AES 加解密算法处理器,在《HC32F460系列数据手册Rev1.22》中第32章,有介绍;

6. DDL_CAN

控制器局域网,在《HC32F460系列数据手册Rev1.22》中第30章,有介绍:

CAN( Controller Area Network)总线是一种可以在无主机情况下实现微处理器或者设备之间相互通信的总线标准。本模块遵循 CAN 总线协议 2.0A 和 2.0B 协议并向上兼容 CAN-FD。 CAN 总线控制器可以处理总线上的数据收发,在本产品中, CAN 具有 8组筛选器。筛选器用于为应用程序选择要接收的消息。

应用程序通过 1 个高优先级的主发送缓冲器( Primary Transmit Buffer, 以下简称 PTB)和 4 个辅发送缓冲器( Secondary Transmit Buffer, 以下简称 STB) 将发送数据送至总线,由发送调度器决定邮箱发送顺序。通过 10 个接收缓冲器( Receive Buffer, 以下简称 RB)获取总线数据。 4 个 STB 以及 10 个 RB 可以理解为一个 4 级 FIFO 和一个 10级 FIFO, FIFO 完全由硬件控制。

CAN 总线控制器同时也可以支持时间触发 CAN 通信( Time-trigger communication)。

7. DDL_CLK

时钟控制器模块,在《HC32F460系列数据手册Rev1.22》中第4章,有介绍:

要根据需要对时钟进行配置,必须要打开;

8. DDL_CMP——电压比较器

电压比较器模块,在《HC32F460系列数据手册Rev1.22》中第15章,有介绍:

9. DDL_CRC

CRC 运算模块,在《HC32F460系列数据手册Rev1.22》中第34章,有介绍:

项目中使用的话就打开,不用可以不打开;

10. DDL_DCU——数据计算单元

数据计算单元模块,在《HC32F460系列数据手册Rev1.22》中第33章,有介绍;

项目中使用的话就打开,不用可以不打开;

11. DDL_DMAC——DMA 控制器

DMA 控制器,在《HC32F460系列数据手册Rev1.22》中第14章,有介绍;

项目中使用的话就打开,不用可以不打开;

12. DDL_EFM——嵌入式 FLASH

内部flash模块,使用的话必须要打开clk;

13. DDL_EMB——紧急刹车模块

紧急刹车模块:紧急刹车模块是在满足一定条件时通知定时器, 以使定时器停止向外部电机输出 PWM信号的功能模块;

14. DDL_EVENT_PORT——作为触发源和触发对象触发

Event Port 输入输出功能,在《HC32F460系列数据手册Rev1.22》中第9.3.4节,有介绍;

支持 4 组 Event Port,每组 16 个端口。 Event Port1 包含 EVNTP100~EVNTP115, Event Port2 包含 EVNTP200~EVNTP215,以此类推。 EVNTPmn (m=1~4, n=0~15) 端口可以作为触发源,根据端口输入生成事件来触发其它周边设备(如 TIMER, ADC, DMA等)开始特定的动作。也可以作为被触发对象,接受事件,自动输入或输出。

作为触发源时,设置 PEVNTRISRm,PEVNTFALRm,PEVNTNFCR 选择上升沿或下降沿检测,以及数字滤波功能,并设置功能选择寄存器 PFSRxy 选择 EVNTPmn 功能。当选择的边沿从端口输入时,则生成事件 EVENT_PORTm,输出到其它周边设备以触发其开始动作。

作为被触发对象时,设置 PEVNTTRGSRm 选择触发事件源,设置 PEVNTDIRRm 选择输出或输入功能。输出功能时,选定事件发生时 EVNTPmn 根据 PEVNTODRm, PEVNTORRm, PEVNTOSRm 设定值输出指定电平。输入功能时,选定事件发生时,EVNTPmn 输入状态保存进寄存器 PEVNTIDRx。

使用 Event Port 功能时,需要先将功能时钟控制 0 寄存器(FCG0)的外围电路触发功能使能位置设为有效。

注意:– 端口 PB11 与 MD 复用,为输入专用端口,故 EVNTP211 无输出功能。

15. DDL_EXINT_NMI_SWI——外部中断输入/外部非可屏蔽中断/软件中断

外部中断输入,外部非可屏蔽中断,和软件中断。主要在《HC32F460系列数据手册Rev1.22》中第10章,有介绍;

EXINT:外部中断输入。在《HC32F460系列数据手册Rev1.22》中第9.3.5节,有介绍;

NMI:外部非可屏蔽中断。在《HC32F460系列数据手册Rev1.22》中第9.3.4节,有介绍;

SWI: 软件中断。在《HC32F460系列数据手册Rev1.22》中第10.5.12节,有介绍;

16. DDL_GPIO——通用 IO

在《HC32F460系列数据手册Rev1.22》中第9章,有介绍;

17. DDL_HASH——安全散列算法

在《HC32F460系列数据手册Rev1.22》中第32章,有介绍;

加密协处理模块( CPM)包括 AES 加解密算法处理器, HASH 安全散列算法, TRNG真随机数发生器三个子模块。

AES 加解密算法处理器遵循标准数据加密解密标准,可以实现 128 位密钥长度的加密运算和解密运算。

HASH 安全散列算法是 SHA-2 版本的 SHA-256( Secure Hash Algorithm),符合美国国家标准和技术局发布的国家标准“ FIPS PUB 180-3”,可以对长度不超过 2^64 位的消息产生 256 位的消息摘要输出。

TRNG 真随机数发生器是以连续模拟噪声为基础的随机数发生器,提供 64bit 随机数。

18. DDL_I2C

集成电路总线。I²C(集成电路总线)用作微控制器和 I²C 串行总线之间的接口。提供多主模式功能,可以控制所有 I²C 总线的协议、 仲裁。 支持标准模式、 快速模式。 还支持 SMBus 总线。

在《HC32F460系列数据手册Rev1.22》中第26章,有介绍;

19. DDL_I2S

集成电路内置音频总线模块。I2S( Inter_IC Sound Bus),集成电路内置音频总线,该总线专责于音频设备之间的数据传输。

在《HC32F460系列数据手册Rev1.22》中第29章,有介绍;

20. DDL_INTERRUPTS——?

帮助文档里在hc32f460_interrupts.c 中有详细说明

21. DDL_INTERRUPTS_SHARE——?

22. DDL_KEYSCAN——键盘扫描控制模块

本产品搭载键盘控制模块( KEYSCAN) 1 个单元。 KEYSCAN 模块支持键盘阵列( 行

和列) 扫描,列是由独立的扫描输出 KEYOUTm(m=0~7)驱动, 而行 KEYINn(n=0~15)则

作为 EIRQn(n=0~15)输入被检测。本模块通过行扫描查询法实现按键识别功能

在《HC32F460系列数据手册Rev1.22》中第12章,有介绍;

23. DDL_MPU——存储保护单元

MPU 可以提供对存储器的保护,通过阻止非授权的访问,可以提高系统的安全性。

本芯片内置了四个针对主机的 MPU 单元和一个针对 IP 的 MPU 单元

在《HC32F460系列数据手册Rev1.22》中第13章,有介绍;

24. DDL_OTS——温度传感器

温度传感器( On-chip Temperature Sensor,以下简称 OTS)可以获取芯片内部的温度,以支持系统的可靠性操作。 OTS 提供了一组与温度相关的数字量,通过计算可以得到温度值。不使用时可以通过模块停止功能将其关闭以减少系统功耗

在《HC32F460系列数据手册Rev1.22》中第17章,有介绍;

25. DDL_PWC——电源控制

电源控制器用来控制芯片的多个电源域在多个运行模式和低功耗模式下的电源供给、切换、检测。电源控制器由功耗控制逻辑(PWC)、电源电压检测单元(PVD)构成

在《HC32F460系列数据手册Rev1.22》中第5章,有介绍;

26. DDL_QSPI—— 四线式串行外设接口

四线式串行外设接口( QSPI)是一个存储器控制模块,主要用于和带 SPI 兼容接口的串行 ROM 进行通信。其对象主要包括有串行闪存,串行 EEPROM 以及串行 FeRAM。

在《HC32F460系列数据手册Rev1.22》中第28章,有介绍;

27. DDL_RMU——复位控制

在《HC32F460系列数据手册Rev1.22》中第3章,有介绍;

28. DDL_RTC——实时时钟

实时时钟 (RTC) 是一个以 BCD 码格式保存时间信息的计数器。记录从 00 年到 99 年间的具体日历时间。支持 12/24 小时两种时制, 根据月份和年份自动计算日数 28、 29(闰年)、 30 和 31 日。

在《HC32F460系列数据手册Rev1.22》中第23章,有介绍;

29. DDL_SDIOC——SDIO 控制器

SDIOC 提供了一个 SD 主机接口和一个 MMC 主机接口,用于和支持 SD2.0 协议的 SD卡,SDIO 设备以及支持 eMMC4.2 协议的 MMC 设备进行通信。

在《HC32F460系列数据手册Rev1.22》中第35章,有介绍;

30. DDL_SPI——串行外设接口

本产品搭载 4 个通道的串行外设接口 SPI,支持高速全双工串行同步传输,方便地与

外围设备进行数据交换。用户可根据需要进行三线/四线, 主机/从机及波特率范围的设

置。

在《HC32F460系列数据手册Rev1.22》中第27章,有介绍;

31. DDL_SRAM——内置 SRAM

本 产 品 带 有 4KB 掉 电 模 式 保 持 SRAM ( Ret_SRAM ) 和 188KB 系 统 SRAM( SRAMH/SRAM1/ SRAM2/SRAM3)。SRAM 可按照字节、半字( 16 位)或全字( 32 位)访问。读写操作以 CPU 速度执行,可插入等待周期。读写访问的等待周期设定和 CPU 时钟频率的关系如表 8-1 所示。各个 SRAM 的读写访问的等待周期由 SRAM 等待控制寄存器( SRAM_WTCR)设定。

在《HC32F460系列数据手册Rev1.22》中第8章,有介绍;

32. DDL_SWDT——专用看门狗计数器

看门狗计数器有两个,一种是计数时钟源为专用内部 RC( SWDTLRC:10KHz)的专用看门狗计数器( SWDT), 另一种是计数时钟源为 PCLK3 的通用看门狗计数器( WDT)。

专用看门狗和通用看门狗是 16 位递减计数器,用来监测由于外部干扰或不可预见的逻辑条件造成的应用程序背离正常的运行而产生的软件故障。

两个看门狗都支持窗口功能。在计数开始前可预设窗口区间,计数值位于窗口区间时,可刷新计数器,计数重新开始。

在《HC32F460系列数据手册Rev1.22》中第24章,有介绍;

33. DDL_TIMER0——通用定时器 TIMER0

通用定时器 0( Timer0)是一个可以实现同步计数 、异步计数两种方式的基本定时器。该定时器内含 2 个通道,可以在计数期间产生比较匹配事件。该事件可以触发中断,也可作为事件输出来控制其它模块等。本系列产品中搭载 2 个单元的 Timer0。

在《HC32F460系列数据手册Rev1.22》中第22章,有介绍;

34. DDL_TIMER4_CNT——通用控制定时器TIMER4计数

通用控制定时器 4( Timer4)是一个用于三相电机控制的定时器模块,提供各种不同应用的三相电机控制方案。该定时器支持三角波和锯齿波两种波形模式,可生成各种PWM 波形;支持缓存功能;支持 EMB 控制。本系列产品中搭载 3 个单元的 Timer4。

在《HC32F460系列数据手册Rev1.22》中第19.3.1.2小节,有介绍;

帮助文档中“Timer4 Counter(Timer4CNT)”是具体设置处;

35. DDL_TIMER4_EMB——通用控制定时器TIMER4 刹车控制

在《HC32F460系列数据手册Rev1.22》中第19章,有介绍;

帮助文档中hc32f460_timer4_emb.c是具体处理的;

36. DDL_TIMER4_OCO——TIMER4 Output Compare

帮助文档中 Timer4 Output Compare(Timer4OCO)是具体处理的;

在《HC32F460系列数据手册Rev1.22》中第19章,有介绍;

37. DDL_TIMER4_PWM——TIMER4通用 PWM 输出

帮助文档中有对函数 hc32f460_timer4_pwm.c 进行说明;

在《HC32F460系列数据手册Rev1.22》中第19章,有介绍;

38. DDL_TIMER4_SEVT——TIMER4专用EVT输出

帮助文档中有对函数 hc32f460_timer4_sevt.c 进行说明;

在《HC32F460系列数据手册Rev1.22》中第19章,有介绍;

39. DDL_TIMER6——高级控制定时器Timer6

在《HC32F460系列数据手册Rev1.22》中第18章,有介绍;

高级控制定时器 6( Timer6)是一个 16 位计数宽度的高性能定时器,可用于计数产生不同形式的时钟波形,输出以供外部使用。该定时器支持三角波和锯齿波两种波形模式,可生成各种 PWM 波形;单元间可实现软件同步计数和硬件同步计数;各基准值寄存器支持缓存功能;支持 2 相正交编码和 3 相正交编码;支持 EMB 控制。本系列产品中搭载 3 个单元的 Timer6。

40. DDL_TIMERA——通用定时器TIMERA

在《HC32F460系列数据手册Rev1.22》中第21章,有介绍;

通用定时器 A( TimerA) 是一个具有 16 位计数宽度、 8 路 PWM 输出的定时器。 该定时器支持三角波和锯齿波两种波形模式,可生成各种 PWM 波形;支持计数器同步启动;比较基准值寄存器支持缓存功能;支持单元间级联实现 32 位计数; 支持 2 相正交编码计数和 3 相正交编码计数。本系列产品搭载 6 个单元 TimerA,最大可实现 48 路PWM 输出。

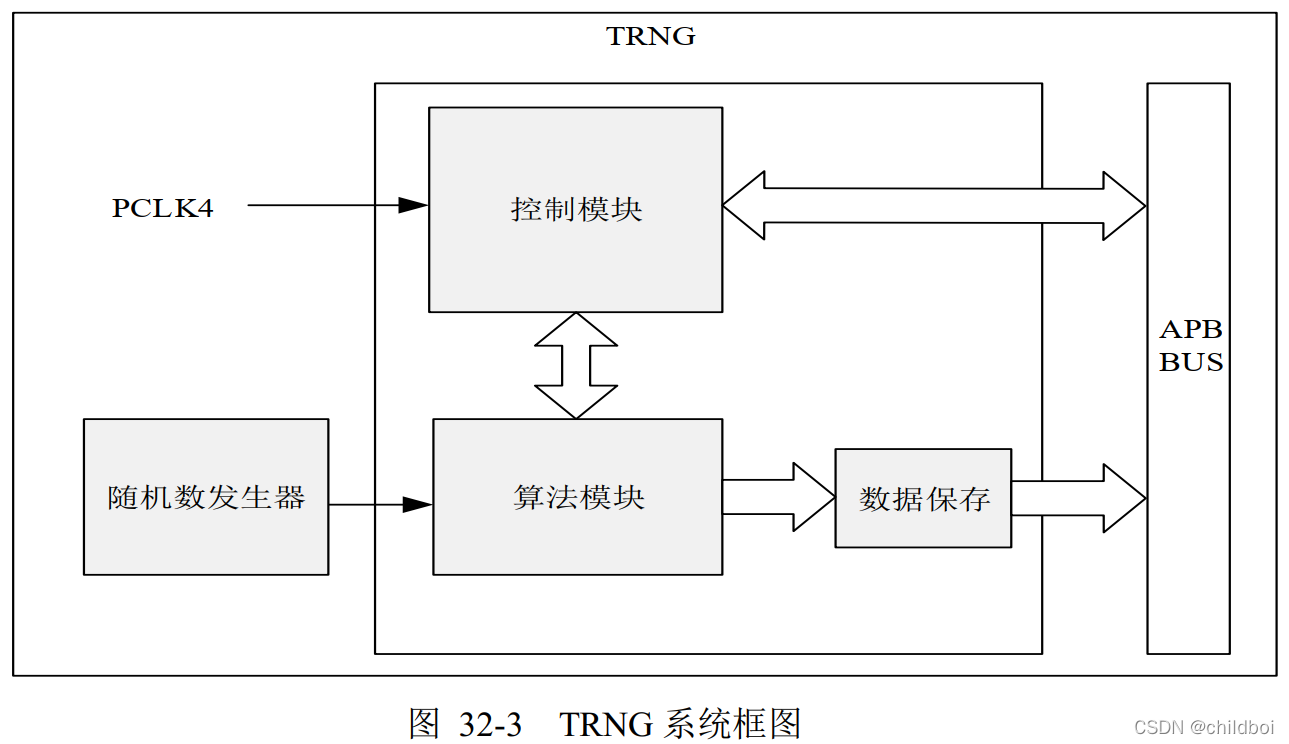

41. DDL_TRNG——真随机数发生器

在《HC32F460系列数据手册Rev1.22》中第32.4小节,有介绍;

TRNG 模块提供 1 个真随机数发生器,产生 1 个 64 位随机数。

TRNG 的系统框图如下图 32-3 所示。其中随机数发生器是一个模拟随机数发振器电路,用于得到随机性的噪声;算法模块捕捉随机噪声并把结果保存至数据模块、并通过总线输出;控制模块控制 TRNG 的模式和启动。

42. DDL_USART——通用同步异步收发器

在《HC32F460系列数据手册Rev1.22》中第25章,有介绍;

本产品搭载通用串行收发器模块( USART) 4 个单元。通用串行收发器模块( USART)能够灵活地与外部设备进行全双工数据交换;本 USART 支持通用异步串行通信接口( UART), 时钟同步通信接口,智能卡接口 (ISO/IEC7816-3)。 支持调制解调器操作(CTS/RTS 操作), 多处理器操作。和 Timer0 模块配合支持 UART 接收 TIMEOUT 功能。

43. DDL_USBFS——USB2.0 全速模块

在《HC32F460系列数据手册Rev1.22》中第31章,有介绍;

USB 全速( USBFS)控制器为便携式设备提供了一套 USB 通信解决方案。 USBFS 控制器支持主机模式和设备模式,且芯片内部集成全速 PHY。主机模式下, USBFS 控制器支持全速( FS, 12Mb/s) 和低速( LS, 1.5Mb/s) 收发器, 而设备模式下则仅支持全速( FS, 12Mb/s) 收发器。 USBFS 控制器支持 USB 2.0 协议所定义的所有四种传输方式(控制传输、批量传输、中断传输和同步传输)。

44. DDL_WDT——通用看门狗计数器

在《HC32F460系列数据手册Rev1.22》中第24章,有介绍;

看门狗计数器有两个,一种是计数时钟源为专用内部 RC( SWDTLRC:10KHz)的专用看门狗计数器( SWDT), 另一种是计数时钟源为 PCLK3 的通用看门狗计数器( WDT)。

专用看门狗和通用看门狗是 16 位递减计数器,用来监测由于外部干扰或不可预见的逻辑条件造成的应用程序背离正常的运行而产生的软件故障。

两个看门狗都支持窗口功能。在计数开始前可预设窗口区间,计数值位于窗口区间时,可刷新计数器,计数重新开始。