- 1爆火!!!中文版 Llama3 开源了!!_ollama llama3 强制用中文回答

- 2520表白神器,小贺只能帮你到这了......

- 32024年,计算机相关专业还值得选择吗?_计算机专业现在饱和了吗

- 4Android 应用程序集成Google 登录及二次封装_com.google.android.gms.auth.api

- 5error: RPC failed; curl 18 transfer closed with outstanding read data remaining fatal: the remote en_linux搭建http server 下载文件出现curl: (18) transfer close

- 6Android Studio 安卓模拟器无法连接网络_androidstudio模拟器没网络

- 7Elasticsearch介绍2

- 8Kubernetes1.23搭建Elasticsearch7集群(集群加密)_kubernetes部署单机elasticsearch7.16.2

- 9【Diffusers库】第五篇 加载pipeline、model、schedulers_diffusers pipline没有本地模型

- 10神仙级AI大模型入门教程(非常详细),从零基础入门到精通,从看这篇开始!_大模型教程

可变频率正弦信号发生器的FPGA实现(Quartus)_fpga正弦信号发生器

赞

踩

一、说明

实现平台:Quartus17.1、MATLAB2021a和Modelsim SE-64 10.4

二、内容

1. 产生一个完整周期的正弦波信号,并保存为*.mif文件;

2. 设计一个ROM,将正弦波信号文件初始化如该ROM中;

3. 设计一正弦波信号发生器,按照读取步长,产生频率可变的正弦波信号;

4.编写测试文件,通过modelsim查看波形。

三、步骤

(1)设计要求

- 要求设计一个可变频率的正弦波产生器,主要参数为:

- 50MHz的主时钟clock,低电平有效复位,reset;

- 输出正弦波,8位输出;

- 通过改变读地址的步进值,使输出的正弦波频率可变。

(2)设计思路

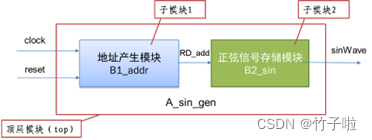

采用top_down设计思想,将正弦波产生器分为三个模块。分别是顶层模块A_sin_gen,子模块B1_addr和子模B2_sin。

图1 设计的总体框图

其中顶层模块主要定义输入输出关系,划分两个子模块的接口,搭建起两个子模块的框架,整个设计要素如图2所示:

图2 顶层模块A_sin_gen的设计要素

子模块B1_addr主要用来产生对ROM的寻址。按照时钟街拍,改变寻址的步进,就可以改变输出正弦波的频率。该模块可以采用简单的向上计数器产生。模块设计要素如图3所示:

图3. 子模块B1_addr的设计要素

子模块B2_sin则主要用LPM_ROM宏模块产生。

(3)具体实现

- 首先通过MATLAB产生产生长度1024,8Bits位宽的正弦信号,并生成mif文件,代码如下:

- %%产生长度1024,8Bits位宽的正弦信号,并生成mif文件

-

- depth =1024; %存储器的单元数1024

- widths = 8; %数据宽度为8位

- fidc = fopen('sine.mif','wt'); %给文件命名

- fprintf(fidc , 'depth = %d;\n',depth); %在文件中打印 "depth=1024;"

- fprintf(fidc, 'width = %d;\n',widths); %在文件中打印 width=8;”

- fprintf(fidc, 'address_radix = UNS;\n'); %在文件中打印 address_radix = UNS;”

- fprintf(fidc,'data_radix = UNS;\n'); %在文件中打印 “data_radix = UNS;”

- fprintf(fidc,'content begin\n'); %在文件中打印 content begin

-

- for(x = 1 : depth)

- fprintf(fidc,'%d:%d;\n',x-1,round(127*sin(2*pi*(x-1)/256)+128));

- end

- fprintf(fidc, 'end;');

- fclose(fidc);

2.打开quartus新建工程,首先设计顶层模块,代码如下:

- //-------------------------------------

- //Date:Nov,15th,2022-----------------

- //Author:Zhuzi------------------------

- //Description:Generate variable frequency sine wave.

- //Version:1.0--------------------------

- //-------------------------------------

-

- module a_sin_gen(clk,rst_n,sin_wave);

- input clk; //时钟信号50MHz

- input rst_n; //复位信号

- output [7:0] sin_wave; //正弦信号

-

- wire [9:0] RD_addr; //rom地址

- wire [7:0] sin_out; //读取正弦信号

-

- B1_addr u1( //例化模块1

- .clk (clk),

- .rst_n (rst_n),

- .RD_addr(RD_addr)

- );

-

- B2_sin u2( //例化模块2

- .clk (clk),

- .add_in (RD_addr),

- .sin_out(sin_out)

- );

-

- assign sin_wave = sin_out; //输出正弦信号

-

- endmodule

-

-

3.接着按顺序设计模块1和模块2。子模块B1_addr用来产生对ROM的寻址,代码如下:

- module B1_addr(clk,rst_n,RD_addr);

- input clk;

- input rst_n;

- output [9:0] RD_addr;

-

- parameter step = 5;//ROM寻址步长

- reg [9:0] addr;

-

- assign RD_addr = addr;

-

- always @(posedge clk or negedge rst_n)begin

- if(!rst_n)

- addr <= 0;

- else addr <= addr + step;

- end

-

- endmodule

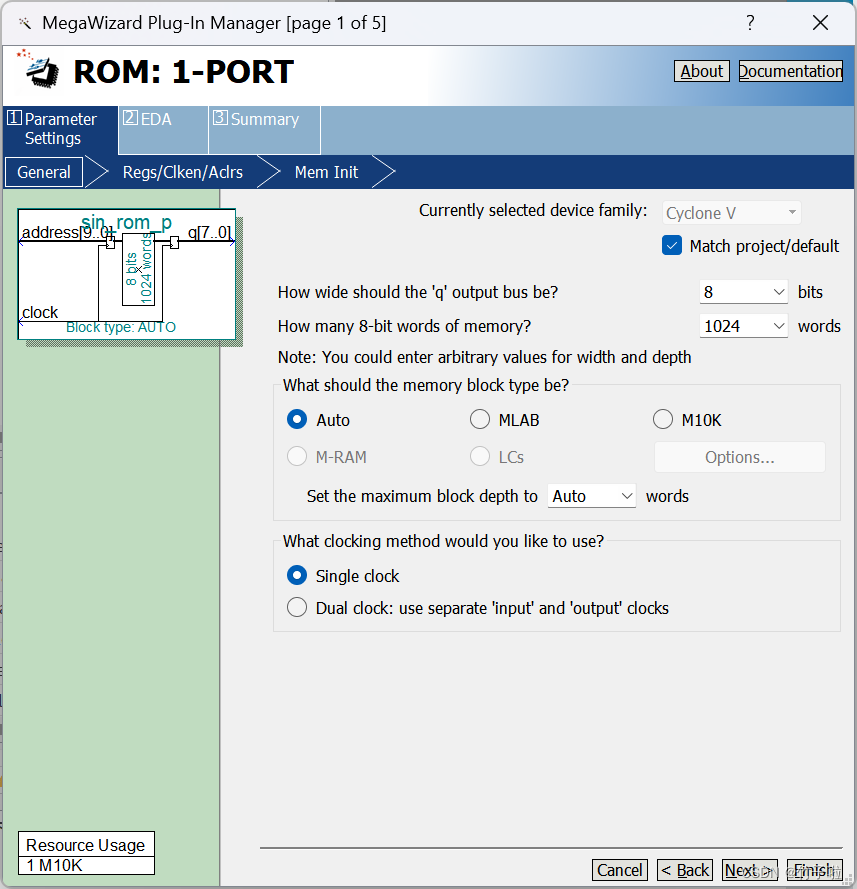

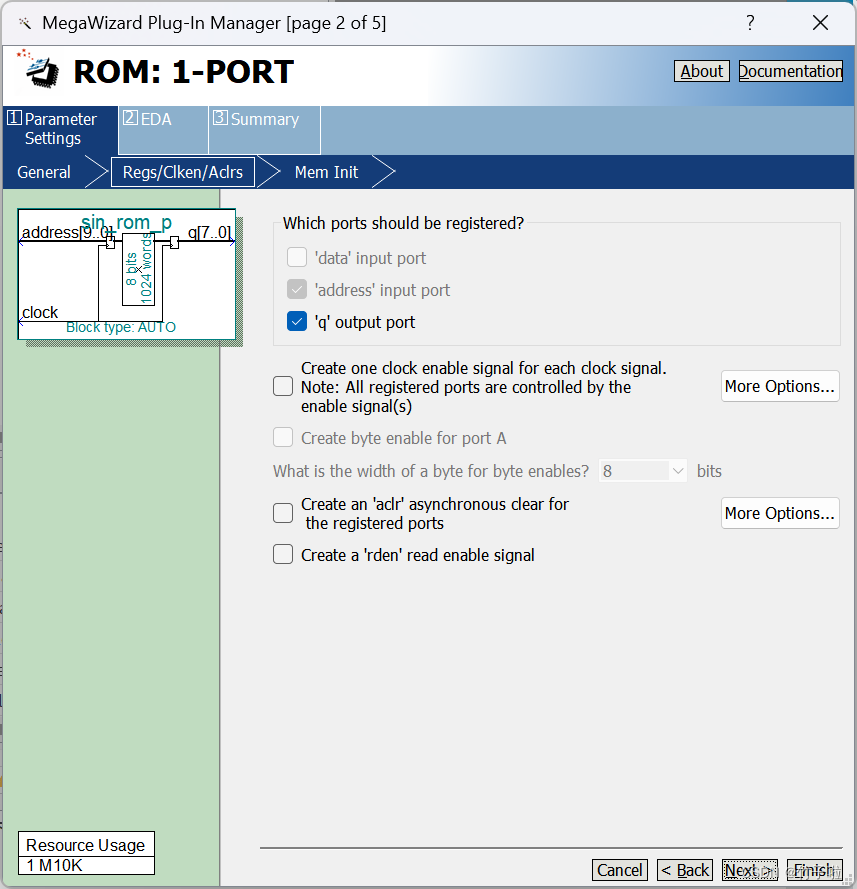

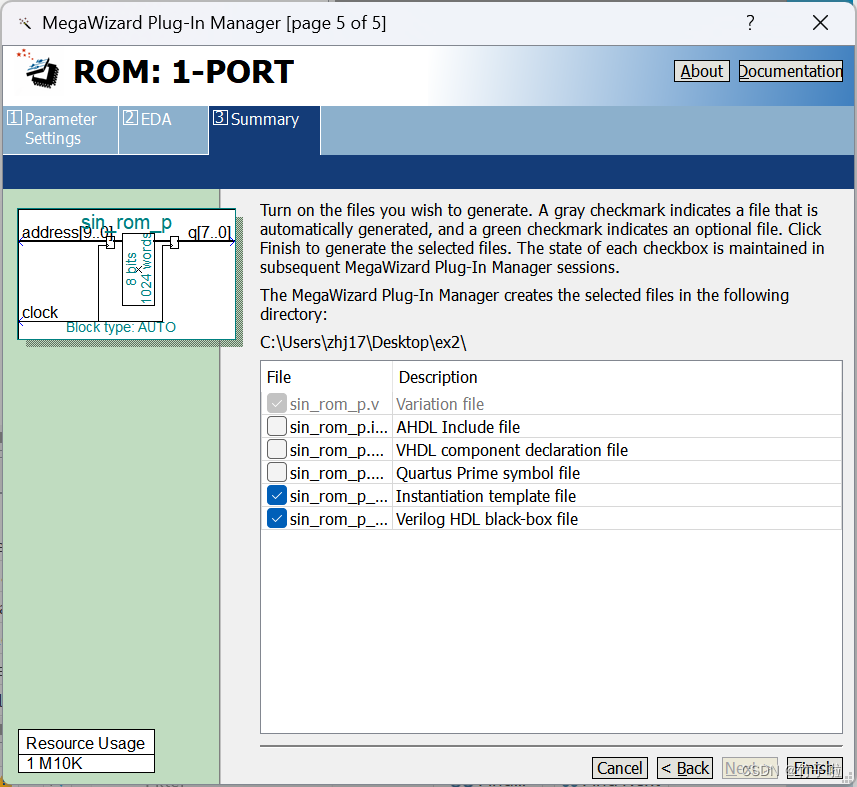

4.子模块B2_sin需要调用LPM_ROM宏功能模块,根据设计要求,ROM核的设置如下:

子模块B2_sin代码如下:

- module B2_sin(clk,add_in,sin_out);

- input clk;

- input [9:0] add_in;

- output [7:0] sin_out;

-

- sin_rom_p u3(

- .address(add_in),

- .clock(clk),

- .q(sin_out)

- );

-

- endmodule

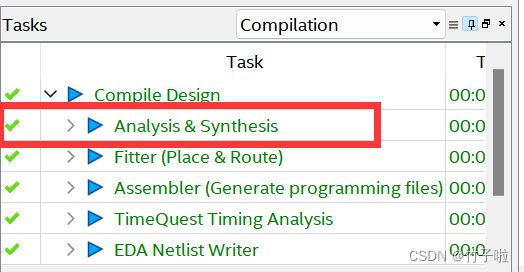

5.程序设计完成后点击综合,只要综合完成即可进行下一步。

设计完成后可以看到RTL原理图如下所示,基本符合预期。

6.TestBench程序编写如下:

- `timescale 1 ns/ 1 ns

- module a_sin_gen_vlg_tst();

-

- reg clk;

- reg rst_n;

- wire [7:0] sin_wave;

-

- a_sin_gen i1 (

- .clk(clk),

- .rst_n(rst_n),

- .sin_wave(sin_wave)

- );

-

- initial

- begin

- clk = 0;

- rst_n = 0;

- #100;

- rst_n = 1;

- end

-

- always #10 clk = ~clk;

-

- endmodule

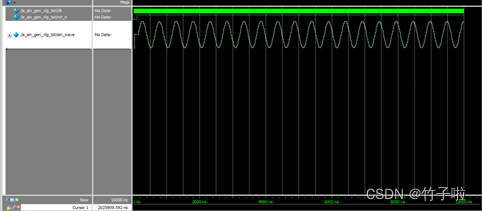

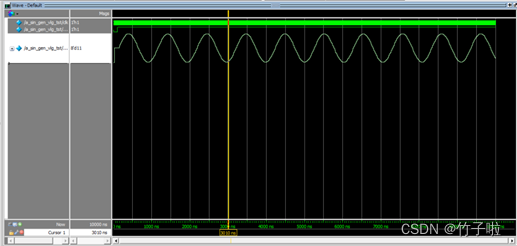

(4)仿真结果

1.修改子模块1中的parameter参数即可改变步长,当ROM寻址步长为10时,测试仿真波形如下图所示:

2. 当ROM寻址步长为5时,测试仿真波形如下图所示:

通过上述结果可知,改变寻址步长即可调整产生正弦波的频率,表明实验成功。