热门标签

热门文章

- 1数据结构-分析期末选择题考点(排序)

- 2Java-集合(ArrayList类)_java里面arrlist里面可以存放多少个null

- 3大疆测试面经(部分附答案)_大疆python测试面试

- 4llama-factory学习个人记录_raise valueerror("please launch distributed traini

- 5快速排序的时间复杂度和空间复杂度分析(图文结合)

- 6explain sql实际分析_explan sql

- 7stm32移植到国产MCU雅特力AT32_at32f437vgt7

- 8计算机毕业设计PySpark+Hadoop地震预测系统 地震数据分析可视化 地震爬虫 大数据毕业设计 Flink Hadoop 深度学习 机器学习 人工智能 知识图谱 大数据毕业设计_基于python的全球地震信息数据可视化分析平台研究技术可行性

- 9python+Django学生管理系统_django 实现管理系统

- 10MybatisPlus存在 sql 注入漏洞(CVE-2023-25330)解决办法

当前位置: article > 正文

Quartus II 实验 (三)——图形化编程4位全加器,4位乘法阵列_使用图形编辑工具实现4位全加器并验证

作者:盐析白兔 | 2024-06-12 11:45:02

赞

踩

使用图形编辑工具实现4位全加器并验证

0x1前言

计算机组成原理实验项目之一,要求使用Quartus II 的图形化编程制作 4位全加器 和 两个4位四位数相乘的乘法阵列。

本篇假定,你已经掌握Quartus II 和 DICE-E213实验箱的基本使用,如果遇到问题可以参考Quartus II 实验 (一)——软件和实验箱DICE-E213的基本说明

x02制作 4位全加器

步骤一:制作一个半加器

导出半加器,并作为模块存放到下一个工程的目录下,具体做法可以参考Quartus II 实验 (一)——软件和实验箱DICE-E213的基本说明,以后的每个工程的调用以此类推。需要注意,调用很可能是递归的,所以所有引用的模块都要连带传递。

步骤二:制作一个全加器

步骤三:制作一个4位加法器

步骤四:排布引脚

- 引脚对应图:

步骤五:编译,上电!烧入实验箱

步骤七:测试

测试时看准引脚对应的输入,并且需要强调对于本试验箱输出模块亮为0灭为1,找到那一端是地位那一端是高位,比较无脑,不再赘述。

0x3制作 4位乘法阵列

- 流程和上面一样,这里不再赘述,贴一下引脚图做一点说明:

ABCD是初始置0000,开关输入量一定要置0000,否则结果不对,CC是低位进位。

另外是,两组4位输入,和一组8位输出。

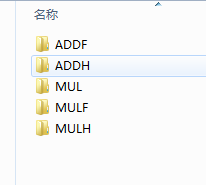

- 目录结构是:

ADDH-->ADDF-->MULH-->MULF-->MUL

0x4提供以上两个工程的源文件,供大家参考。

四位乘法阵、\四位加法器 http://sudo.ys168.com/ 公共下载区

备用链接:https://download.csdn.net/download/qq_41420747/11247995

0x5结束收工

在试验过程中如有错误,欢迎留言,讨论,也欢迎指出我的错误。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/盐析白兔/article/detail/707964

推荐阅读

相关标签