- 1任务4.8.4 利用Spark SQL实现分组排行榜

- 2python小游戏开心消消乐制作9-连接路径和广度优先搜索_广度优先搜索 游戏

- 3ORA-12514: TNS: 监听程序当前无法识别连接描述符中请求服务的解决方法_ora12514监听程序当前无法识别连接描述符中请求的服务

- 4基于微信小程序的助农电商系统设计与实现-计算机毕业设计源码+LW文档_助农商城小程序的设计与实现

- 5windows11 取消windows登录密码 共享文件夹 输入法 去掉屏保广告 右键恢复原样_win11关闭密码保护共享

- 6github中的watch、star、fork的含义

- 7最近,大模型岗位爆了。。。

- 8机器学习实战 泰坦尼克号生存预测_泰坦尼克号生存预测数据下载

- 9vue的element文档_vue文档 elementui

- 10人工智能:算法如何使系统变得智能_人工智能是如何变智能的

【友晶科技】基于FPGA的贪吃蛇游戏设计(三)——计分模块_fpga计分器

赞

踩

DE10-Standard/DE1-SoC/DE2-115

计分模块任务一

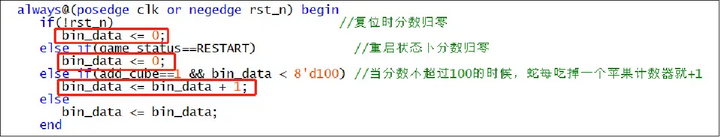

游戏计分模块(score_ctrl.v)完成的任务之一:蛇每吃掉一个食物,计数器值增加1,直到计数到100结束。

该功能直接用一个计数器电路实现。

(注:在食物产生模块apple_generate.v中,蛇每吃掉一个食物,add_cube信号被置1。)

计分模块任务二

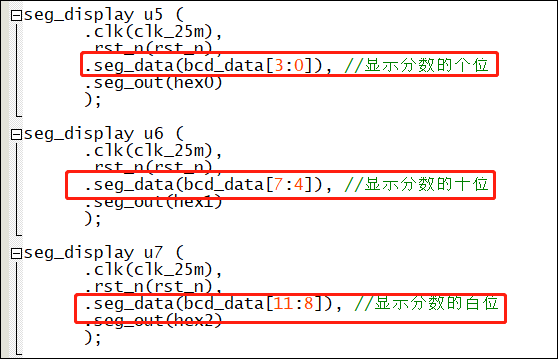

游戏计分模块(score_ctrl.v)完成的任务之二:将计数器数据bin_data转成BCD码形式输出。

用数码管显示一个十进制数的时候,每个数码管只能显示十进制数的一个位,比如游戏中显示分数范围0-100,需要三个数码管,依次显示十进制的百位,十位,个位。计数器数据bin_data是二进制的,无法直接输出到数码管显示,可先用除法取余的方法将分数的百位、十位和个位分离出来:

- assign bcd_data[3:0] = bin_data%10; //算出十进制数的个位

- assign bcd_data[7:4] = (bin_data/10)%10; //算出十进制数的十位

- assign bcd_data[11:8] = (bin_data/100)%10; //算出十进制数的百位

然后在顶层模块,将分数的百位、十位和个位分配到对应的数码管上进行显示:

计分模块完整代码

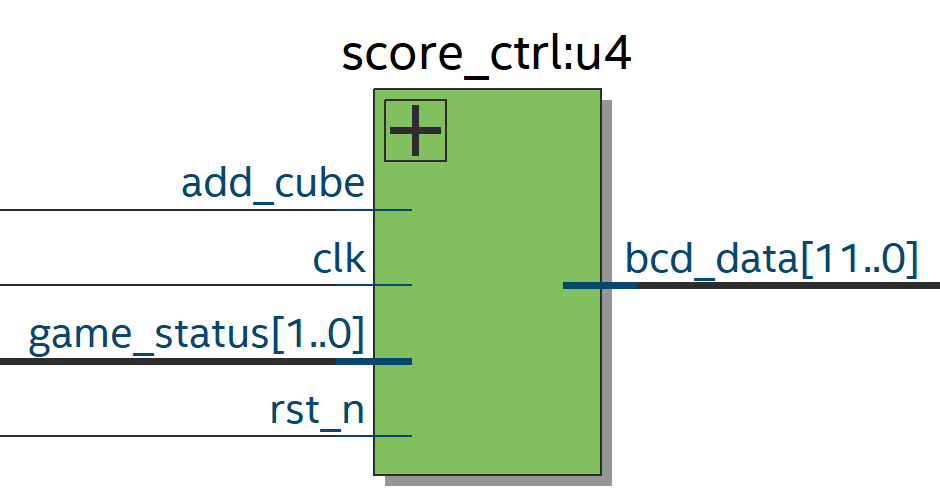

计分模块RTL视图:

计分模块score_ctrl.v完整代码如下:

- //数码管计分模块

- module score_ctrl

- (

- input clk,//25MHz

- input rst_n,//系统复位

-

- input add_cube,//蛇吃掉一个苹果,该信号为高

- input [1:0]game_status,//游戏状态

-

- output [11:0]bcd_data//计分

- );

- reg [7:0]bin_data;//二进制计分寄存器,最小值0000 0000 ,最大值0110 0100(也就是十进制100)

-

- localparam RESTART = 2'b00;//游戏的第1个状态是重启

-

- always@(posedge clk or negedge rst_n) begin

- if(!rst_n) //复位时分数归零

- bin_data <= 0;

- else if(game_status==RESTART) //重启状态下分数归零

- bin_data <= 0;

- else if(add_cube==1 && bin_data < 8'd100) //当分数不超过100的时候,蛇每吃掉一个苹果计数器就+1

- bin_data <= bin_data + 1;

- else

- bin_data <= bin_data;

- end

-

- assign bcd_data[3:0] = bin_data%10; //算出十进制数的个位

- assign bcd_data[7:4] = (bin_data/10)%10; //算出十进制数的十位

- assign bcd_data[11:8] = (bin_data/100)%10; //算出十进制数的百位

-

- endmodule

二进制码转换比较

当然,使用除法和取余的代码看起来非常简洁,但很占用FPGA 的逻辑资源,这里用的是DE10-Standard开发板,逻辑资源充足(110K LEs), 但如果大家是移植到其他资源有限的开发板上,可以选择二进制转BCD码的算法(如加3移位法)以节省更多资源。

另外也可以直接将bin_data信号转成BCD码计数,代码如下:

- if(add_cube) begin

- if(bin_data[3:0] < 9) begin

- bin_data[3:0] <= bin_data[3:0] + 1;

- end

-

- else begin

- bin_data[3:0] <= 0;

- if(bin_data[7:4] < 9) begin

- bin_data[7:4] <= bin_data[7:4] + 1;

- end

-

- else begin

- bin_data[7:4] <= 0;

- if(bin_data[11:8] < 9) begin

- bin_data[11:8] <= bin_data[11:8] + 1;

- end

-

- else begin

- bin_data[11:8] <= 0;

- end

- end

- end

- end

贪吃蛇系列连载文章:

1. 基于FPGA的贪吃蛇游戏设计(一)

2. 基于FPGA的贪吃蛇游戏设计(二)——数码管驱动模块

3. 基于FPGA的贪吃蛇游戏设计(三)——计分模块

4. 基于FPGA的贪吃蛇游戏设计(四)——VGA驱动模块色块显示

5. 基于FPGA的贪吃蛇游戏设计(五)——VGA驱动模块字符显示

6. 基于FPGA的贪吃蛇游戏设计(六)——VGA驱动模块图片显示

7. 基于FPGA的贪吃蛇游戏设计(七)——食物(苹果)的产生

8. 基于FPGA的贪吃蛇游戏设计(八)——状态机设计

9. 基于FPGA的贪吃蛇游戏设计(九)——蛇身控制

关注“友晶Terasic”公众号可获取源码下载地址。

移植到DE1-SOC、DE2-115时代码无需改变,只需修改引脚分配即可。