热门标签

热门文章

- 1如何把AI聊天模型接入QQ_给qq接入ai

- 2文件上传下载容易引发的安全问题及如何预防_上传文件安全性考虑

- 3本地连接虚拟机中Redis出现的问题(远程连接redis)_本地连不上虚拟机的redis

- 4【案例分析】基于IMDb数据集的印度电影信息剖析_imdb电影信息

- 5已成功与服务器建立连接,但是在登录过程中发生错误。(provider: SSL提供程序,error:0-证书链是由不受信任的颁发机构颁发的。)_已成功与服务器建立连接,但是在登录过程中发生错误。 (provider: ssl 提供程序, e

- 6Android:双非大二3轮技术面+HR面(1),三面蚂蚁核心金融部_mateapp hr面

- 7第三章-AllData数据中台-开源团队_alldatadc

- 8如何下载视频号的视频文件?_视频号下载文件报错

- 9由maven sources.jar逆向成可运行的java工程_reverse-m2-sources

- 10面试?跳槽?涨薪?这些你必须先了解:互联网大厂的薪资和职级一览!_腾讯产品职级

当前位置: article > 正文

Xilinx FPGA:vivado单端RAM实现输出偶数(单端RAM的简单应用)

作者:小桥流水78 | 2024-06-27 13:33:31

赞

踩

Xilinx FPGA:vivado单端RAM实现输出偶数(单端RAM的简单应用)

一、实验步骤

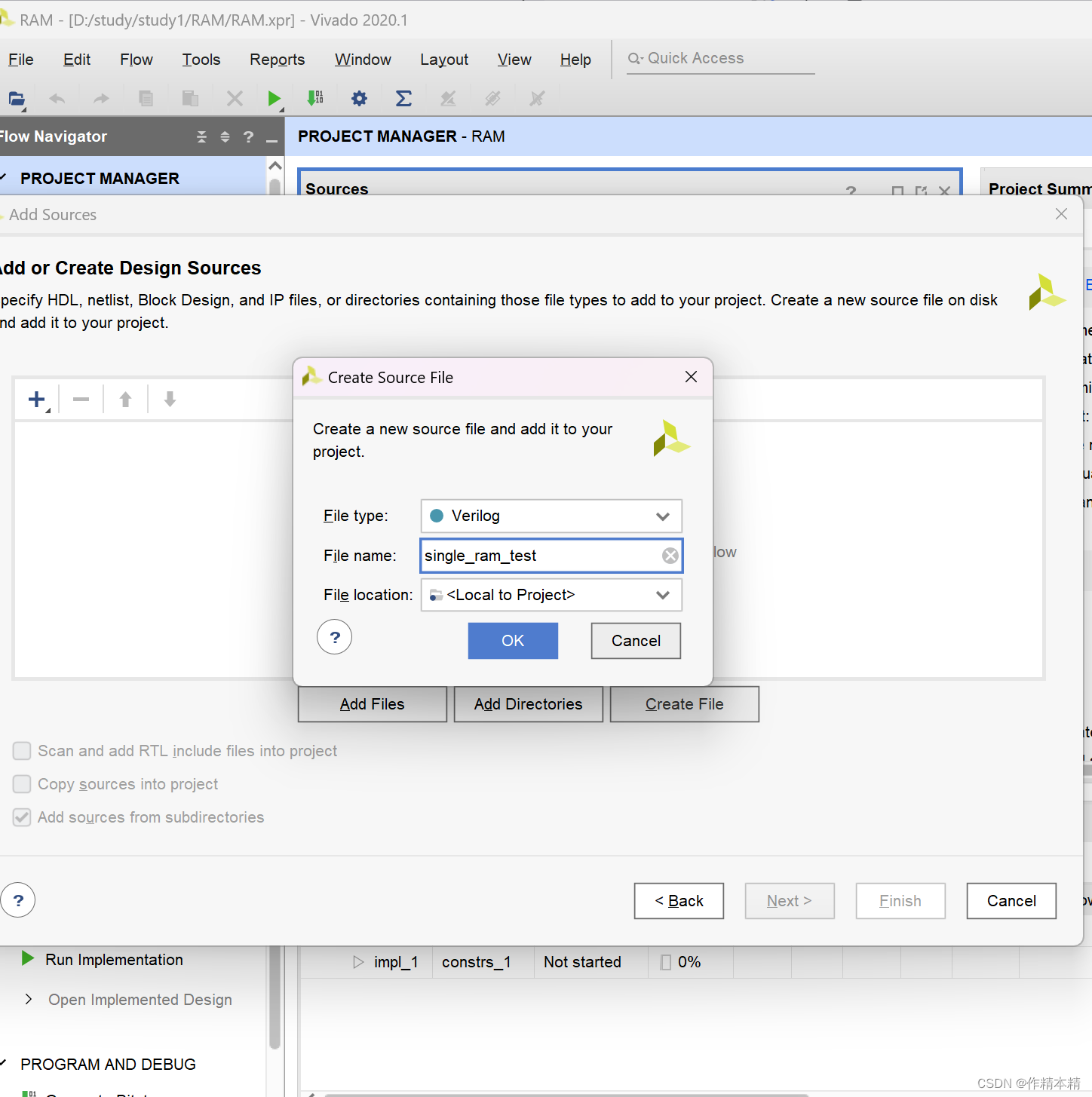

(1)先创建一个工程

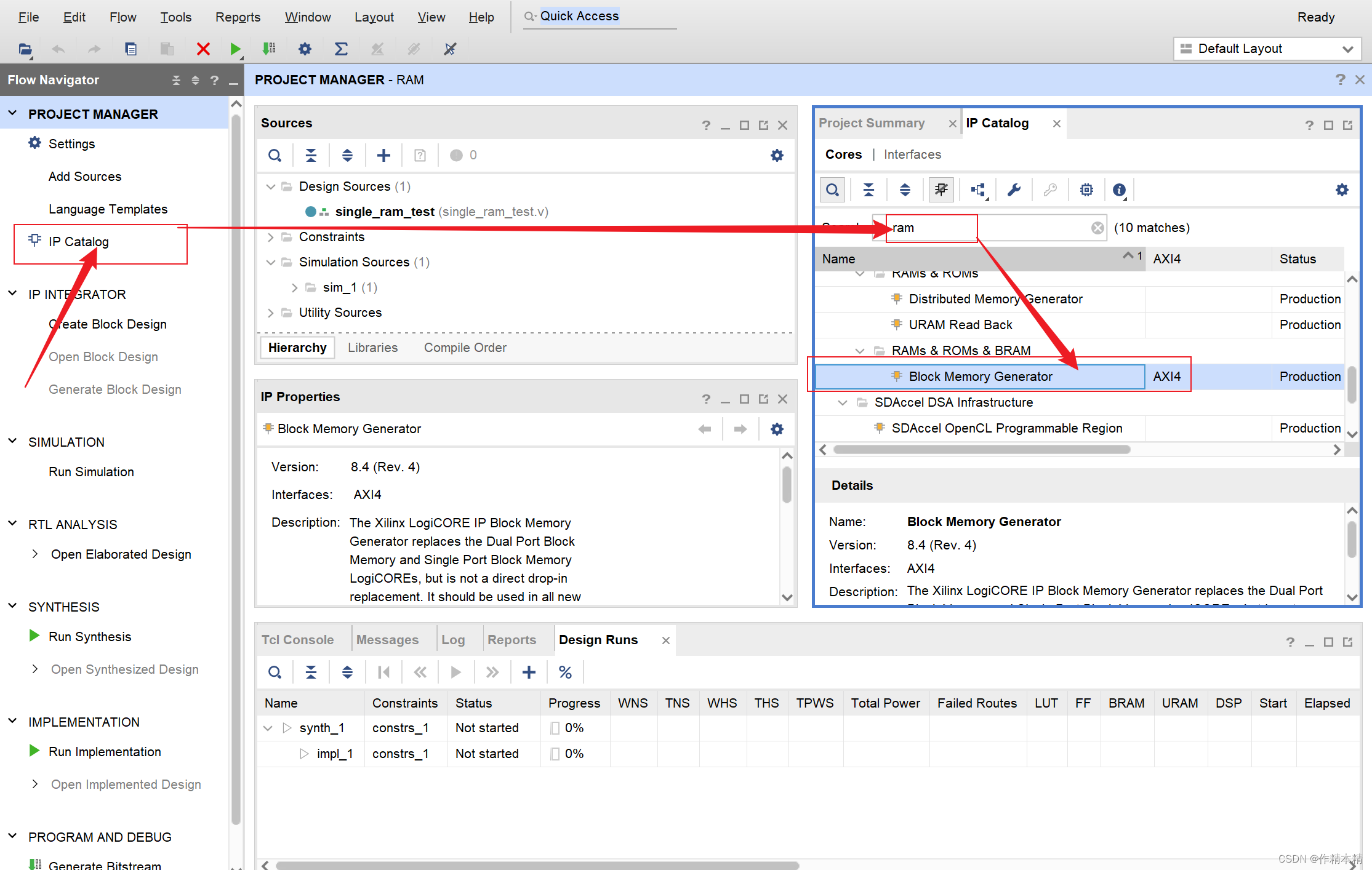

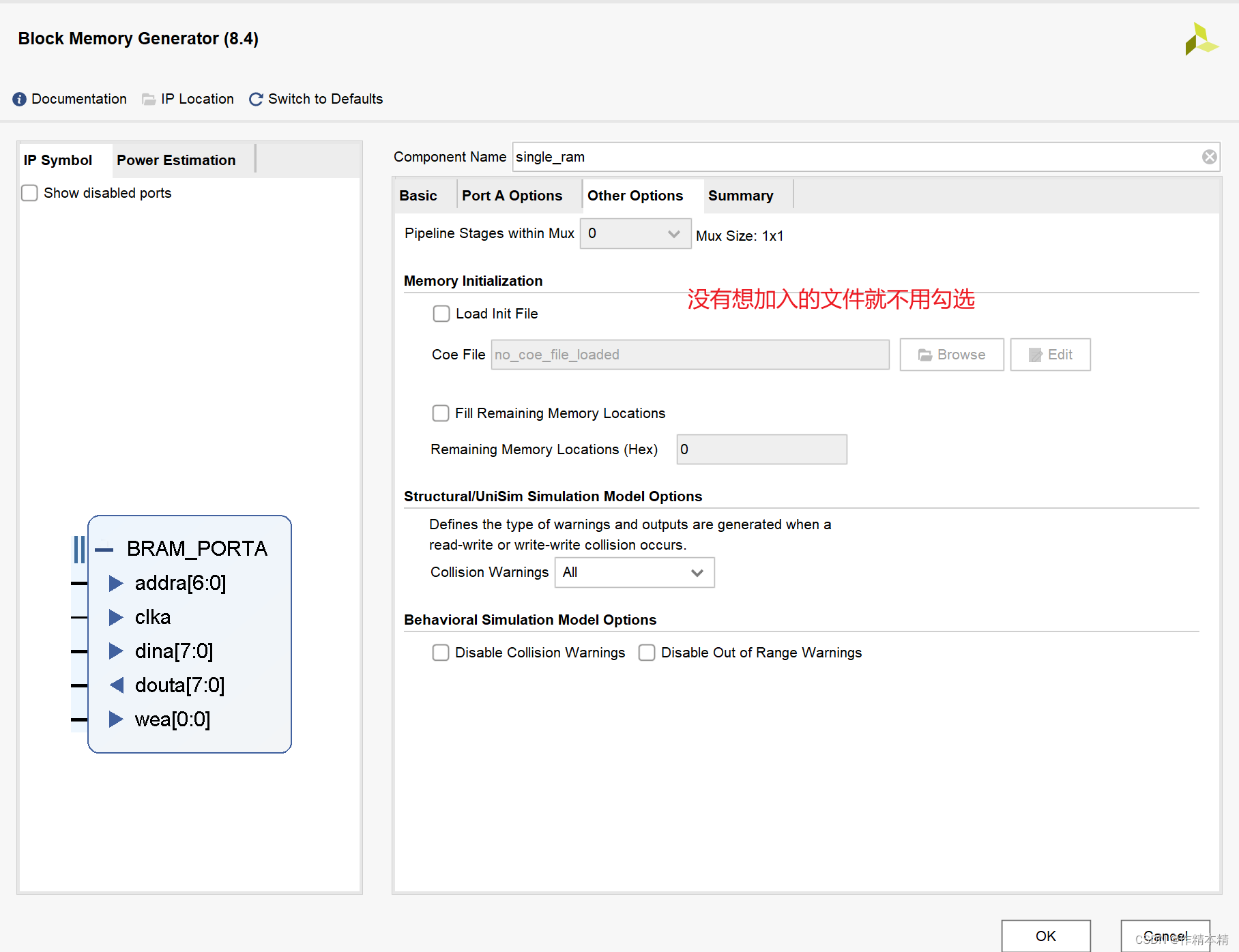

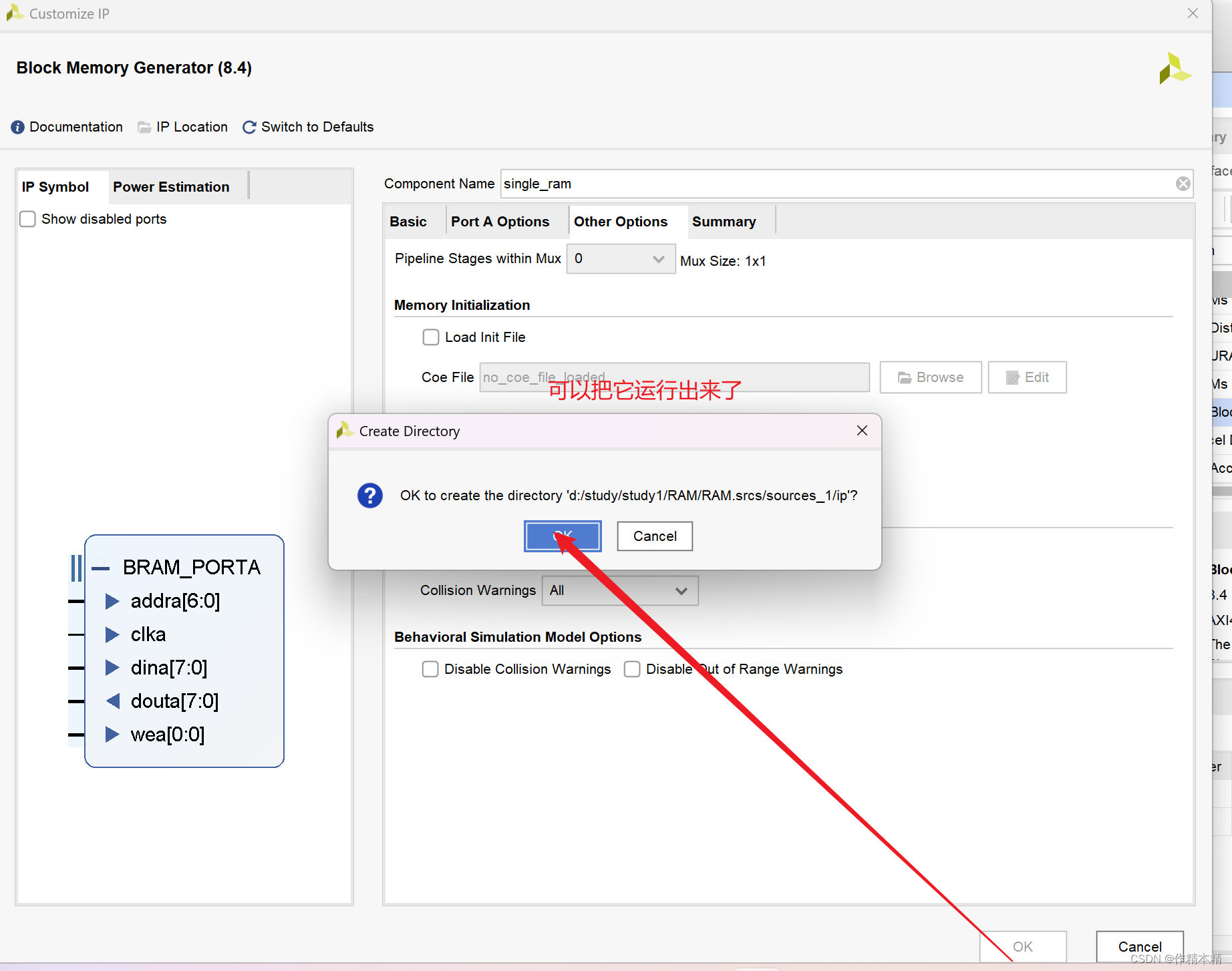

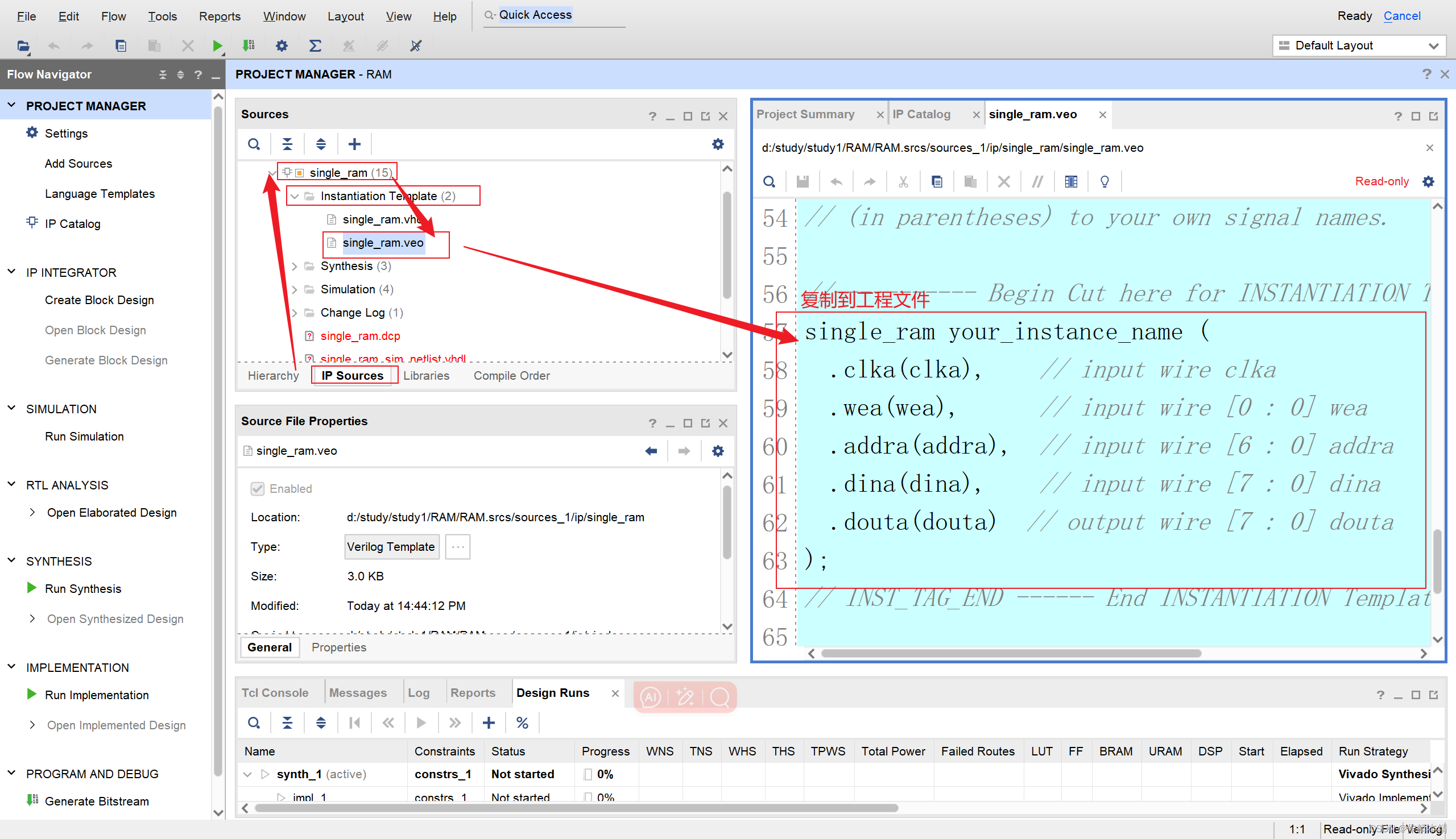

(2)调用IP资源找到RAMs&ROMs&BRAMs,选择其中的块资源

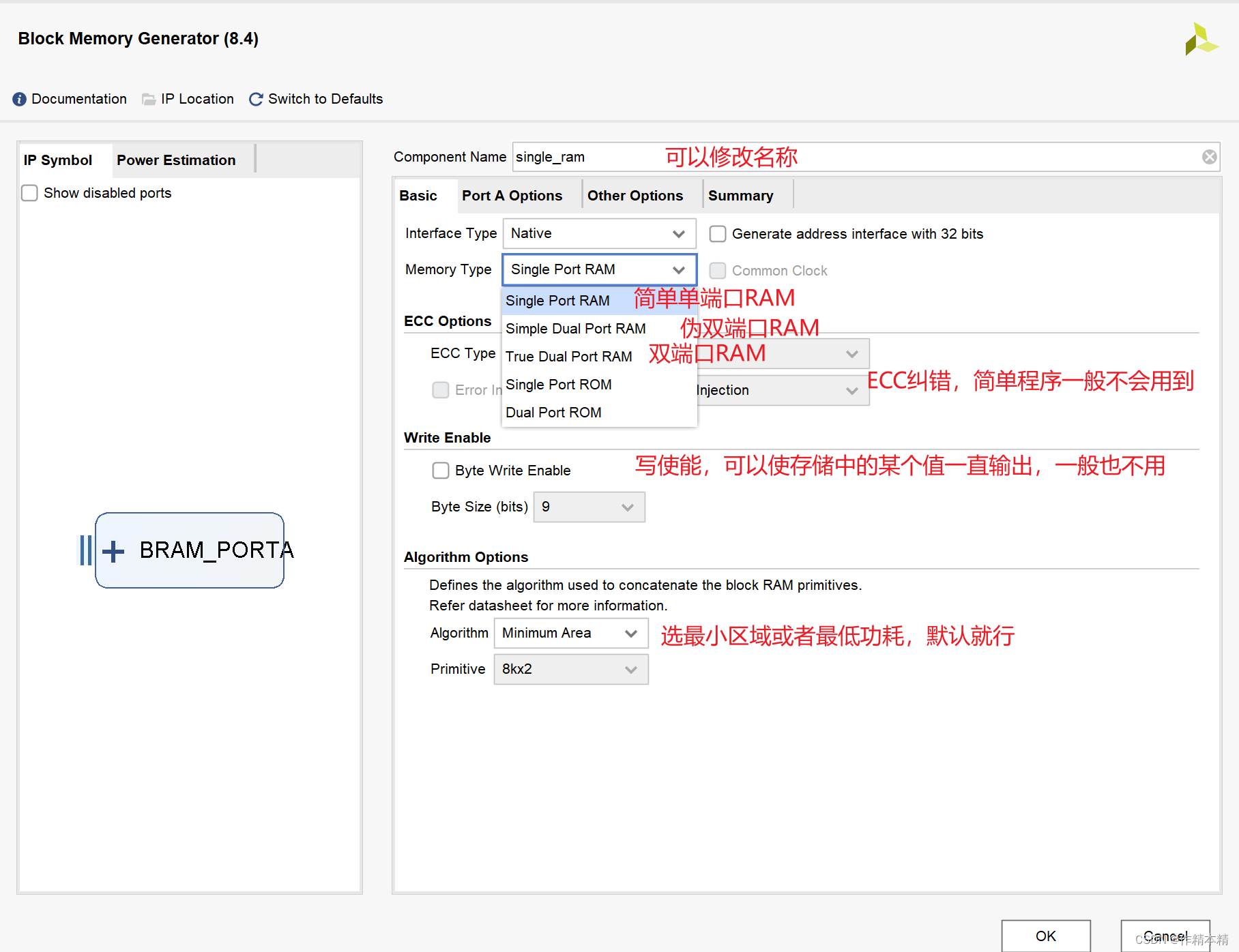

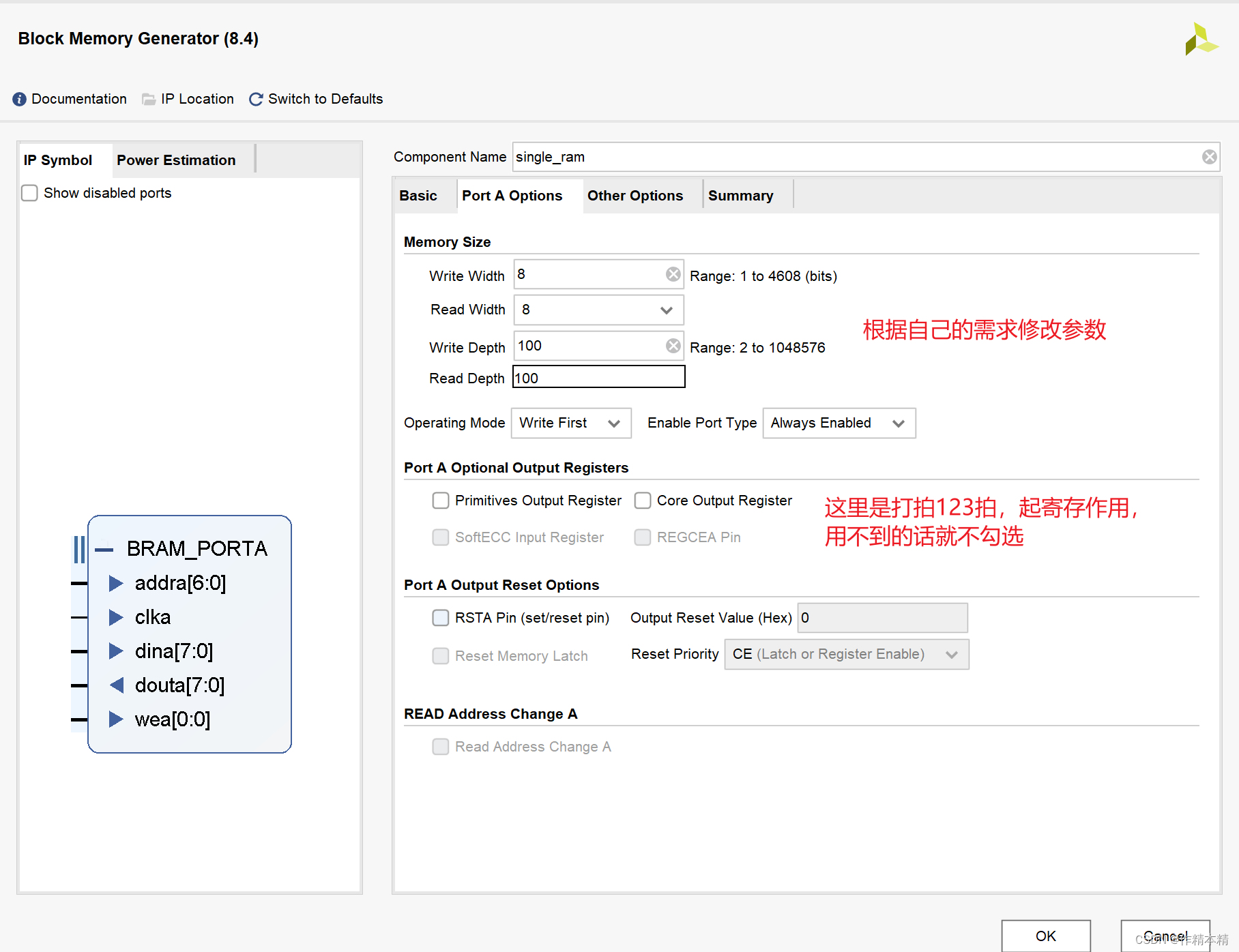

(3)修改配置参数

- `timescale 1ns / 1ps

- //写入0-99的数据,读出偶数

- module single_ram_test(

- input sys_clk ,

- input rst_n ,

- output reg[7:0] ram_out

-

- );

-

- //----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

- wire wea ; //写使能

- assign wea = 1 ;

-

- reg[6:0] addra ;

- reg[7:0] dina ;

- wire[7:0] douta ;

-

- always@(posedge sys_clk)

- if(!rst_n)

- addra <= 0 ;

- else if (addra == 99)

- addra <= 0 ;

- else

- addra <= addra +1 ;

-

- always@(posedge sys_clk )

- if(!rst_n)

- dina <= 0 ;

- else if ( dina == 99 )

- dina <= 0 ;

- else

- dina <= dina +1 ;

-

- always@(posedge sys_clk )

- if(!rst_n)

- ram_out <= 0 ;

- else if ( douta%2 == 0 ) //读出偶数

- ram_out <= douta ;

- else

- ram_out <= 0 ;

-

-

- single_ram your_instance_name (

- .clka(sys_clk), // input wire clka

- .wea(wea), // input wire [0 : 0] wea

- .addra(addra), // input wire [6 : 0] addra

- .dina(dina), // input wire [7 : 0] dina

- .douta(douta) // output wire [7 : 0] douta

- );

- // INST_TAG_END ------ End INSTANTIATION Template ---------

-

-

-

-

- endmodule

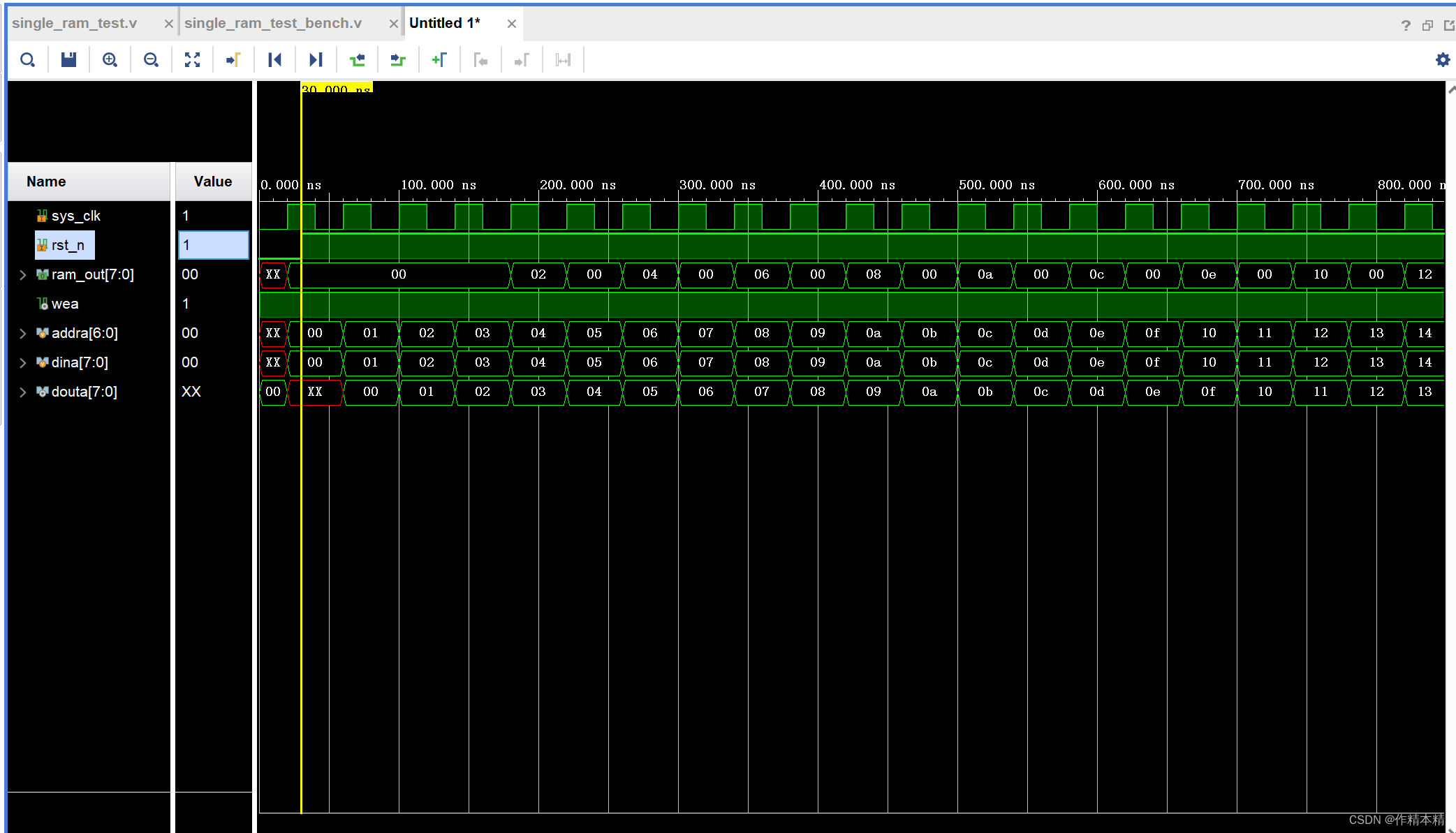

仿真结果:

- `timescale 1ns / 1ps

- module single_ram_test_bench( );

-

- reg sys_clk ;

- reg rst_n ;

- wire[7:0] ram_out ;

-

- initial

- begin

- sys_clk = 0 ;

- rst_n = 0 ;

- #30 rst_n = 1 ;

- end

-

- always #20 sys_clk = ~sys_clk ;

-

-

-

-

- single_ram_test single_ram_test_u1(

- . sys_clk (sys_clk) ,

- . rst_n (rst_n ) ,

- . ram_out (ram_out)

-

- );

-

-

-

- endmodule

本文内容由网友自发贡献,转载请注明出处:https://www.wpsshop.cn/w/小桥流水78/article/detail/762653

推荐阅读

相关标签