- 1Mem0 - 个人 AI 的内存层

- 2数据结构——哈夫曼树_哈夫曼树是否唯一

- 32022网刃杯_spel黑名单

- 4详细教程--将本地项目上传到gitee(使用idea或者git推送)_idea本地新建项目提交到gitee

- 5监控mysql主从状态与延迟_mysql主从延迟监控报警

- 6开源模型应用落地-安全合规篇-用户输入合规性检测(一)_开源合规指标

- 7【LeetCode】刷题工具_leetcode editor

- 8中文Transformer(BERT,GPT,T5等)预训练模型权重_gpt2-chinese-cluecorpussmall

- 9终于碰上torch.nn.Embedding_nn.embedding通过矩阵加载预训练向量

- 10llama3的微调与部署

手把手教你玩转AD9361数字调制解调系列(一) ----纯逻辑实现ASK信号的数字调制解调_ad9361 工作流程

赞

踩

因最近客户需求,用纯PL实现AD9361的数字信号调制解调,于是就把各种数字调制都在AD9361上都实现了一遍。

制作不易,记得三连哦,给我动力,持续更新中!!!

完整工程文件下载:纯逻辑设计AD9361发射ASK 提取码:1567

如果看过我之前的文章的小伙伴,肯定都知道如何通过AD936x Evaluation Software,来生成对AD9361的配置,以及如何在vivado里面调用这个配置,并写入AD9361,接下来将继续延伸我们的设计,来基于纯逻辑配置AD9361的基础上,实现各种数字信号的调制解调。

新来的小伙伴可以看一下我以前的文章:

纯逻辑配置AD9361教程/通过UART串口发送配置文件配置AD9361/通过rom配置AD9361/纯PL配置AD9361_ad9361发送数据代码-CSDN博客

本篇文章将介绍如何通过AD9361发射ASK信号以及纯verilog代码实现和讲解。

一、ASK原理

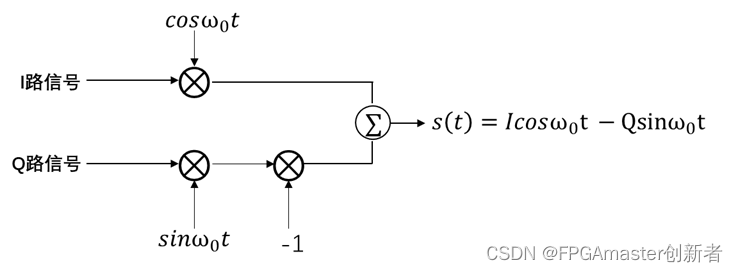

这个系列所有的调制方式都是IQ调制,IQ调制的定义是:“IQ调制就是数据分为两路,分别进行载波调制,两路载波相互正交。I是in-phase(同相), q是 quadrature(正交)”

我们通过下面的示意图介绍IQ调制的过程:

-

调制方法:正交IQ调制。

-

调制类型:2ASK,MASK。

二、FPGA工程代码

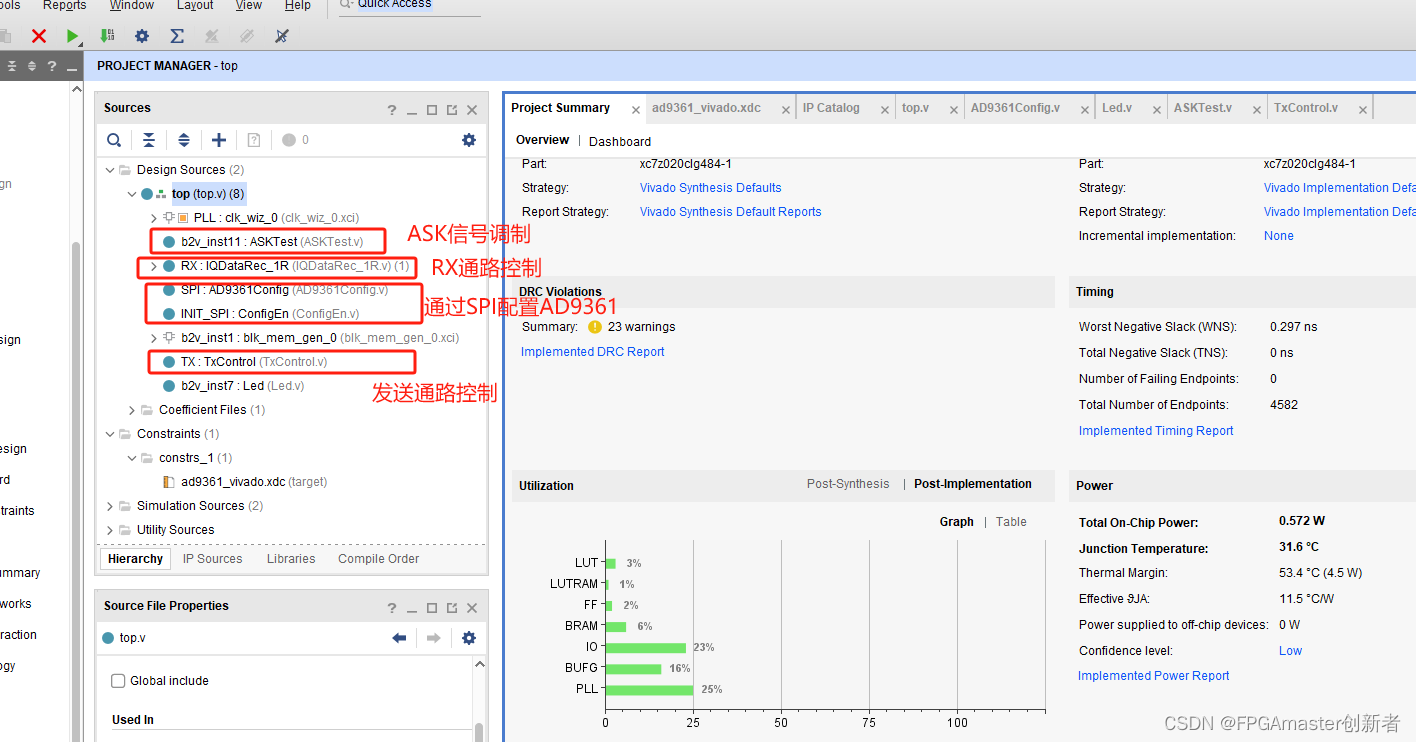

(1)整体工程介绍

具体还是通过以前的架构来实现,只不过单音信号变成了ASK

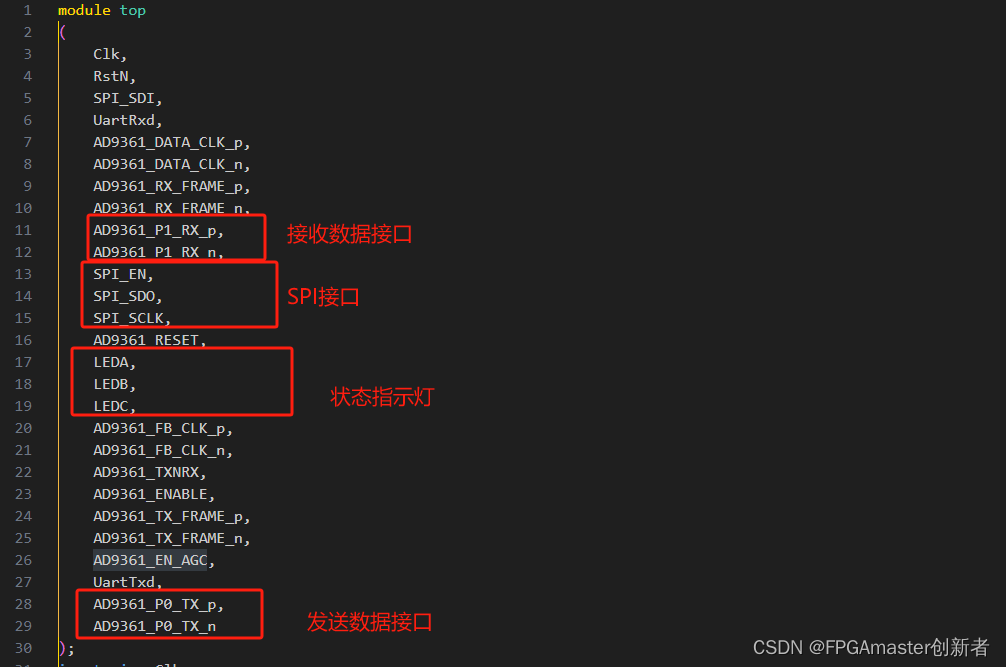

(2)顶层设计 top.v

主要连接各个模块,以及对外的接口定义

部分代码设计:

部分代码设计:

- module top

- (

- Clk,

- RstN,

- SPI_SDI,

- UartRxd,

- AD9361_DATA_CLK_p,

- AD9361_DATA_CLK_n,

- AD9361_RX_FRAME_p,

- AD9361_RX_FRAME_n,

- AD9361_P1_RX_p,

- AD9361_P1_RX_n,

- SPI_EN,

- SPI_SDO,

- SPI_SCLK,

- AD9361_RESET,

- LEDA,

- LEDB,

- LEDC,

- AD9361_FB_CLK_p,

- AD9361_FB_CLK_n,

- AD9361_TXNRX,

- AD9361_ENABLE,

- AD9361_TX_FRAME_p,

- AD9361_TX_FRAME_n,

- AD9361_EN_AGC,

- UartTxd,

- AD9361_P0_TX_p,

- AD9361_P0_TX_n

- );

- input wire Clk;

- input wire RstN;

- input wire SPI_SDI;

- input wire UartRxd;

- input wire AD9361_DATA_CLK_p;

- input wire AD9361_DATA_CLK_n;

- input wire AD9361_RX_FRAME_p;

- input wire AD9361_RX_FRAME_n;

- input wire [5:0] AD9361_P1_RX_p;

- input wire [5:0] AD9361_P1_RX_n;

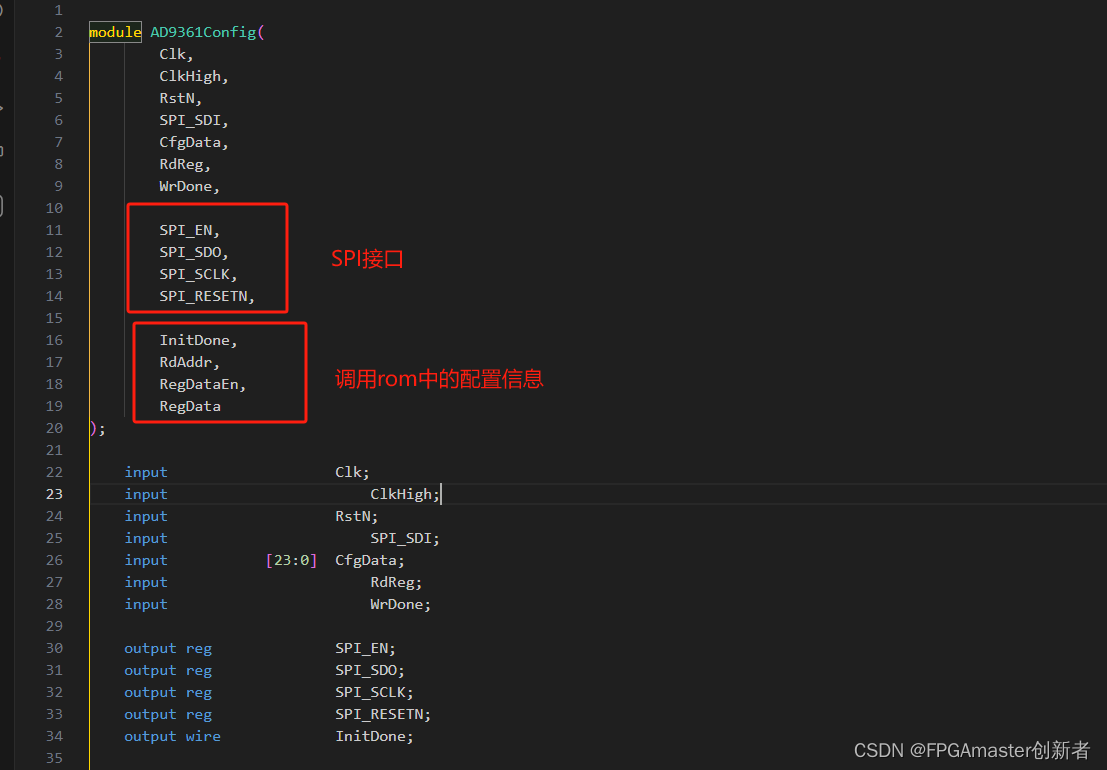

(3)SPI控制9361

通过SPI,把rom中的配置信息配置到AD9361

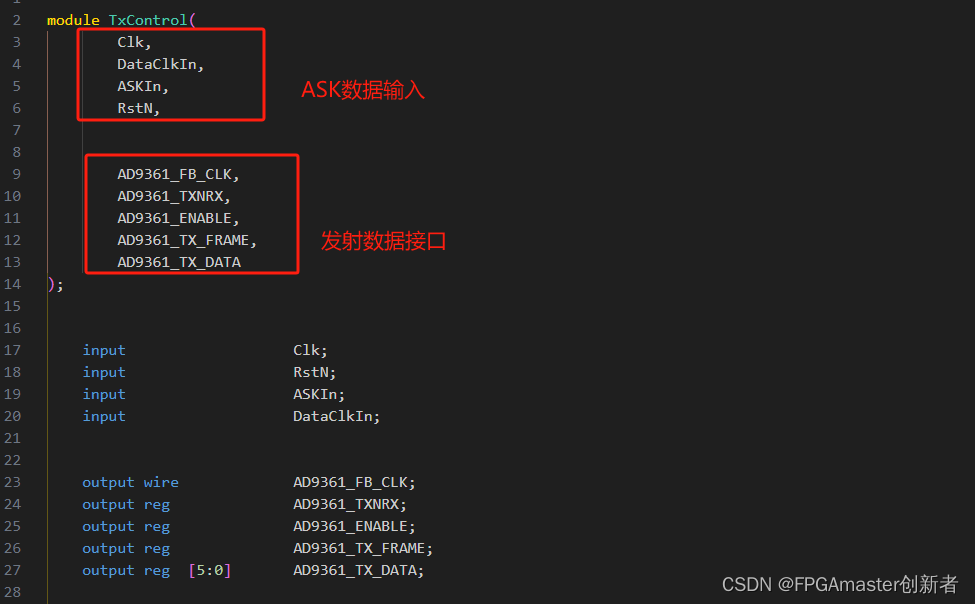

(4)发射接口

主要把ASK数据通过AD9361发射出去

三、测试结果

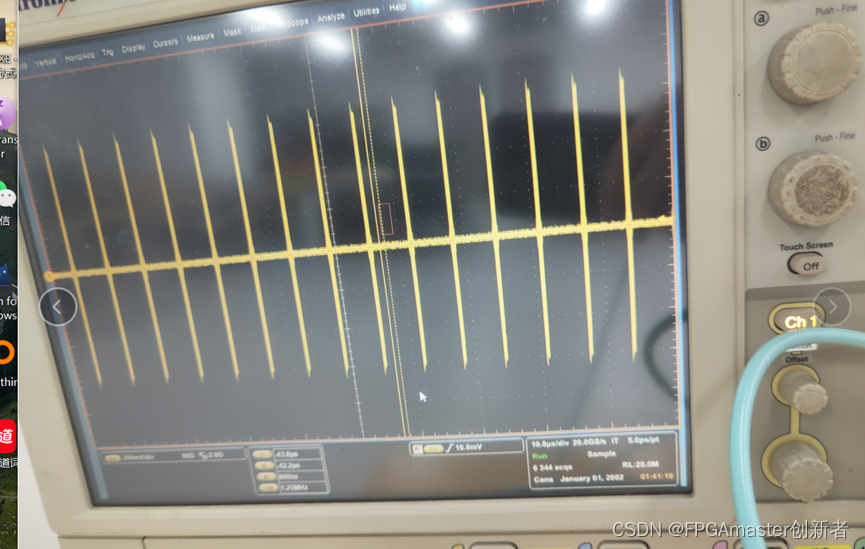

用示波器抓取AD9361发射的端口:

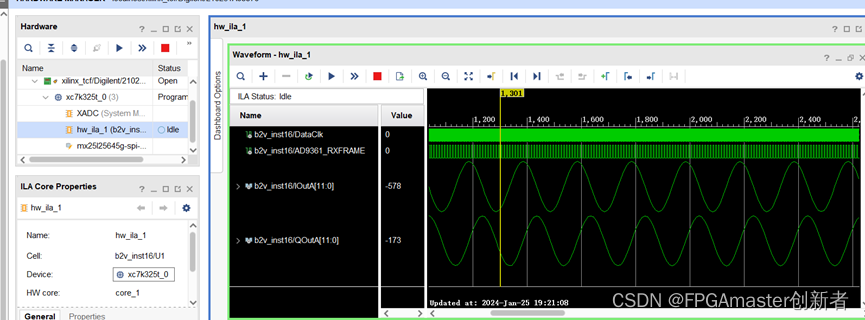

ila查看基带信号:

讲解视频:

纯逻辑实现AD9361发送ASk

自此就已经完成了本次设计内容,下一章更新发射FSK信号!!!

完整工程文件下载:纯逻辑设计AD9361发射ASK 提取码:1567

如果感觉文章对您有用,麻烦三连支持一下,方便下次用到的时候,就可以快速找到我,非常感谢您的支持!!!