- 1R语言合并多个CSV文件:高效的并行读取与合并方法_rstudio 批量导入csv表格并合并

- 2浙大计算机就业方向,浙大四大 "王牌专业",毕业后工作待遇高,发展前景非常广阔...

- 3NLP 分类算法_nlp数学方面的算法怎么写

- 4基于EasyDL搭建音频在线实时分类系统_easydl 模型部署

- 5GO语言,区块链私钥公钥生成以及钱包地址生成_go 区块链的钱包怎么生成

- 6API接口漏洞利用及防御_api接口未授权访问漏洞

- 7基于深度学习的图像识别技术研究综述_基于深度学习的番茄目标识别技术研究进展

- 8为什么需要代理ip_为什么要用代理ip

- 9AI互动课正当时,即构AI课堂2.0助推在线教育创新升级_ai课堂教学

- 10heic图片如何转为jpg格式_c# opencvsharp heic 图片转jpg

AD9361-----启动状态机指南_ad9361 alert

赞

踩

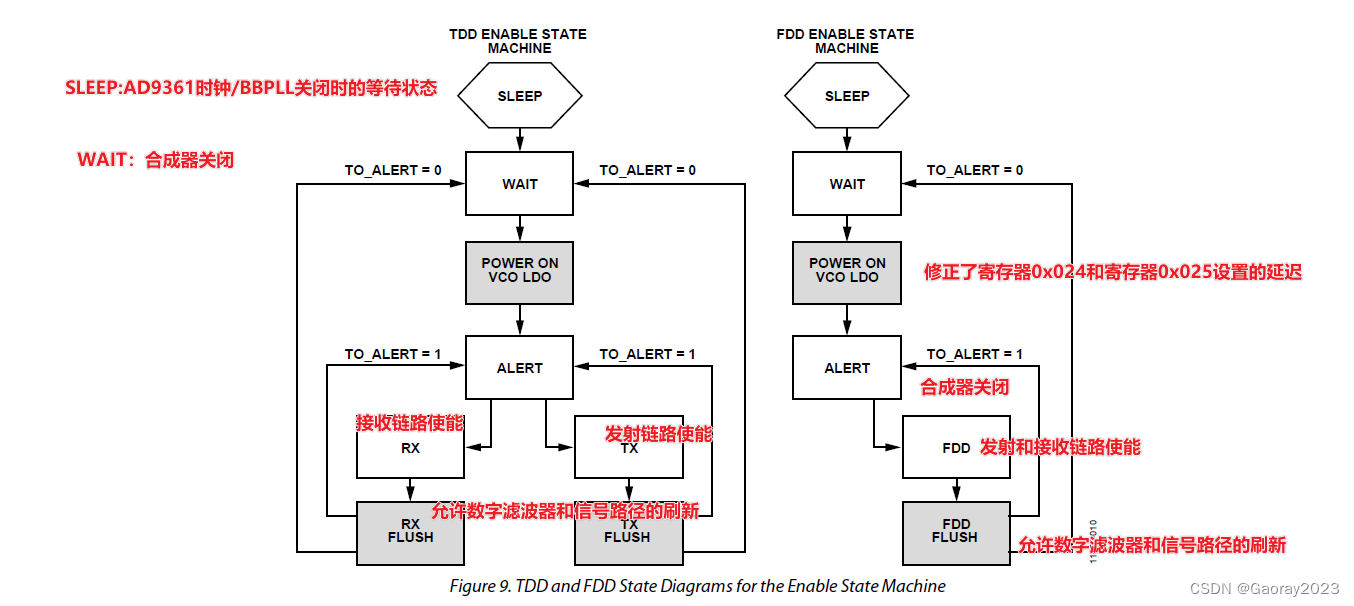

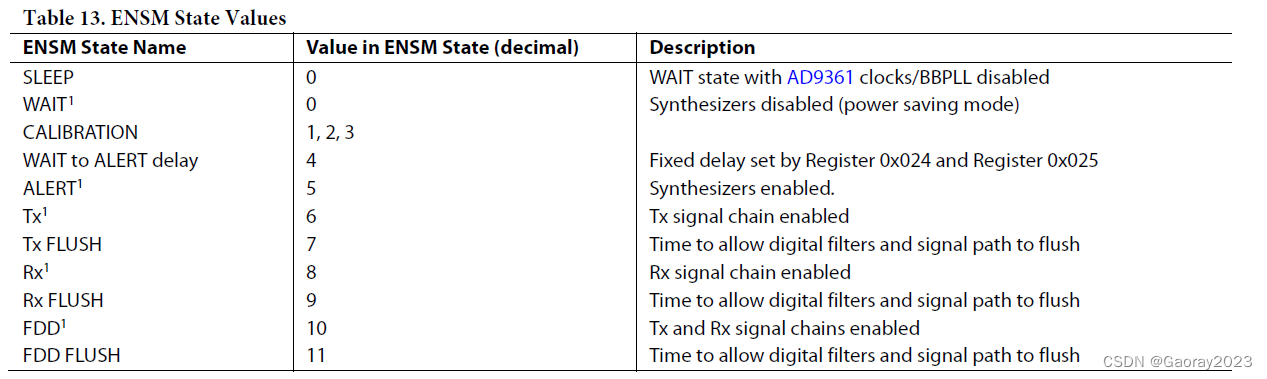

1.概述

AD9361收发器包括一个使能状态机(ENSM),允许实时控制设备的当前状态。ENSM有两种可能的控制方法——SPI控制和引脚控制。通过写入SPI寄存器来异步地控制ENSM,将当前状态推进到下一个状态。ENABLE和TXNRX引脚允许实时控制当前状态。ENSM还允许TDD或FDD操作。ad9361_set_en_state_machine_mode函数配置ENSM。

图9中显示的灰色状态不需要用户控制,并将在设定的时间后自动过渡到下一个状态。

TO_ALERT信号是ENSM配置1寄存器中的一个设置。

要进入WAIT状态,需在Rx或Tx状态下清除TO_ALERT位。

在该配置下,当从Rx、Tx或FDD状态退出时,ENSM将转换到WAIT状态。

如果该位被设置,则ENSM将转换到ALERT状态。

SLEEP状态是带有AD9361时钟禁用的WAIT状态。

要进入睡眠状态,首先转换到WAIT状态,然后在BPLL寄存器中禁用AD9361时钟。

使能状态机

操作模式

ENSM可以通过SPI写或ENABLE/TXNRX引脚进行控制。由于SPI_CLK可以来自不同的时钟参考,并且仍然可以正常工作,因此SPI控制被认为是异步于DATA_CLK的。

当不需要实时控制合成器时,建议使用SPI控制ENSM方法。只要BBP能够准确执行定时SPI写入,SPI控制就可以用于实时控制。

如果BBP具有额外的控制输出可以实时控制,允许简单的两线接口控制AD9361设备的状态,则建议使用ENABLE/TXNRX引脚控制方法。

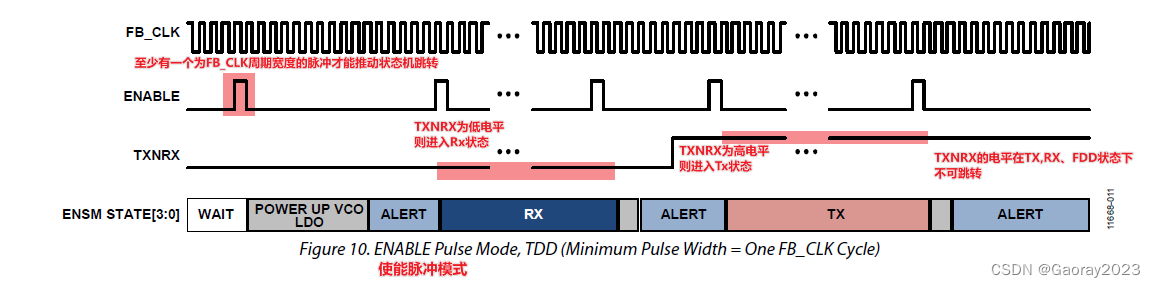

ENABLE引脚可以由脉冲(在AD9361内部检测到的边沿)或电平驱动,以将ENSM的当前状态推进到下一个状态。如果在ENABLE引脚上使用脉冲,则脉冲宽度必须至少为一个FB_CLK周期。在电平模式下,ENABLE和TXNRX引脚也在AD9361中检测到边沿,并且必须满足一个FB_CLK周期的最小脉冲宽度要求。

SPI控制

SPI控制默认情况下是禁用的,可以在ENSM配置1寄存器中启用。一旦进入ALERT状态,AD9361会启用其用于发射机和接收机的射频合成器。如果由于某种原因合成器没有正确校准,则ENSM将无法将状态转换为Rx或Tx状态。此功能保护AD9361在合成器未正确校准时不会传输或接收数据,从而保护了无线频谱。

一旦进入ALERT状态,并且RFPLL正确校准,ENSM就准备好进入Rx、Tx或FDD状态。要从ALERT转换到Rx,请设置Force Rx On位。要返回到ALERT或WAIT状态,请清除该位。要从ALERT转换到Tx或FDD,请设置Force Tx On位。要返回到ALERT或WAIT状态,请清除该位。在FDD模式下,Force Rx On位被忽略。在TDD模式下,在Rx和Tx状态之间,ENSM必须转换到ALERT状态。ENSM不能直接从Rx转换到Tx,或者从Tx直接转换到Rx。

在从WAIT状态发送Force Alert State位后,要等待ENSM通过ENSM State 4的时间后再发送另一个命令。State 4完成所需的时间取决于写入Rx和Tx Load Synth Delay寄存器的时间设置。此延迟为2微秒。

在发送SPI写命令退出Rx或Tx状态后,要在发送另一个ENSM SPI命令之前,允许六个ADC_CLK/64时钟周期的冲刷时间。如果在中间ENSM状态期间接收到SPI命令,则该命令将被忽略。

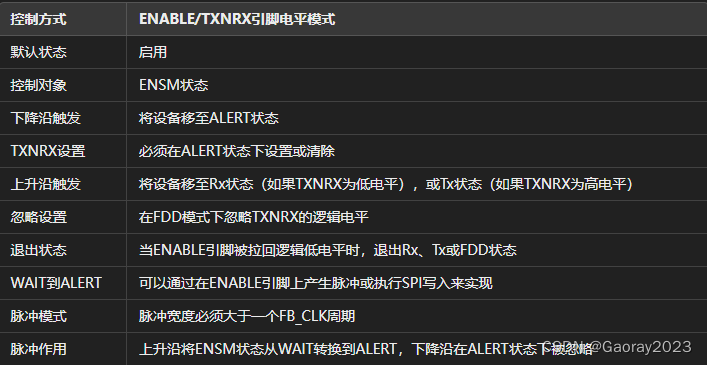

使能/发射控制

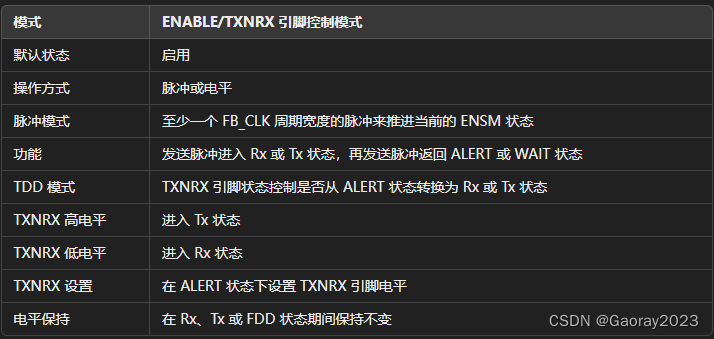

ENABLE/TXNRX引脚控制模式默认情况下是启用的。ENABLE引脚可以使用脉冲或电平将ENSM状态转换到下一个状态。

在脉冲模式下

必须有一个至少为一个FB_CLK周期宽度的脉冲才能推进当前的ENSM状态。BBP发送一个ENABLE脉冲以进入Rx或Tx状态,然后在需要返回到ALERT或WAIT状态时发送另一个脉冲。

在TDD模式下

TXNRX引脚的状态控制AD9361是否从ALERT状态转换为Rx或Tx状态。

如果TXNRX为高电平,则设备将进入Tx状态。

如果TXNRX为低电平,则设备将进入Rx状态。

TXNRX引脚的电平应在ALERT状态下设置。

TXNRX的逻辑电平在Rx、Tx或FDD状态期间不得更改。

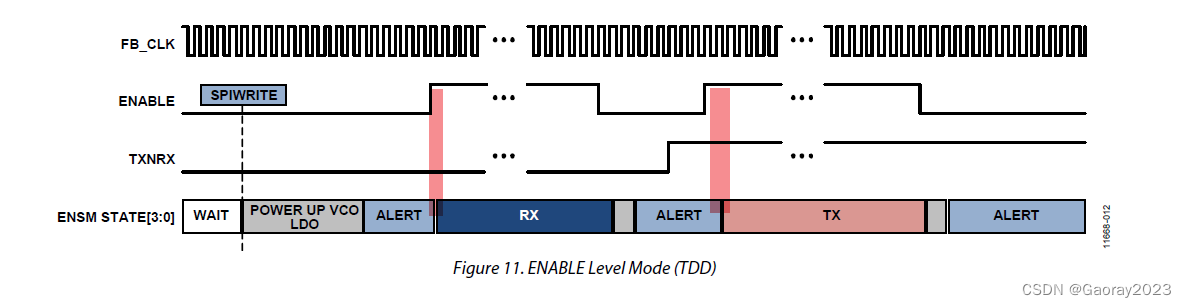

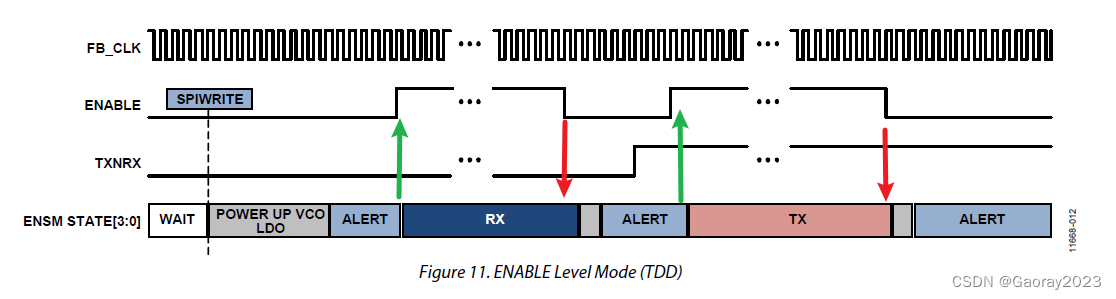

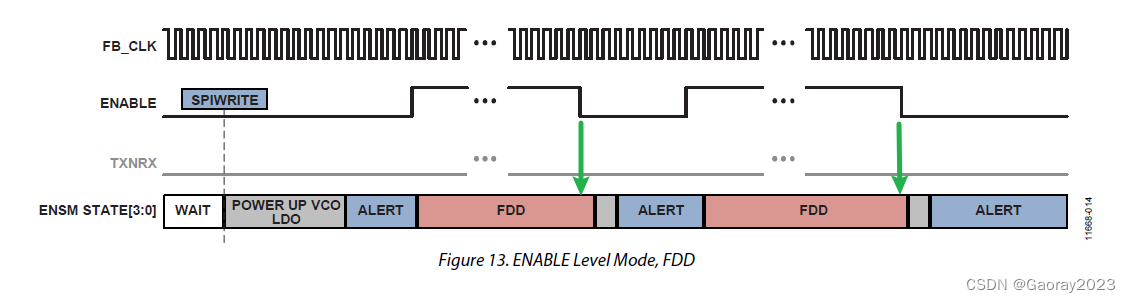

电平模式下

ENABLE引脚电平控制ENSM状态。

ENABLE引脚的下降沿将AD9361设备移至ALERT状态。

在ALERT状态下,必须设置或清除TXNRX。

ENABLE引脚的上升沿将AD9361设备移至Rx状态(如果TXNRX为低电平),或Tx状态(如果TXNRX为高电平)。

FDD模式下

忽略TXNRX的逻辑电平。

当ENABLE引脚被拉回逻辑低电平时,ENSM将退出Rx、Tx或FDD状态。

如果To Alert位被清除,则设备将从Rx、Tx或FDD转换到WAIT状态。

在电平模式下,要从WAIT转换到ALERT状态,BBP可以在ENABLE引脚上产生一个脉冲,或者执行SPI写入到Force Alert State位。

如果使用ENABLE脉冲,它的脉冲宽度必须大于一个FB_CLK周期。

ENABLE脉冲的上升沿将ENSM状态从WAIT转换到ALERT。

在ALERT状态下,忽略ENABLE脉冲的下降沿。

从WAIT状态转换到ALERT状态时,必须等待第4状态完成后才能发送另一个ENABLE脉冲。等待的时间取决于Rx和Tx的Load Synth Delay。此外,在Rx、Tx和FDD状态之后,每个相应的FLUSH状态都要允许六个ADC_CLK/64时钟周期的时间来完成。

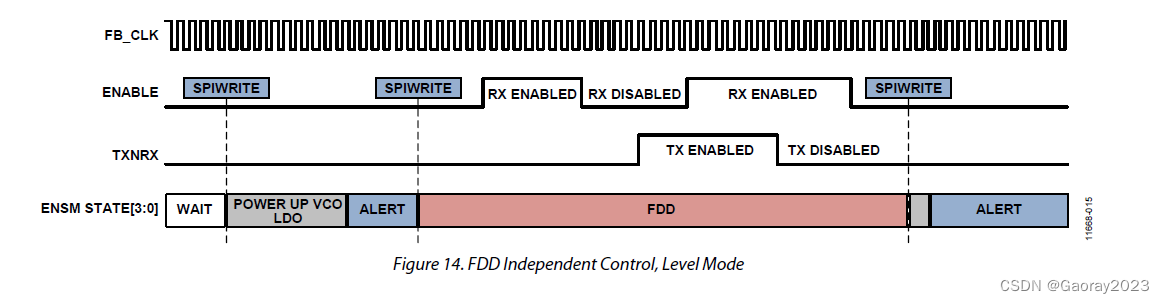

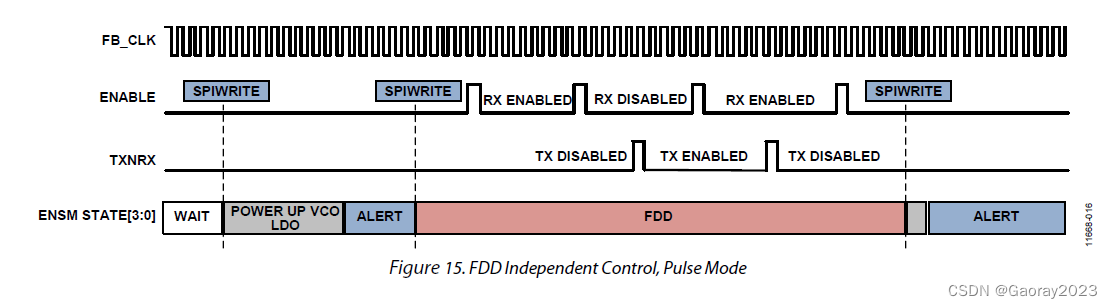

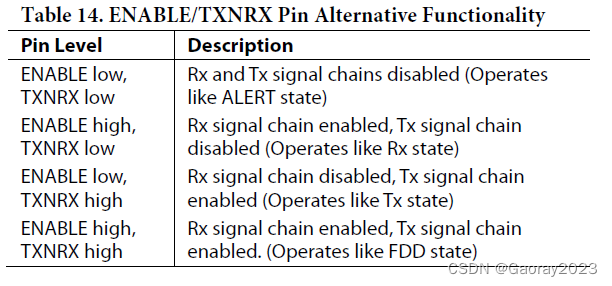

FDD独立控制

在FDD模式下,FDD独立控制选项允许接收链路和发送链路独立启用。通过设置FDD外部控制使能位(0x015[D7])来启用此模式。请注意,必须使用SPI写入将ENSM移至FDD状态。然后,ENABLE和TXNRX引脚被内部重新映射为Force Rx On和Force Tx On。一旦进入FDD状态,允许使用表14中列出的控制组合。

请注意,由于ENSM始终保持在FDD状态,因此它永远不会转换到FDD FLUSH状态。因此,BBP必须在启用接收链路后允许足够的时间进行数字滤波器的刷新,并在发送Tx数据后允许足够的时间,以便Tx完成传输后再禁用相应的信号链路。如果Tx_FRAME保持低电平,AD9361中的数据端口将强制将零输入到Tx数据路径中。请注意,在脉冲模式下,BBP应该在ENABLE引脚上发送脉冲来启用/禁用Rx信号链路。在TXNRX引脚上发送的脉冲将启用/禁用Tx信号链路。

当使用SPI写入从ALERT转换到FDD状态时,直到收到第一个脉冲之前,Rx和Tx信号链路都处于禁用状态。脉冲的最小脉冲宽度应为一个FB_CLK周期。没有定义最大脉冲宽度;该脉冲被边沿检测,并在内部生成一个单周期宽的脉冲。

使能状态机和RF压控振荡器校准

ENSM控制着一个内部信号,告诉Rx和Tx合成器何时进行校准。在FDD中,当从WAIT转换到ALERT时,以及写入整数RF频率字时,Rx和Tx合成器都会进行校准。否则,合成器保持通电并保持锁定状态。

与FDD类似,在TDD中,当从WAIT转换到ALERT时,启用的合成器(取决于TXNRX逻辑电平)将进行校准。在ALERT、Rx或Tx状态时,启用的合成器(取决于TXNRX逻辑电平)将在SPI寄存器映射中写入整数频率字时进行校准。

在TDD中,合成器不会始终保持锁定状态。在Rx状态下,Tx合成器被禁用以节省功耗。在Tx状态下,Rx合成器被禁用。在TDD中,ENSM将在TXNRX状态更改后生成信号以重新校准正确的VCO。此信号将在Rx或Tx Load Synth Delay延迟完成后,从ENSM发出到合成器。

在设备进入ALERT状态时尽快更改TXNRX的状态非常重要,以便为选定的合成器在进入Rx或Tx状态之前提供校准时间。