- 1【机器学习】Qwen2大模型原理、训练及推理部署实战

- 2全网最全的鸿蒙源码结构分析(附自制4张架构图)_开源鸿蒙源码_鸿蒙架构图

- 3网络协议与标准

- 4PM到SM,个人蜕变&组织转型_pmo sm

- 5Python Spark MLlib之逻辑回归_stumbleupon evergreen数据集

- 6基于SpringBoot+Vue的大学生志愿者管理系统(源码+文档+部署+讲解_vue志愿者系统数据库设计

- 7Unity 自定义房间布局系统 设计与实现一个灵活的房间放置系统 ——自定义房间区域功能_自定义空间布局

- 8【MySQL】(基础篇十二) —— 子查询

- 9git报错: Another git process seems to be running in this repository

- 10上位机图像处理和嵌入式模块部署(h750和市场上的开发板)

xilinx管脚差分端接_Xilinx 7系列SelectIO结构之IO标准和端接匹配(三)

赞

踩

引言:SSTL电平标准一般用于DDR SDRAM存储器,在FPGA存储器外设接口中经常使用该电平标准。本文我们介绍伪差分SSTL电平标准相关的端接匹配拓扑结构,具体包括:

- SSTL电平标准概述

- SSTL电平标准可用I/O bank类型

- SSTL端接拓扑结构

1.SSTL电平标准概述

1.8V(SSTL18)、1.5V(SSTL15)和1.35V(SSTL135) I/O 标准用于一般目的存储器总线。本节讨论端接技术举例,通过对PCB拓扑结构的信号完整性分析(包括存储器器件、布局布线和传输线阻抗),确定给定存储接口最佳端接方案。Xilinx为所有I/O标准提供了IBIS模型文件和加密的HSPICE模型文件。7系列FPGA支持单端和差分SSTL标准。差分SSTL使用真差分放大器输入缓冲和互补推拉输出缓冲。三态DCI(T_DCI)标准是HP I/O banks存储器接口优选的标准。推荐在HR I/O banks实现接口设计时使用IN_TERM属性。

7系列FPGA为所有存储器接口相关标准,HSTL、SSTL、HSUL和MOBILE_DDR,新增slew rate可选功能。尽管默认的设置为slow slew rate,对于大部分快速接口频率,fast slew rate是优选的,然而,是否选择fast slew rate,需要通过信号完整性分析决定。

1.1 SSTL18标准

SSTL18 I/O标准用于DDR2 SDRAM存储器接口。Class I类型只能用于单向拓扑,不支持双向接口,Class II可以用于单向和双向信号。对于某些拓扑(如短的传输线和点对点接口),Class I类型可以减少反射和更好的信号完整性。

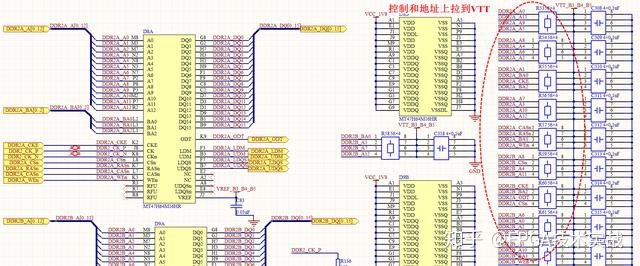

图1、使用SSTL18_II的DDR2电路图

SSTL18 Class I和Class II在HR和HP banks都是可用的,HP banks提供DCI和T_DCI端接功能,T_DCI只能用于双向I/O。HR banks提供IN_TERM选项用于内部并行分立端接电阻。尽管任何新设计的最佳驱动和端接方案都是通过仔细的信号完整性分析确定的,但最初的考虑应包括:

-

<