热门标签

热门文章

- 1RabbitMQ整合 SpringCloud_@resource(name="${message.type.name}") private imq

- 2mockito_@injectmocks 会连接数据库吗

- 3阿里云天池 天池实验室DSW探索者版 免费GPU 天池notebook教程_data science workshop

- 4低代码让传统软件开发土掉渣了_为什么用低代码做出来的产品很快就淘汰了

- 5目标检测(任务概述、机器学习时代的方法、深度学习时代的目标检测模型)_目标检测任务

- 6Java实现学生信息管理系统(用Java实现数据库的增删改查等功能的操作)_java学生信息管理系统筛选信息

- 7#NLP|TextRank #使用 TextRank 算法为文本生成关键字和摘要_利用textrank、指针生成网络等进行文本摘要生成,并对生成摘要进行质量评测,计算其

- 8【配送路径规划】基于matlab停靠点的NIA算法单卡车协同单无人机多客户外卖配送路径规划(目标函数:最短时间)【含Matlab源码 3987期】_无人机配送线路规划

- 9用python爬github上星级排名前列的项目报错AttributeError: 'NoneType' object has no attribute 'decode'

- 10UE中UMG控件属性(一)_umg控件可访问性

当前位置: article > 正文

Quartus新建一个工程流程+QuartusII18.0l与Modelsim10.5版本的联合仿真案例成功:3-8通路三态门输出_quartus ii工程文件建立流程

作者:木道寻08 | 2024-07-05 15:35:52

赞

踩

quartus ii工程文件建立流程

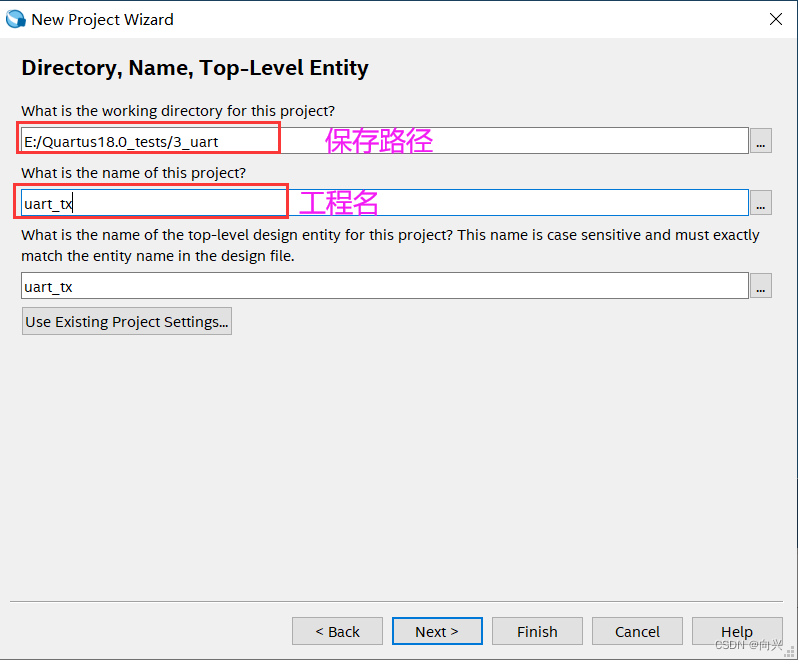

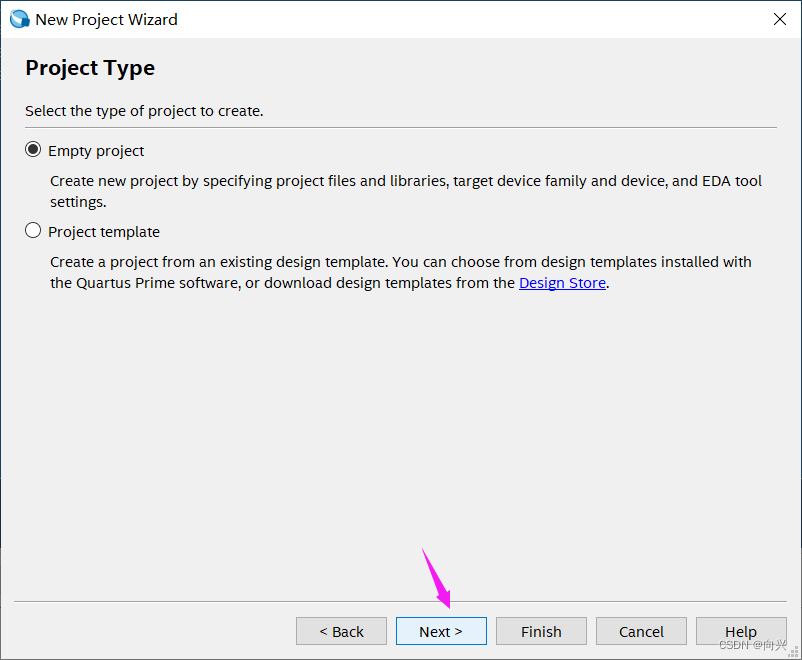

1,QuartusII新建一个工程的流程

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

(9)

(10)

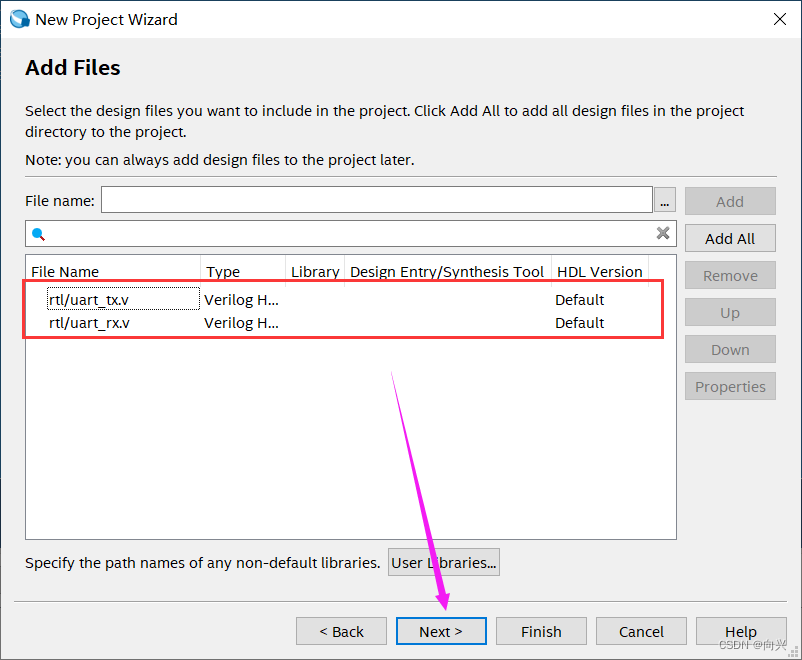

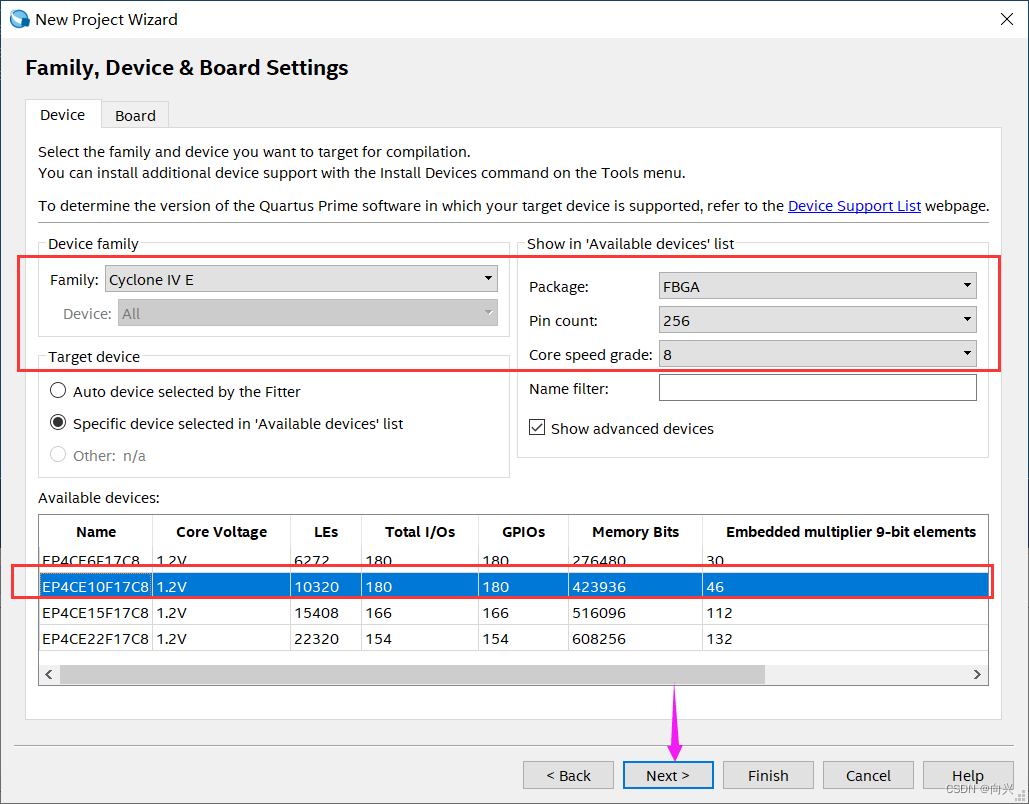

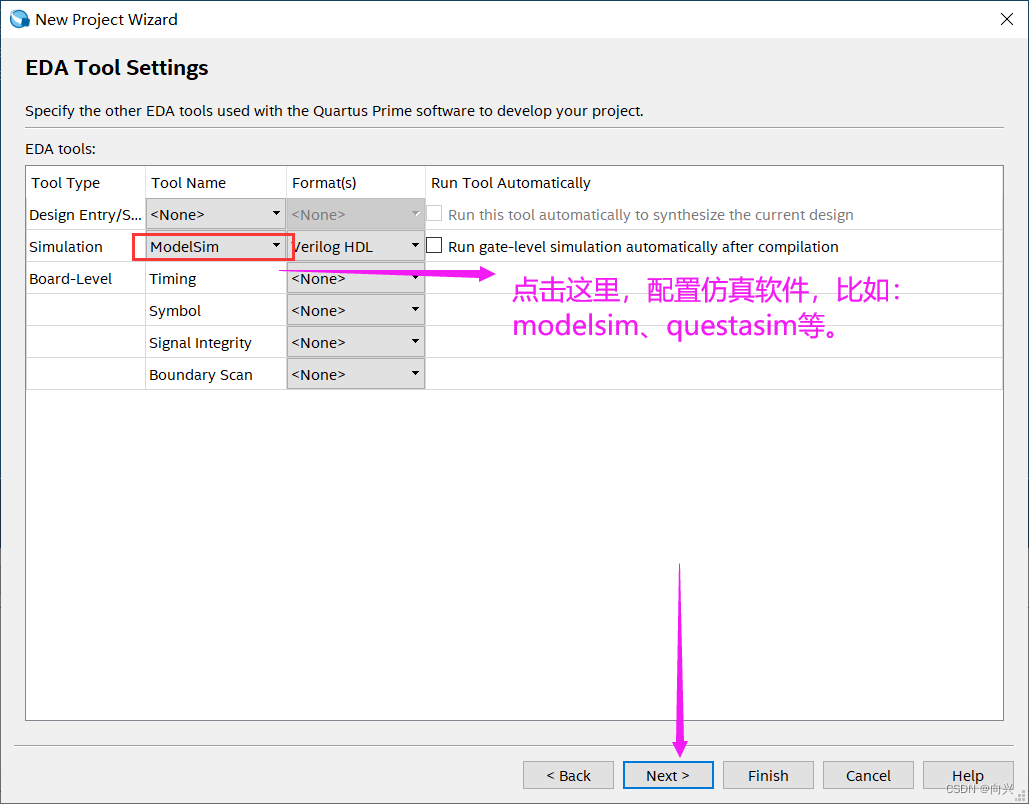

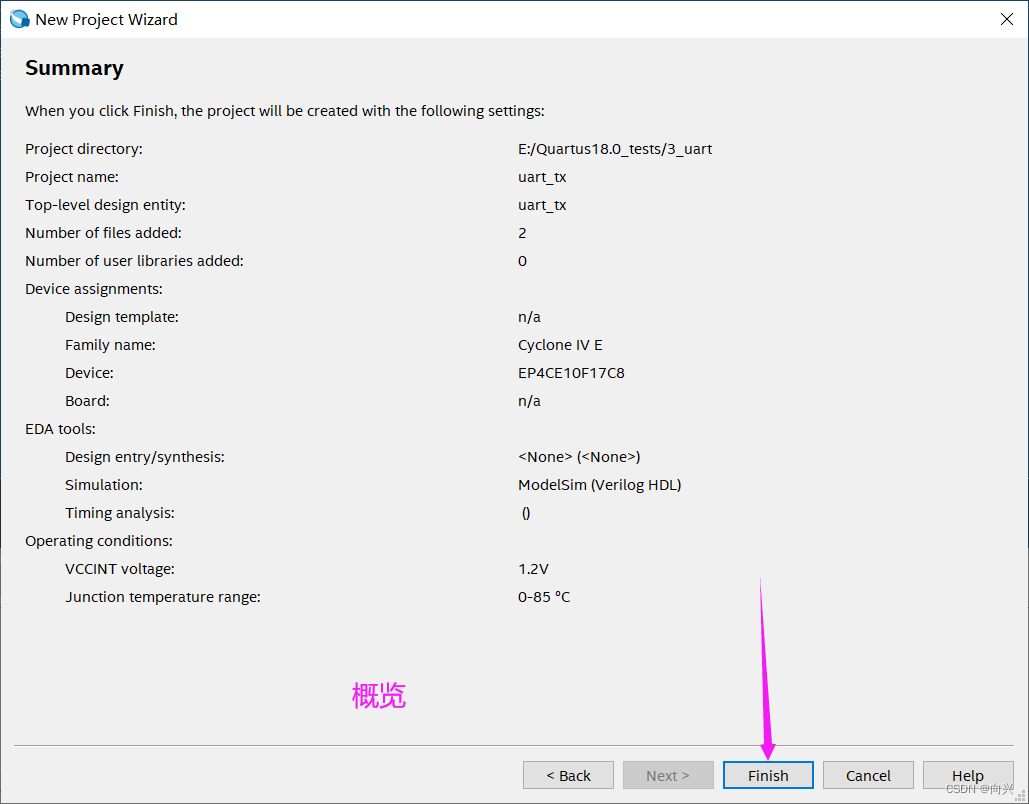

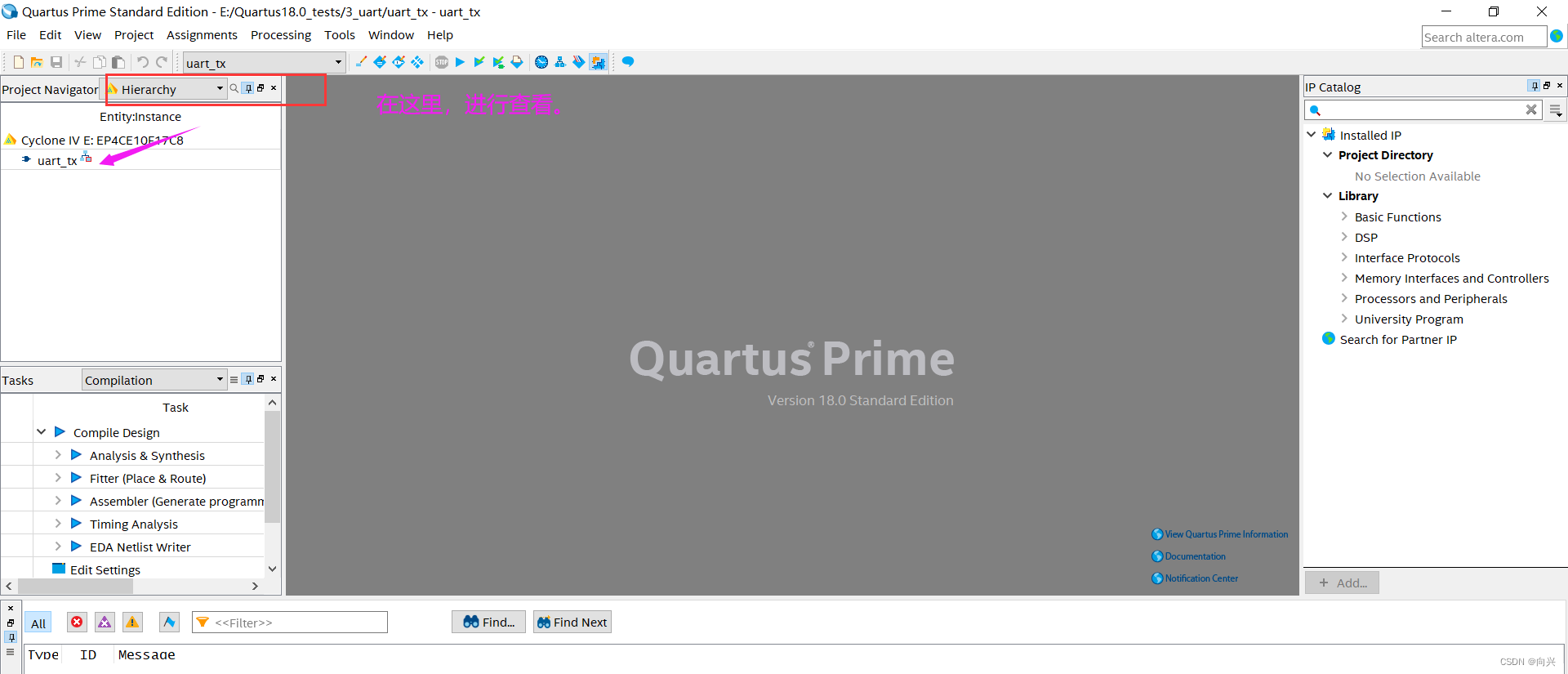

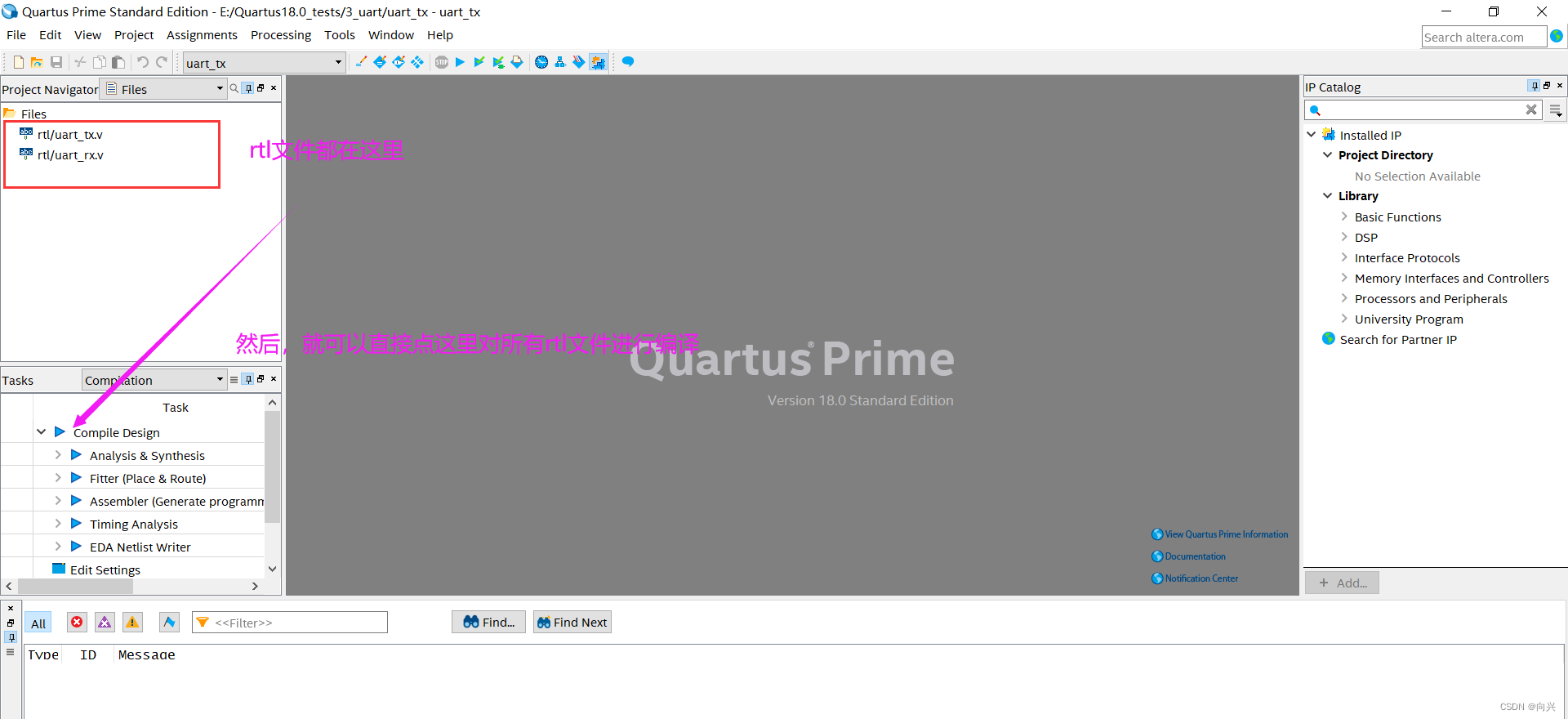

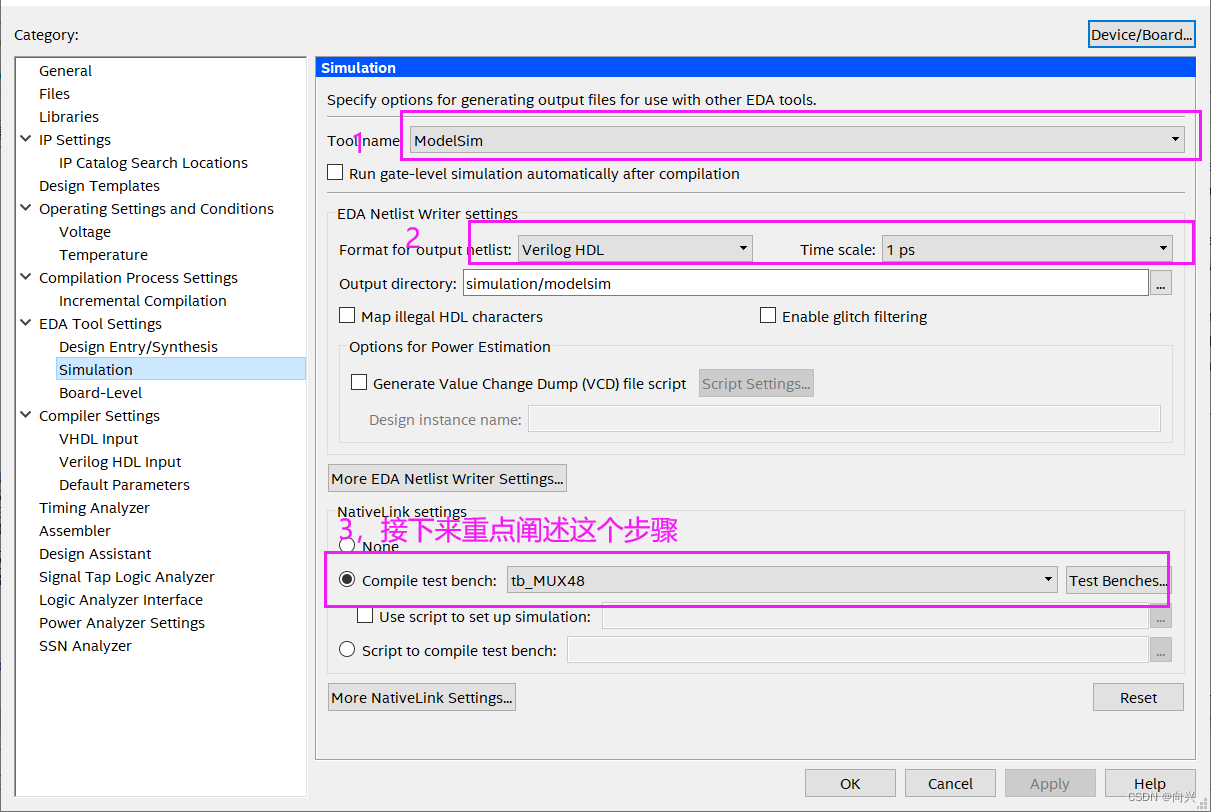

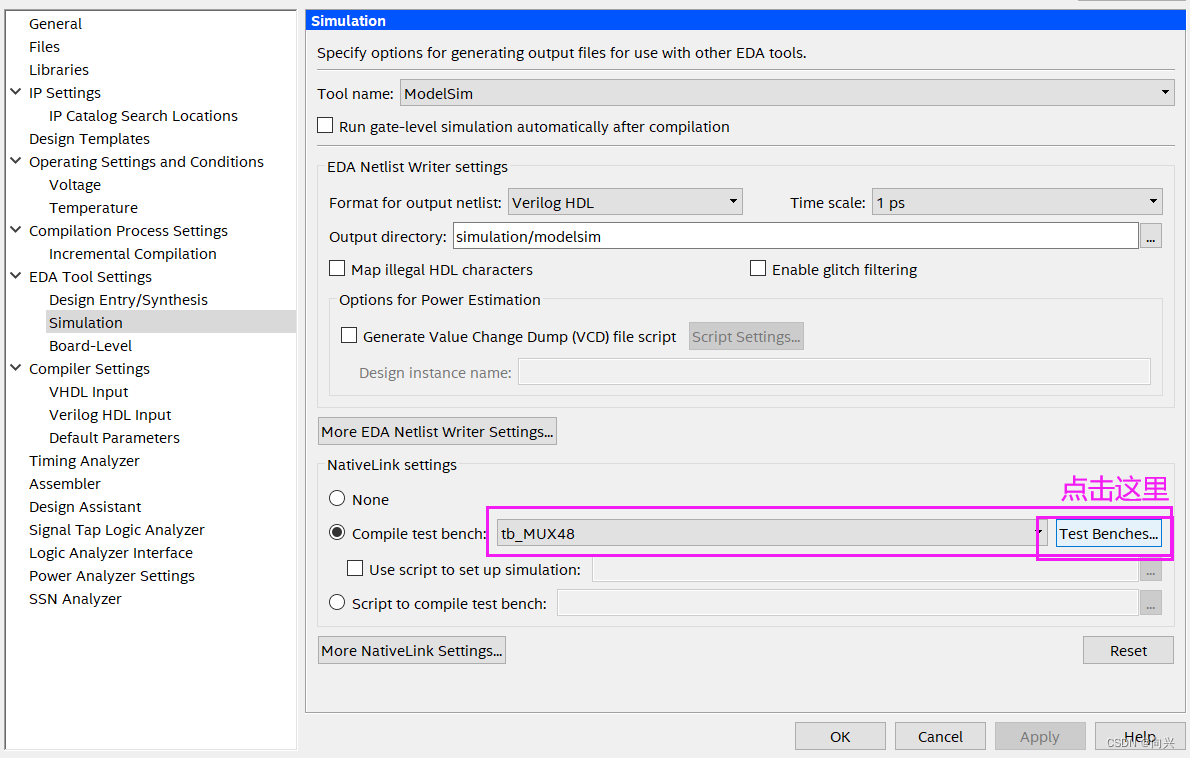

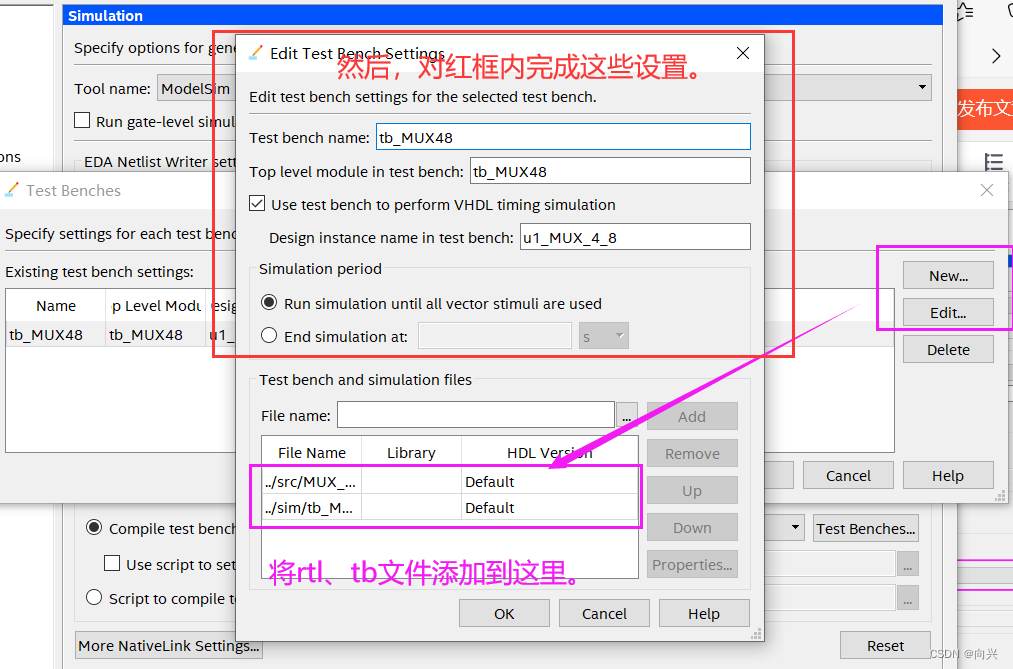

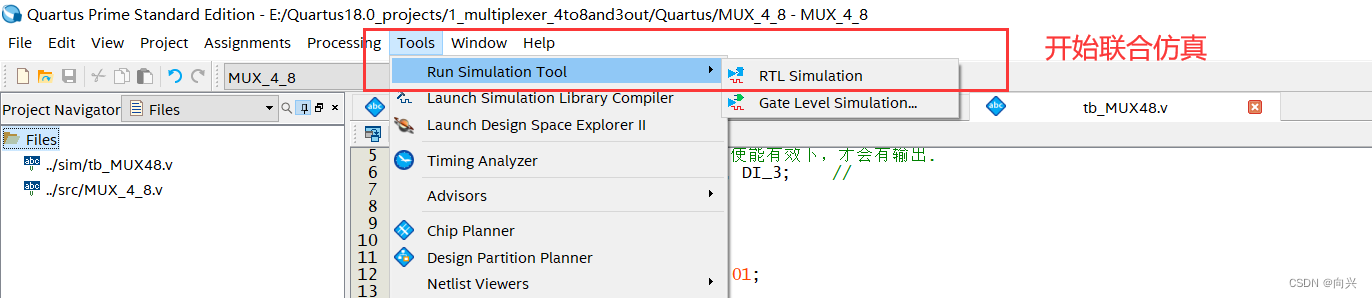

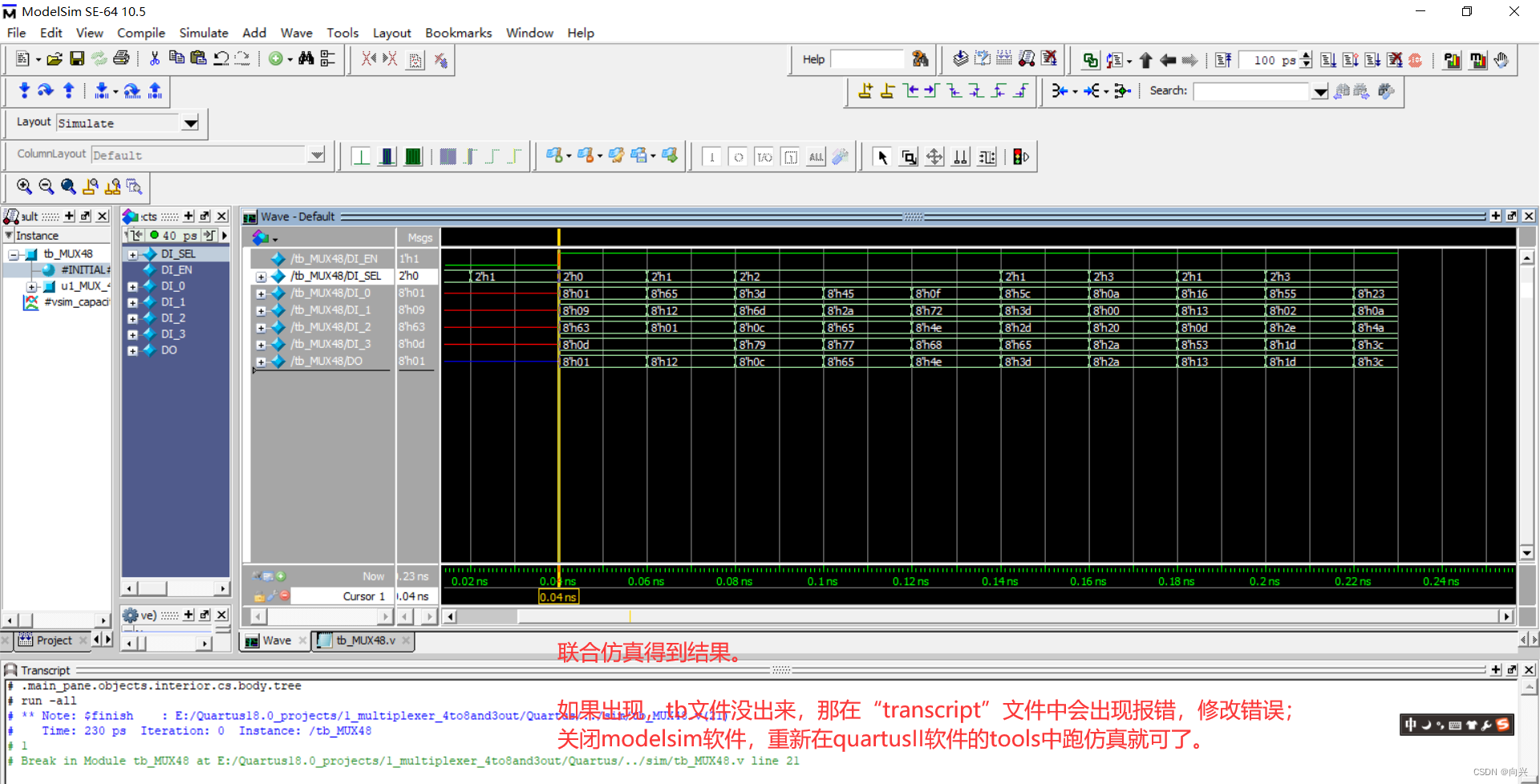

注意:上面是一个新建工程的流程,仅做参考。 1,下面另一个工程,新建工程的流程是一样的,先完成rtl文件的compile后; 2,再添加testbench,然后配置testbench文件与rtl文件的关联性,然后完成关联; 3,仿真,调出仿真软件跑仿真,比如modelsim;

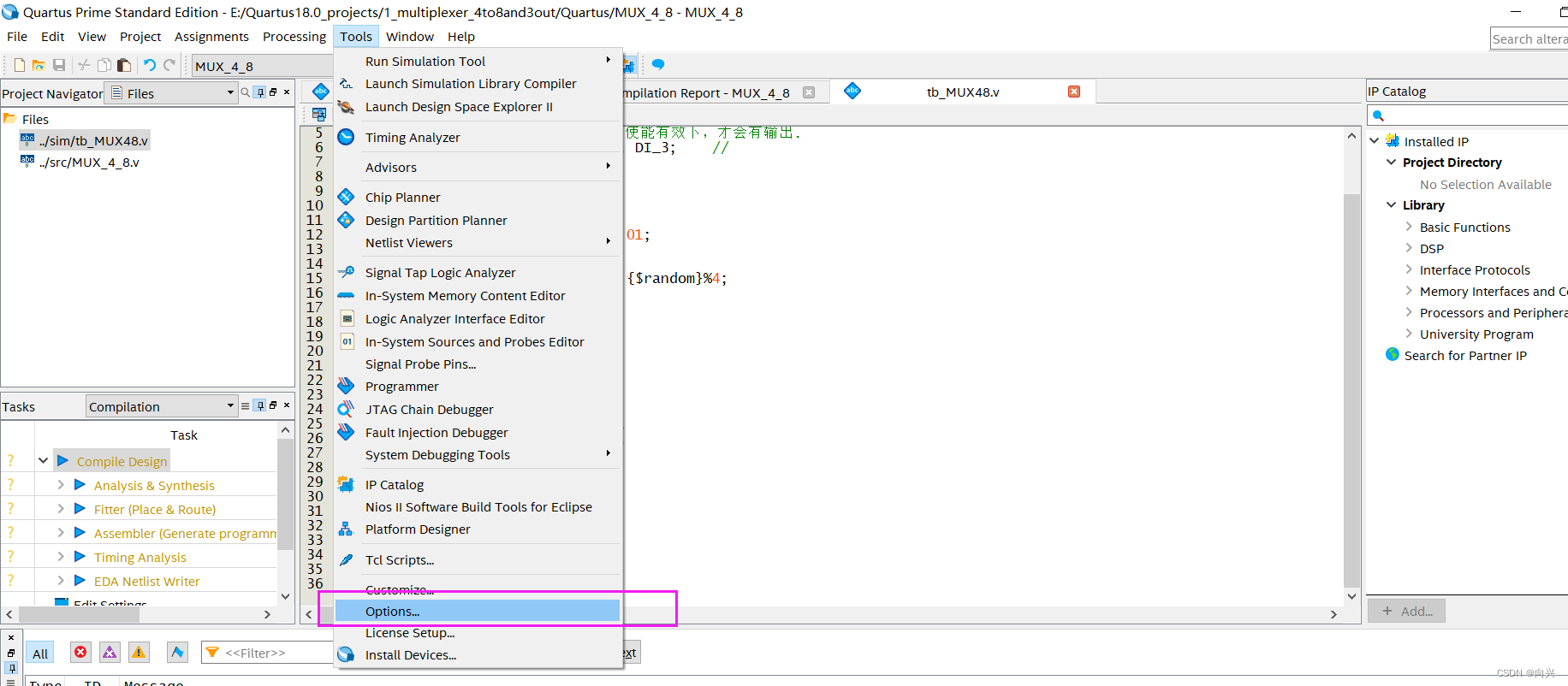

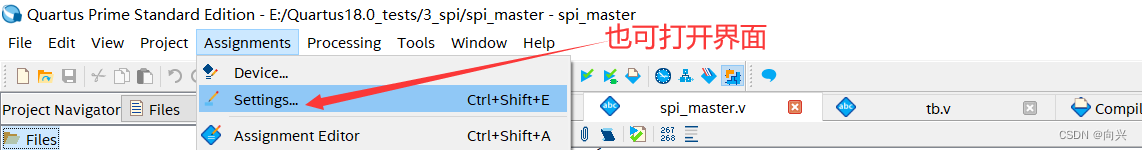

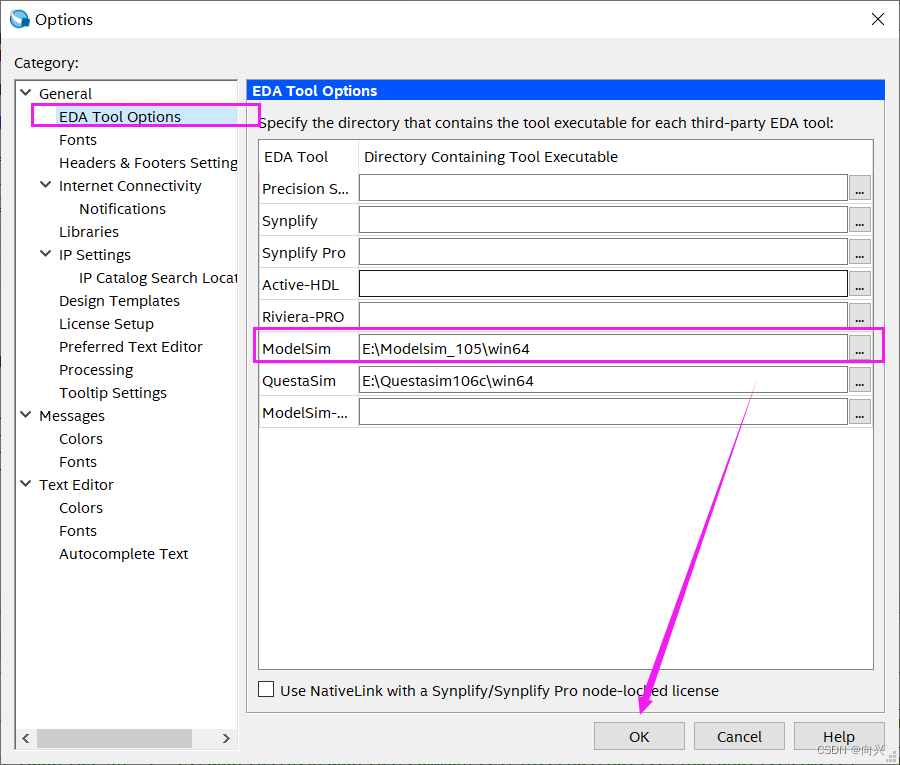

2,Quartus18.0软件配置Modelsim版本的仿真,将两个软件关联起来

第一步,

或者

第二步,

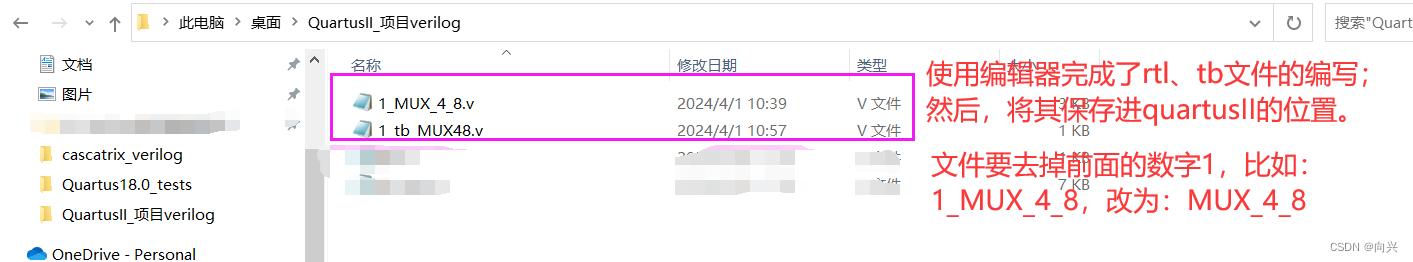

3,在编辑器中写rtl、tb文件并将其保存在这个位置,然后开始配置联合仿真,使rtl、tb两个文件在QuartusII和Modelsim两个软件中关联起来

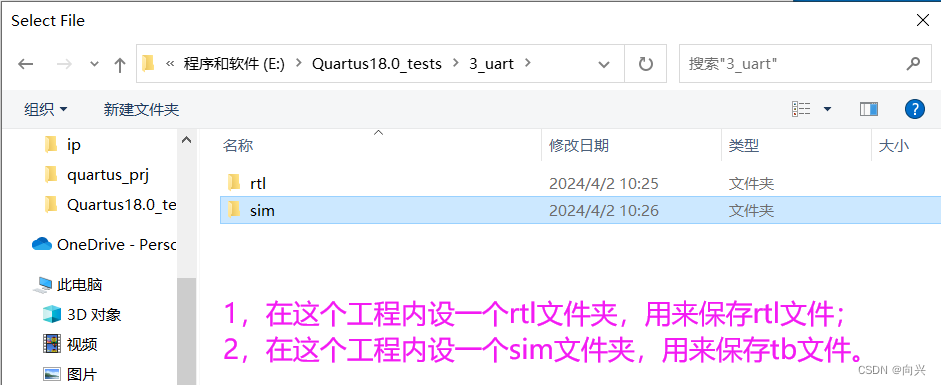

第一步,使用编辑器,完成rtl、tb文件的编写;

注意:这里我使用的是notepad++编辑器。

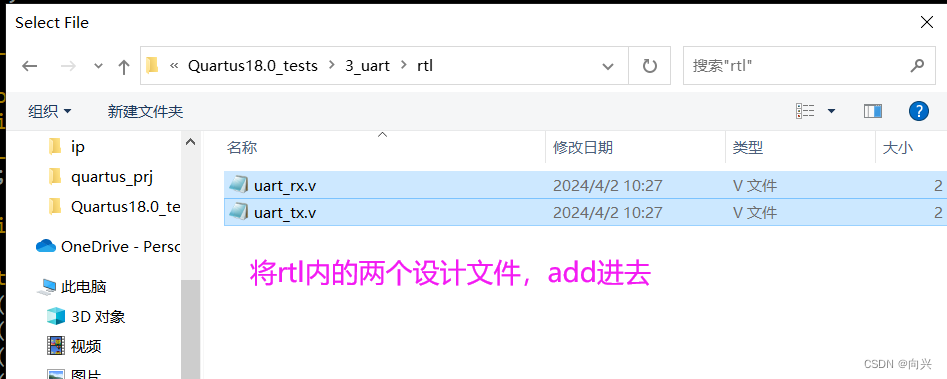

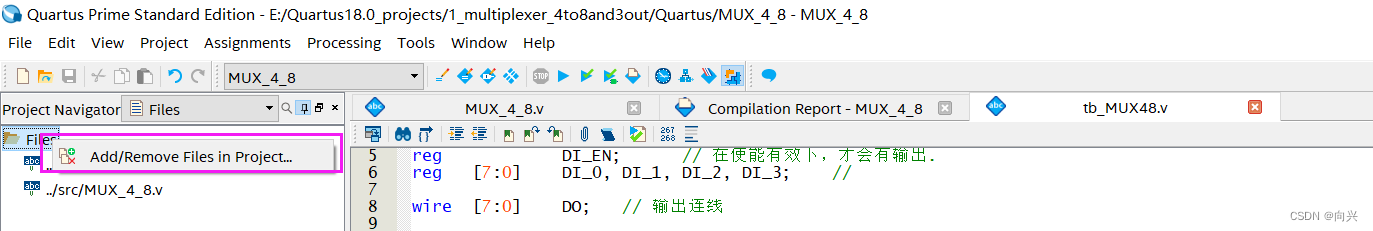

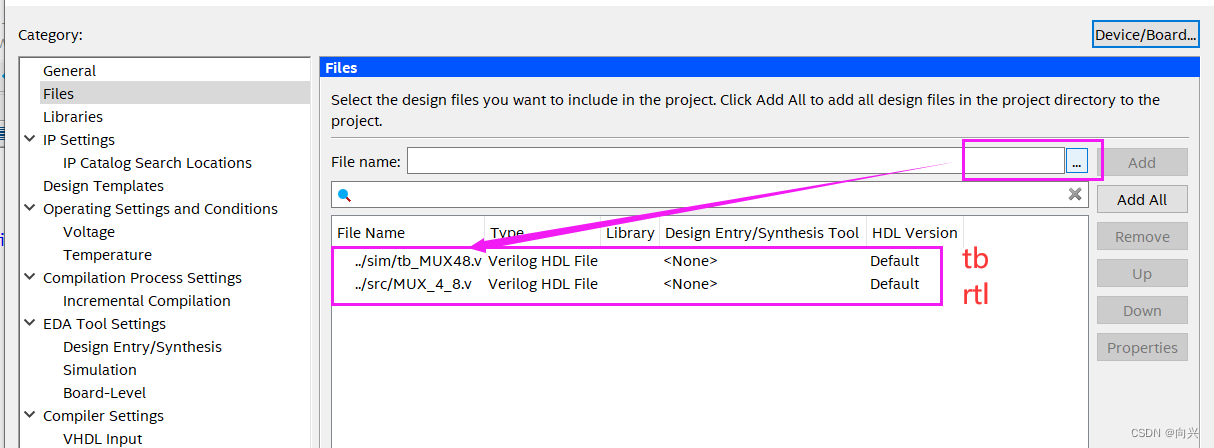

第二步,将文件添加到quartus的文件位置:

(1)

(2)

(3)

(4)

(5)

(6)

(7)联合仿真,在这里完成。

4,两个v文件。

4.1,rtl文件

`define UD #1 module MUX_4_8 ( //Input ports. DI_SEL, // 选择 DI_EN, // 使能 DI_0, // 4输入 DI_1, DI_2, DI_3, //Output ports. DO ); //========================================================================== //Input and output declaration //========================================================================== input [1:0] DI_SEL; input DI_EN; input [7:0] DI_0; input [7:0] DI_1; input [7:0] DI_2; input [7:0] DI_3; output [7:0] DO; //========================================================================== //Wire and reg declaration //========================================================================== wire [1:0] DI_SEL; wire DI_EN; wire [7:0] DI_0; wire [7:0] DI_1; wire [7:0] DI_2; wire [7:0] DI_3; wire [7:0] DO; //========================================================================== //Wire and reg in the module //========================================================================== // 知识点: // DO_INIT 这里定义成一个寄存器型,但实质并不会生成真正的寄存器,这个例程是 // 一个纯组合逻辑。 reg [7:0] DO_INIT; //========================================================================== //Logic //========================================================================== // 知识点: // DI_EN 无效时输出三态。 assign DO = DI_EN ? DO_INIT : 8'hz; // 知识点: // case 结构无优先级 always @ (*) begin case (DI_SEL) 2'h0 : DO_INIT = DI_0; 2'h1 : DO_INIT = DI_1; 2'h2 : DO_INIT = DI_2; 2'h3 : DO_INIT = DI_3; default : DO_INIT = 8'hz; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

4.2,tb文件

// // 测试信号 module tb_MUX48; /*wire */ reg [1:0] DI_SEL; /*wire */ reg DI_EN; // 在使能有效下,才会有输出. /*wire */ reg [7:0] DI_0, DI_1, DI_2, DI_3; // wire [7:0] DO; // 输出连线 initial begin DI_EN = 0; DI_SEL = 00; #20 DI_EN = 0; DI_SEL = 01; repeat(10) begin #20 DI_EN = 1; DI_SEL = {$random}%4; DI_0 = {$random}%128; // 所以这里,需要 reg 型. DI_1 = {$random}%128; DI_2 = {$random}%128; DI_3 = {$random}%128; end #10; $finish; end MUX_4_8 u1_MUX_4_8( .DI_SEL (DI_SEL ), .DI_EN (DI_EN ), .DI_0 (DI_0 ), .DI_1 (DI_1 ), .DI_2 (DI_2 ), .DI_3 (DI_3 ), .DO (DO ), ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/木道寻08/article/detail/790414

推荐阅读

相关标签