- 1CentOS7虚拟机中使用kolla-ansible部署all-in-one模式openstack详细步骤_openstack all in one

- 21.12 实例:猜数字小游戏_verilog猜数字游戏

- 3深度学习如何入门?_深度学习 入门

- 4python calendar模块常用方法_python calendar用法

- 5LeetCode:419. 甲板上的战舰————中等_甲板上的战舰 js

- 6python中的sorted怎么用_python sorted方法和列表使用解析

- 7MySQL知识总结一(MySQL常见术语)_mysql 术语解释

- 8FPGA 20个例程篇:20.USB2.0/RS232/LAN控制并行DAC输出任意频率正弦波、梯形波、三角波、方波(一)_用verilog控制dac产生波形

- 9新版onenet平台安全鉴权的确定与使用_新版onenet没有鉴权_onenet新版本的设备的鉴权信息是什么

- 10ARP解析_arp报文

xilinx原语(a7是不支持idelay2及ctl原语的)_ibufds gte3

赞

踩

1.Xilinx FPGA7系列分为全局时钟(Global clock)和局部时钟(Regional clock)资源,区域时钟Regional clock相较于全局时钟的时钟质量更好。只是区域时钟只是针对于区域类。

- //1

- IBUFDS #(

- .DIFF_TERM ("TRUE"), // Differential Termination

- .IBUF_LOW_PWR ("FALSE"), // Low power="TRUE", Highest performance="FALSE"

- //.IOSTANDARD ("LVDS_25") // Specify the input I/O standard

- .IOSTANDARD ("LVDS") // Specify the input I/O standard

- )

- u_clkds

- (

- .I (i_ad_clk_p),

- .IB (i_ad_clk_n),

- .O (adclk_int)

- );

-

- //2

- BUFR

- #(.SIM_DEVICE("7SERIES"),

- .BUFR_DIVIDE("BYPASS"))

- clkout_buf_inst

- ( .O (adclk_bufg),

- .CE(),

- .CLR(),

- .I (adclk_int)

- //.I (adclk_dly)

- );

- //3

- BUFG u_clkbufg

- (

- .I (adclk_bufg),

- .O (adclk_gclk)

- );

1.差分时钟进入FPGA需用ibufds或者pll的差分输入接口来处理时钟信号。

2.自己推测单端时钟应该怎么写如下

- BUFR

- #(.SIM_DEVICE("7SERIES"),

- .BUFR_DIVIDE("2"))

- clkout_buf_inst

- (.O (clk_div_bufr),

- .CE(1'b1),

- .CLR(clk_reset),

- .I (clk_in_int));

-

- BUFG U_bufr_clk

- (

- .O (clk_div),

- .I (clk_div_bufr)

- );

- IBUFGDS u_IBUFGDS

- (

- .I(clk_p) ,

- .IB(clk_n) ,

- .O(clk)

-

- );

相关知识点:

BUFR是区域时钟缓冲器,要进入区域时钟网络,必须例化BUFR

ibuf是输入缓冲器,用于将外部输入的时钟信号进行缓冲和放大;

bufg是全局缓冲器,用于将经过ibuf缓冲的时钟信号进行进一步的放大和分配

4.实测——输入pcie硬核的差分时钟经过IBUFDS_GTE2,出来后不能直接驱动ila(布线报错),需经过bufg在给ila(才不会报错)——这一点存疑(因为在bd里面同样不经过bufg也没报错)——推断应该和布线资源的消耗有关系,如果报错了就按报错的推荐加bufg。

IBUFDS_GTE2原语————进入GT的两个差分时钟必须要使用该原语,才能给ip核使用。

- IBUFDS_GTE2 #(

- .CLKCM_CFG("TRUE"), // Refer to Transceiver User Guide

- .CLKRCV_TRST("TRUE"), // Refer to Transceiver User Guide

- .CLKSWING_CFG(2'b11) // Refer to Transceiver User Guide

- )

- IBUFDS_GTE2_inst (

- .O(O), // 1-bit output: Refer to Transceiver User Guide

- .ODIV2(ODIV2), // 1-bit output: Refer to Transceiver User Guide

- .CEB(CEB), // 1-bit input: Refer to Transceiver User Guide

- .I(I), // 1-bit input: Refer to Transceiver User Guide

- .IB(IB) // 1-bit input: Refer to Transceiver User Guide

- );

-

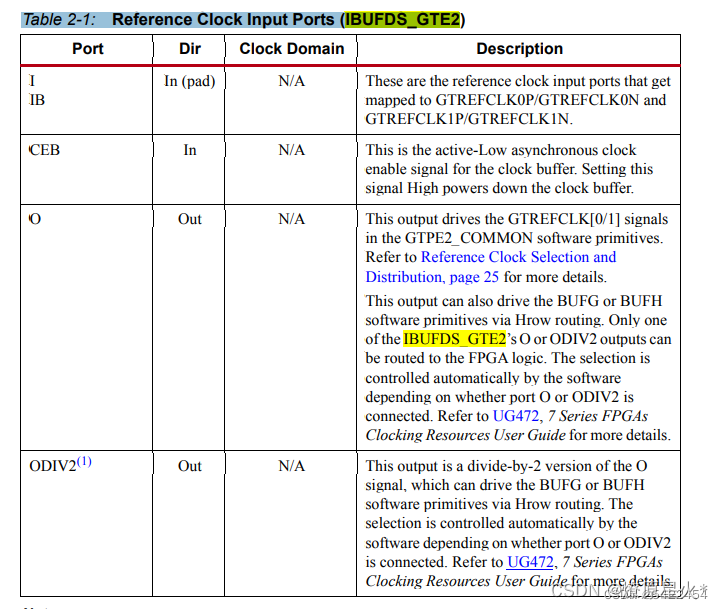

1) I和IB是一对差分输入;

2) CEB低有效,高表示不使能IBUFDS_GTE2;

3) O 和 ODIV2都可以驱动BUFG或BUFH;

4) O 和 ODIV2 哪个连接到程序中哪个起作用;

5:clkswing_cfg:只能设置2'd11(手册上说的)

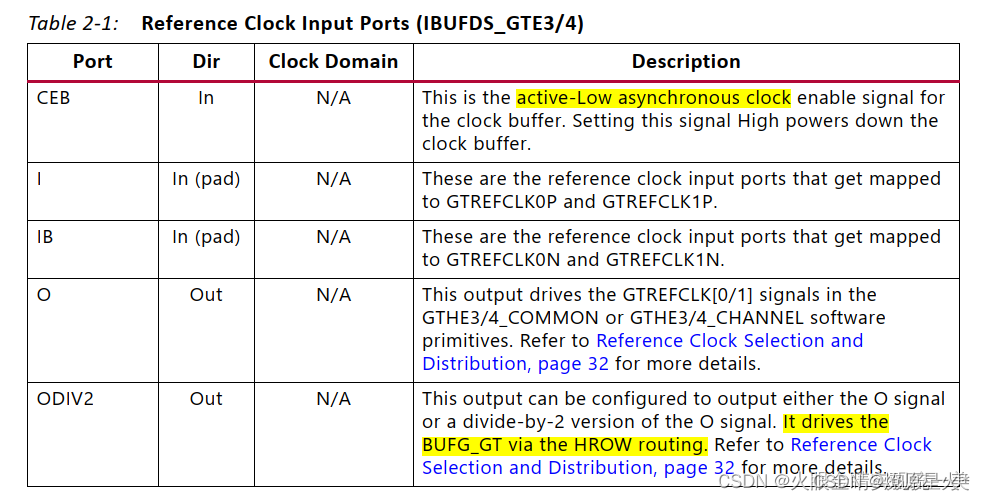

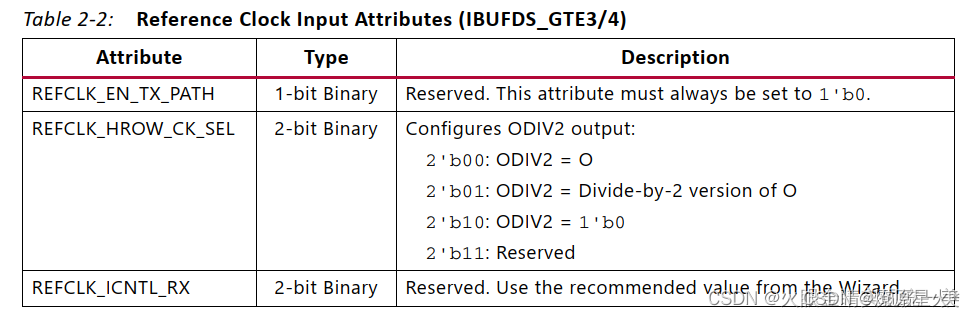

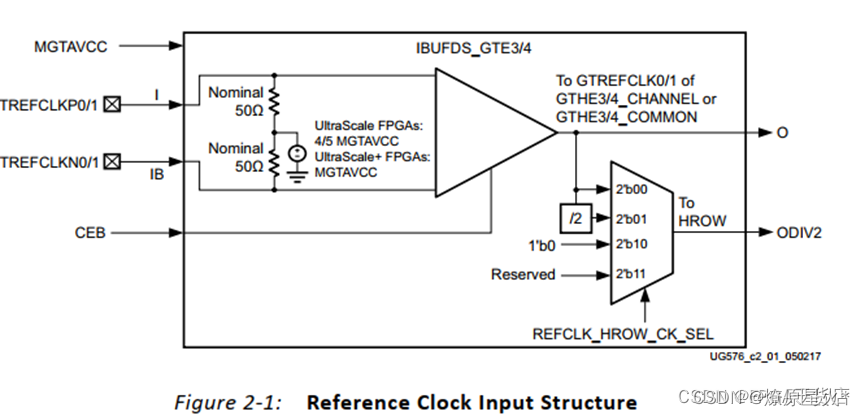

五: IBUFDS_GTE3 原语

六:BUFG

全局时钟缓冲。它的输入是IBUFG的输出,BUFG的输出到达FPGA内部的IOB、CLB、选择性块RAM的时钟延迟和抖动最小。BUFG连接的是芯片中的专用时钟资源,能减少信号的传输延时,提高驱动能力。BUFG可以到达设备上的任何时钟点。

注意:如果内部产生的时钟,只在局部模块使用,可以考虑不使用BUFG。一个BUFG只能驱动一个时钟。

- BUFG BUFG_inst (

- .O(CLK0), // 1-bit output: Clock output.

- .I(CLK) // 1-bit input: Clock input.

- );

七:IBUF

介绍

输入缓冲,综合的时候,工具会自动给输入信号连接IBUF。

IBUF IBUF_inst (

.O(O), // 1-bit output: Buffer output

.I(I) // 1-bit input: Buffer input

);

八:IBUFDS

重点是差分。

IBUFGDS的输入端仅仅与芯片的专用全局时钟输入管脚有物理连接,与普通IO和其它内部CLB等没有物理连接,因此差分信号进入片内之后不经过IBUFDS缓冲是无法直接处理的,即无法使用。

- IBUFDS IBUFDS_inst (

- .O(O), // 1-bit output: Buffer output

- .I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

- .IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

- );

-

九:

1.

IBUFDS_GTEx,x=2/3/4,差分缓冲器,用于高速BANK(GTY BANK)的两路参考时钟输入。其中UltraScale使用IBUFDS_GTE3作为GTY bank的差分缓冲器,UltraScale+采用IBUFDS_GTE4。对于高速BANK,需要使用IBUFDS_GTEx(不同系列的FPGA x的值不同,如x=2/3/4),如果仍然使用IBUFDS,可能会在编译或者生成bit文件时报错

2.

使用原语驱动GTX/GTH/GHY参考时钟,每个Quad有两个IBUFDS_GTEx元件,驱动GTREFCLK0和GTREFCLK1,常用模式是实例化一个IBUFDS_GTEx并驱动两个参考时钟之一。

十:

逻辑设计中需要显式地使用IBUF以及OBUF类似的原语吗?——————不需要