- 1传统图像处理算法总结_传统图像算法

- 2AI技术创业有哪些机会_ai时代创业机会

- 3自然语言处理:使用NLTK库进行文本分析_nltk如何对中文文本进行分析

- 4SQLServer2008R2中sa的密码忘记了怎么办?_sql2008r2sa密码查看

- 5iMazing2023官网中文版下载及许可证附使用教程_imazing官网

- 6字节跳动,三轮面试,四个小时,灵魂拷问,结局我哭了但下次还敢!!!

- 7我的Ollama+openWebUI部署笔记_llava openweb ui

- 8云网络与云计算:有什么区别?

- 9NOAUTH Authentication required.错误解决办法

- 10【uses ARM-Compiler ‘Default Compiler Version 5‘ which is not available 】_uses arm-compiler 'default compiler version 5' whi

XILINX Ultrascale+ FPGA学习(1)——I/O口和原语介绍_ultrascale 接口

赞

踩

介绍

主要介绍Zynq UltraScale+ MPSoC,FPGA选择和xilinx FPGA家族参考PDF。

FPGA文档教程查询。

对于新手学习UltraScale+ FPGA的建议

Xilinx的SOC芯片分为PL端和PS端。

PL端可以就是FPGA(采用LCU),其使用方法和传统的FPGA一样;而PS端是arm处理器,与树莓派、STM32使用方法相似。

如果第一次接触FPGA,那么你需要从最基本的Verilog语言学起,如果你使用过传统FPGA,那么学习Zynq UltraScale+ MPSoC可以参考本人的学习过程。

Zynq UltraScale+ MPSoC介绍

Zynq UltraScale+ MPSoC其总框架参考链接.

Zynq UltraScale+ MPSoC其硬件参数参考链接.

Zynq UltraScale+ MPSoC其电气特性参考链接.

Zynq UltraScale+ MPSoC其引脚资源参考链接.

文章目录

- 介绍

- 接口原语

- 单端I/O原语

- 差分I/O原语

- IBUFDS(差分输入buffer)

- IBUFDS_DIFF_OUT (具有互补输出的差分输入缓存)

- IBUFDS_DIFF_OUT_IBUFDISABLE

- IBUFDS_DIFF_OUT_INTERMDISABLE

- IBUFDS_IBUFDISABLE

- IBUFDS_INTERMDISABLE

- IBUFDSE3

- IBUFDS_DPHY

- IOBUFDS(差分双向缓存)

- IOBUFDS_DCIEN

- OBUFDS_DIFF_OUT

- IOBUFDS_DIFF_OUT_DCIEN

- IOBUFDS_INTERMDISABLE

- IOBUFDS_DIFF_OUT_INTERMDISABLE

- IOBUFDSE3

- OBUFDS(差分输出buffer)

- OBUFTDS(差分三态输出缓存)

- OBUFDS_DPHY

- HPIO_VREF

- I/O接口属性和约束

I/O接口资源介绍

这里大致介绍一下该芯片的引脚。其包括三类引脚:

High-performance(HP) I/O

高速引脚,其设计是为了满足高速存储器和其他芯片对芯片接口的性能要求,支持1.8V,1.5V,1.35V,1.2V ,1V I/O标准,支持LVDS信号(1.8V),数控阻抗,内部参考电压,内部差分终端,延迟可调,串并转换(ISERDES)等功能。

可以完全满足高速信号的接收

High-range (HR) I/O

宽电平引脚,其设计是为了满足更广泛的I/O标准。支持支持3.3V,2.5V,1.8V,1.5V,1.35V,1.2V I/O标准,支持LVDS信号(2.5V),内部参考电压,内部差分终端,延迟可调,串并转换等功能。

下图是HP I/O和HR I/O总结

这里值得一提的是HP I/O可以进行数字阻抗控制(DCI),简单来说HP I/O的输出阻抗可以数字可调,这里不做描述,其具体配置参考上面引脚配置的文档。

High-density (HD) I/O

高密度引脚,用于低速接口设计,其专为单端电压参考伪差分I/O标准最高数据率位250Mb/s。对真差分提供有限支持(需要外接匹配电阻),支持3.3V,2.5V,1.8V,1.5V,1.35V,1.2V I/O标准,支持LVDS信号和LVPECL(2.5V)输入,内部参考电压,最大数据率250Mb/s,支持ILOGIC和OLOGIC,上下拉保持,ZHOLD。

注意其不支持内部差分终端,不支持数控阻抗控制,不支持串并转换(ISERDES),不支持延迟(IDELAY),不支持DQS_BIAS,不支持差分输出。

接口原语

原语(Primitives),是xlinx公司定义的能够实现特定功能的模块(这些模块大部分是硬件结构,也有软件结构),这些模块可以简单的看作是一个c里面的类,或者是FPGA里的IP。使用原语可以简化我们编程的逻辑。

常用原语:单端:IBUF(输入缓存),IOBUF(双向缓存),OBUF(输出缓存);差分:IBUFDS(差分输入),OBUFDS(差分输出)

单端I/O原语

值得一提的是,可以在vivado软件的Language Templates查到原语的实例化模板,(即在Verilog语言中使用该原语)

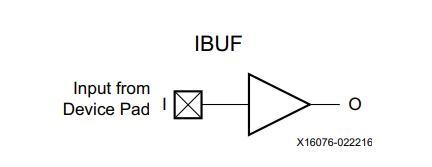

IBUF(输入buffer)

信号输入必须使用该输入buffer。其原语结构如下:

// IBUF: Input Buffer

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IBUF IBUF_inst (

.O(O), // 1-bit output: Buffer output

.I(I) // 1-bit input: Buffer input

);

// End of IBUF_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

IBUF_IBUFDISABLE(具有缓存禁用控制功能的输入缓存)

该原语在不使用输入的时候,可以禁用端口的输入缓存,主要目的是省电。

当IBUFDISABLE为高电平时,IBUF_IBUFDISABLE原语可以禁用输入缓存,并将输入的逻辑设置为低电平。为了使该原语的行为与特定于 UltraScale 架构的预期行为相符,必须满足下列条件:将USE_IBUFDISABLE 属性设置为 TRUE,控制 IBUFDISABLE 端口,并将 SIM_DEVICE 设置为 ULTRASCALE。此功能可用于在 I/O 空闲时降低功耗。将 IBUFDISABLE 信号设置为逻辑高电平对于使用 VREF 电源轨的输入缓存 (例如 SSTL 和HSTL)最有益,因为这些缓存的静态功耗往往比非 VREF 标准 (例如 LVCMOS 和 LVTTL)更高。

// IBUF_IBUFDISABLE: Input Buffer With Input Buffer Disable

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IBUF_IBUFDISABLE #(

.SIM_DEVICE("ULTRASCALE"), // Set the device version for simulation functionality (ULTRASCALE)

.USE_IBUFDISABLE("TRUE") // Enable/Disable the IBUFDISABLE pin (FALSE, TRUE, T_CONTROL)

)

IBUF_IBUFDISABLE_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Buffer input (connect directly to top-level port)

.IBUFDISABLE(IBUFDISABLE) // 1-bit input: Buffer disable input, high=disable

);

// End of IBUF_IBUFDISABLE_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

IBUF_INTERMDISABLE

该原语在HR I/O中使用,其功能与IBUF_IBUFDISABLE相似。当IBUFDISABLE为高电平时,IBUF_IBUFDISABLE原语可以禁用输入缓存,并将输入的逻辑设置为低电平。每当 INTERMDISABLE 信号断言为高电平有效时,IBUF_INTERMDISABLE 原语还允许禁用终端分支。

// IBUF_INTERMDISABLE: Input Buffer With Input Buffer Disable and On-die Input Termination Disable

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IBUF_INTERMDISABLE #(

.SIM_DEVICE("ULTRASCALE"), // Set the device version for simulation functionality (ULTRASCALE)

.USE_IBUFDISABLE("TRUE") // Enable/Disable the IBUFDISABLE pin (FALSE, TRUE)

)

IBUF_INTERMDISABLE_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Buffer input (connect directly to top-level port)

.IBUFDISABLE(IBUFDISABLE), // 1-bit input: Buffer disable input, high=disable

.INTERMDISABLE(INTERMDISABLE) // 1-bit input: Input Termination Disable

);

// End of IBUF_INTERMDISABLE_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

IBUFE3

仅在HP I/O中使用的原语,与IBUF_IBUFDISABLE用法相似。并增加了偏移校准和 VREF 调整控制功能,以及输入缓存禁用 (IBUFDISABLE)。可使用 OSC_EN 和 OSC [3:0] 端口访问偏移校准功能(校准电压)。通过将 HPIO_VREF 原语与 IBUFE3 结合使用即可访问 VREF 扫描功能(微调输入缓存内部VREF电压,以便最大程度提高 I/O 标准子集的性能)。

在使用偏移校准时,OSC_EN 设置为1’b1,OSC[3:0]的值与偏移的电压有关,如下表

如果输入存在15mV的偏移,设置OSC[3:0]=1011取消偏移。

// IBUFE3: Input Buffer with Offset Calibration and VREF Tuning

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IBUFE3 #(

.SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version for simulation functionality (ULTRASCALE,

// ULTRASCALE_PLUS)

.SIM_INPUT_BUFFER_OFFSET(0), // Offset value for simulation (-50-50)

.USE_IBUFDISABLE("FALSE") // Enable/Disable the IBUFDISABLE pin (FALSE, TRUE, T_CONTROL)

)

IBUFE3_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Buffer input (connect directly to top-level port)

.IBUFDISABLE(IBUFDISABLE), // 1-bit input: Buffer disable input, high=disable

.OSC(OSC), // 4-bit input: Offset cancellation value

.OSC_EN(OSC_EN), // 1-bit input: Offset cancellation enable

.VREF(VREF) // 1-bit input: Vref input from HPIO_VREF

);

// End of IBUFE3_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

IOBUF(双向缓存)

该原语用于,双向信号既需要输入缓存又需要具有高电平有效三态T管脚的三态输出缓存。T 管脚上的逻辑高电平会禁用输出缓存。当输出缓存为三态 (T = High) 时,输入缓存和任何片上接收器终端 (未校准或 DCI)都为 ON。当输出缓存未处于三态 (T = Low) 时,任何片上接收器终端 (未校准或 DCI)均被禁用。

HP I/O bank 具有适用于 SSTL、 HSTL、 POD 和 HSUL 标准 (类似于 DCI)的可选未校准源极终端功能。此功能为受支持的标准提供 40Ω、 48Ω, 或 60Ω 驱动选项,以匹配驱动线路的特性阻抗。

// IOBUF: Input/Output Buffer

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IOBUF IOBUF_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Buffer input

.IO(IO), // 1-bit inout: Buffer inout (connect directly to top-level port)

.T(T) // 1-bit input: 3-state enable input

);

// End of IOBUF_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

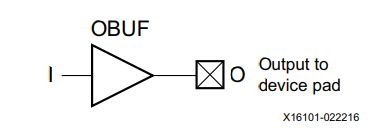

OBUF(输出buffer)

输出buffer,其原语如下

// OBUF: Output Buffer

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

OBUF OBUF_inst (

.O(O), // 1-bit output: Buffer output (connect directly to top-level port)

.I(I) // 1-bit input: Buffer input

);

// End of OBUF_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

OBUFT(三态输出缓存)

通用三态输出缓存 OBUFT 通常实现三态输出或双向 I/O。

// OBUFT: 3-State Output Buffer

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

OBUFT OBUFT_inst (

.O(O), // 1-bit output: Buffer output (connect directly to top-level port)

.I(I), // 1-bit input: Buffer input

.T(T) // 1-bit input: 3-state enable input

);

// End of OBUFT_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

IOBUF_DCIEN

在 HP I/O bank 中使用。它具有 IBUFDISABLE 端口,该端口可在不使用缓存期间禁用输入缓存。 IOBUF_DCIEN 原语还具有 DCITERMDISABLE 端口,该端口可用于手动禁用可选的片上接收器终端功能(未校准和 DCI)。其使用方法参考IBUF_INTERMDISABLE和OBUFT。

// IOBUF_DCIEN: Input/Output Buffer DCI Enable

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IOBUF_DCIEN #(

.SIM_DEVICE("ULTRASCALE"), // Set the device version for simulation functionality (ULTRASCALE)

.USE_IBUFDISABLE("TRUE") // Enable/Disable the IBUFDISABLE pin (FALSE, TRUE, T_CONTROL)

)

IOBUF_DCIEN_inst (

.O(O), // 1-bit output: Buffer output

.DCITERMDISABLE(DCITERMDISABLE), // 1-bit input: DCI Termination Disable

.I(I), // 1-bit input: Buffer input

.IBUFDISABLE(IBUFDISABLE), // 1-bit input: Buffer disable input, high=disable

.IO(IO), // 1-bit inout: Buffer inout (connect directly to top-level port)

.T(T) // 1-bit input: 3-state enable input

);

// End of IOBUF_DCIEN_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

IOBUF_INTERMDISABLE

在HR I/O中使用,其使用与IOBUF_DCIEN。

// IOBUF_INTERMDISABLE: Bidirectional Buffer with Input Path Disable and On-die Input Termination Disable

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IOBUF_INTERMDISABLE #(

.SIM_DEVICE("ULTRASCALE"), // Set the device version for simulation functionality (ULTRASCALE)

.USE_IBUFDISABLE("TRUE") // Enable/Disable the IBUFDISABLE pin (FALSE, TRUE)

)

IOBUF_INTERMDISABLE_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Buffer input

.IBUFDISABLE(IBUFDISABLE), // 1-bit input: Buffer disable input, high=disable

.INTERMDISABLE(INTERMDISABLE), // 1-bit input: Input Termination Disable

.IO(IO), // 1-bit inout: Buffer inout (connect directly to top-level port)

.T(T) // 1-bit input: 3-state enable input

);

// End of IOBUF_INTERMDISABLE_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

IOBUFE3

仅在HP I/O中使用,与IOBUF_DCIEN类似。

差分I/O原语

其用法与单端相似

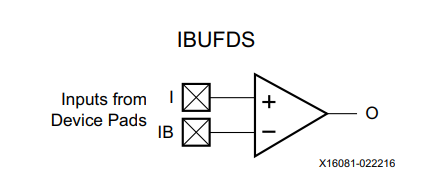

IBUFDS(差分输入buffer)

将差分输入信号转化为单端输入信号的原语,其原语如下:

其中I表示差分输入的P端,IB代表N端。

IBUFDS_DIFF_OUT (具有互补输出的差分输入缓存)

具有互补输出 (O 和 OB)的差分输入缓存原语。

IBUFDS_DIFF_OUT_IBUFDISABLE

IBUFDS_DIFF_OUT_INTERMDISABLE

用法与单端IBUF_INTERMDISABLE相似。在HR I/O中使用。

IBUFDS_IBUFDISABLE

与单端IBUF_IBUFDISABLE原语相似。

IBUFDS_INTERMDISABLE

用法与单端IBUF_INTERMDISABLE相似。在HR I/O中使用。

IBUFDSE3

与单端IBUFE3原语用法相似,只能在HP I/O中使用

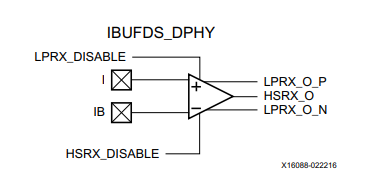

IBUFDS_DPHY

仅在Virtex UltraScale+ 、Kintex UltraScale+ 器件和 Zynq UltraScale+ 器件中的HP I/O中使用。

此特定于 UltraScale 架构的原语专用于 MIPI D-PHY 接收器实现。 HSRX_DISABLE 端口用于启用或禁用 MIPI D-PHY 高速 (HS) 接收器。 LPRX_DISABLE 端口用于启用或禁用低功耗 (LP) 接收器。 HSRX_O 和LPRX_O(_P/_N) 分别从 HS 和 LP 接收器输入到互联逻辑。该原语仅支持MIPI_DPHY_DCI 作为 IOSTANDARD 属性的值。

// IBUFDS_DPHY: Differential Input Buffer with MIPI support

// Kintex UltraScale+

// Xilinx HDL Language Template, version 2021.2

IBUFDS_DPHY #(

.DIFF_TERM("TRUE"), // Differential termination

.IOSTANDARD("DEFAULT"), // I/O standard

.SIM_DEVICE("ULTRASCALE_PLUS") // Set the device version (ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1,

// ULTRASCALE_PLUS_ES2)

)

IBUFDS_DPHY_inst (

.HSRX_O(HSRX_O), // 1-bit output: HS RX output

.LPRX_O_N(LPRX_O_N), // 1-bit output: LP RX output (Slave)

.LPRX_O_P(LPRX_O_P), // 1-bit output: LP RX output (Master)

.HSRX_DISABLE(HSRX_DISABLE), // 1-bit input: Disable control for HS mode

.I(I), // 1-bit input: Data input0 PAD

.IB(IB), // 1-bit input: Data input1 PAD

.LPRX_DISABLE(LPRX_DISABLE) // 1-bit input: Disable control for LP mode

);

// End of IBUFDS_DPHY_inst instantiation

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

IOBUFDS(差分双向缓存)

与单端的IOBUF用法相似,T 管脚上的逻辑高电平表示禁用输出缓存。当输出缓存为三态 (T = High) 时,输入缓存和任何片上接收器终端 (未校准或 DCI)都为 ON。当输出缓存未处于三态 (T = Low) 时,任何片上接收器终端 (未校准或 DCI)均被禁用。

IOBUFDS_DCIEN

用于HP I/O口。用法与单端IOBUF_DCIEN相似。

OBUFDS_DIFF_OUT

T 管脚上的逻辑高电平表示禁用输出缓存。当输出缓存处于三态 (T = High) 时,输入缓存和任何片上接收器终端(未校准或 DCI)均为 ON。当输出缓存未处于三态 (T= Low) 时,任何片上接收器终端 (未校准或 DCI)均被禁用。必须将 TM 和 TS 连接到来自互联逻辑的相同输入,以使此原语的行为与特定于 UltraScale 架构的预期行为相符。

IOBUFDS_DIFF_OUT_DCIEN

在HP I/O中使用。它具有互补差分输出、一个 IBUFDISABLE 端口和一个 DCITERMDISABLE 端口,可用于手动禁用可选 DCI 片上接收器终端功能 (未校准或 DCI)。必须将 TM 和 TS 连接到来自互联逻辑的相同输入,以使此原语的行为与特定于 UltraScale 架构的预期行为相符。

如果 I/O 使用任何片上接收器终端功能 (未校准或 DCI),则当 DCITERMDISABLE 信号断言为高电平有效且输出缓存为三态时,该原语将禁用终端分支。当输出缓存为三态 (T = High) 时,任何片上接收器终端 (未校准或 DCI)均由DCITERMDISABLE 控制。当输出缓存未处于三态 (T = Low) 时,输入缓存和片上接收器终端 (未校准或 DCI)都被禁用,并且强制将 O 输出 (至内部逻辑)设置为逻辑低电平。

IOBUFDS_INTERMDISABLE

在H/R引脚中使用。它具有一个 IBUFDISABLE 端口,该端口可在不使用缓存期间禁用输入缓存。IOBUFDS_INTERMDISABLE 原语还具有一个 INTERMDISABLE 端口,该端口可用于禁用可选片上接收器终端功能。

当 IBUFDISABLE 信号断言为高电平有效且输出缓存为三态 (T = High) 时,IOBUFDS_INTERMDISABLE 原语可以禁用输入缓存,并强制将至内部逻辑的 O 输出设置为逻辑低电平。为了使该原语的行为与特定于 UltraScale 架构的预期行为相符,必须满足下列条件:将 USE_IBUFDISABLE 属性设置为 TRUE,控制 IBUFDISABLE 端口,并将 SIM_DEVICE 设置为ULTRASCALE。如果 I/O 使用片上接收器终端功能,则只要 INTERMDISABLE 信号断言为高电平有效且输出缓存为三态,此原语就会禁用终端分支。当输出缓存为三态 (T = High) 时,输入缓存和任何片上接收器终端分别由 IBUFDISABLE和 INTERMFIDISABLE 控制。当输出缓存未处于三态 (T = Low) 时,输入缓存和片上接收器终端均被禁用,并且强制将O 输出 (至内部逻辑)设置为逻辑低电平。这些功能可以组合使用,以在输入空闲一段时间后降低功耗。

尽管不常见,但如果设计要求输入处于持续启用状态,同时保留动态控制 DCI 的功能,则可以通过使 IBUFDISABLE 管脚保持浮动并将 USE_IBUFDISABLE 属性设置为 FALSE 来使用该原语。

IOBUFDS_DIFF_OUT_INTERMDISABLE

在HR I/O口使用。

IOBUFDSE3

在HP I/O口中使用,其用法与单端IOBUFE3。

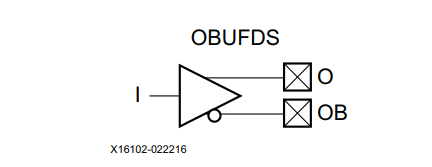

OBUFDS(差分输出buffer)

差分输出buffer,同样的OB为N端,O为P端。

OBUFTDS(差分三态输出缓存)

OBUFDS_DPHY

仅在 Virtex UltraScale+、 Kintex UltraScale+ 和 Zynq UltraScale+ 器件的 HP I/O bank 中支持差分输出缓存原语。此特定于 UltraScale 架构的原语用于 MIPI D-PHY 发射器实现。HSTX_T 端口用于将 MIPID-PHY 高速 (HS) 发射器设为三态。LPTX_T 端口用于将低功耗 (LP) 发射器设为三态。HSTX_I 和 LPTX_I(_P/_N) 输入分别对应从互联逻辑到 HS 发射器的输入和从互联逻辑到 LP 发射器输入。该原语仅支持 MIPI_DPHY_DCI 作为 IOSTANDARD属性的值。

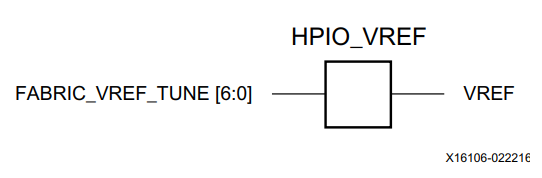

HPIO_VREF

仅在HP I/O中使用。此特定于 UltraScale 架构的原语可提供对 HP I/O bank 中可用的 VREF 扫描功能的访问。通过将 HPIO_VREF 原语与 IBUFE3 或 IOBUFE3 原语结合使用即可访问 VREF 扫描功能。

I/O接口属性和约束

属性和约束(具体参考上面的引脚配置链接)其实就是FPGA中引脚设置,包括位置约束(pin 分配),输入延迟,输出驱动电压,转换速率等。注意这里的约束都是在xdc文件中编写(参考博客),其都用关键字set_property开头 。

这里介绍常用的约束属性。

PACKAGE_PIN 约束

必须使用 PACKAGE_PIN 约束来指定外部端口标识符的 I/O 位置,即FPGA引脚选择(如A8、M5),其用法为:

set_property PACKAGE_PIN pin_name [get_ports port_name]

- 1

IOSTANDARD 属性

IOSTANDARD 属性可用于为所有 I/O 缓存选择 I/O 标准的值。即用于选择I/O口的电压值。

set_property IOSTANDARD value [get_ports port_name]

- 1

IOSTANDARD 属性

IBUF_LOW_PWR 属性允许在性能和功耗之间进行可选的利弊取舍。默认情况下,此属性设置为 TRUE,即以低功耗模式而不是高性能模式来实现输入缓存。

对于数据速率>1.6GB/s,使用FALSE。

IBUF_LOW_PWR 属性可应用于 I/O 缓存实例,并在 XDC 文件中使用以下语法:

set_property IBUF_LOW_PWR TRUE|FALSE [get_ports port_name]

- 1

差分终端属性

设置I/O口差分的终端电阻,阻值为100Ω,对于 HP I/O bank, I/O bank 的 VCCO 必须连接到 1.8V,而对于 HR I/O bank,则必须连接到 2.5V,以提供 100Ω 的有效差分终端。

在verilog中可以使用DIFF_TERM,其值为:

DIFF_TERM = TRUE (使用差分终端电阻)

DIFF_TERM = FALSE (不使用)

而在约束中,使用DIFF_TERM_ADV 来设置,其值为:

DIFF_TERM_ADV = TERM_NONE (默认)

DIFF_TERM_ADV = TERM_100

在XDC文件中设置的格式如下:

set_property DIFF_TERM_ADV [get_ports port_name]

- 1

LVDS 发射器预加重

使用 LVDS 发射器器预加重 (LVDS_PRE_EMPHASIS) 功能可以针对某些 I/O 标准在驱动上进行预加重。此属性必须与ENABLE_PRE_EMPHASIS 结合使用。

LVDS_PRE_EMPHASIS 属性的允许值为:

LVDS_PRE_EMPHASIS = FALSE (默认值)

LVDS_PRE_EMPHASIS = TRUE (其中 ENABLE_PRE_EMPHASIS 必须设置为 TRUE)

LVDS_PRE_EMPHASIS 属性在 XDC 文件中使用以下语法:

set_property LVDS_PRE_EMPHASIS TRUE|FALSE [get_ports port_name]

- 1