热门标签

热门文章

- 1低危-TLS 1.0 协议启用漏洞_tls 1.0 enabled 漏洞利用

- 2中国排名前100的IT公司

- 3iOS APP审核前注意事项和审核被拒的处理意见_苹果后台定位审核注意事项

- 4Qt常见中文乱码问题解决方法总结_qt 中文乱码

- 5机器学习集成模型学习——投票集成Voting(二)_基于投票机制的集成模型

- 6安全防御------Dos攻击

- 7iOS - iOS8.0 至 iOS15.0 版本变化_ios14 workspace settings

- 8性能优化:使用SparseArray和ArrayMap替代HashMap?_比hashmap更快的map

- 9解决 MySQL 5.7 修改密码报错:Your password does not satisfy the current policy requirements._failed! error: your password does not satisfy the

- 10ElasticSearch 复合搜索与过滤API_es api过滤索引

当前位置: article > 正文

用FPGA设计呼吸灯_fpga呼吸灯bram

作者:我家自动化 | 2024-07-05 22:49:11

赞

踩

fpga呼吸灯bram

呼吸灯介绍:

呼吸灯是指灯能够像人的呼吸一样,实现由暗到亮或由亮到暗的变化,通常用于消息提示功能,或者作为系统正在运行的提示。

呼吸灯原理:

通过脉冲宽度调制(PWM)实现,即通过调节占空比来对模拟信号电平进行数字编码,进而控制高电平时间

实验目的:用一个按键可以开关控制呼吸灯的呼吸与停止

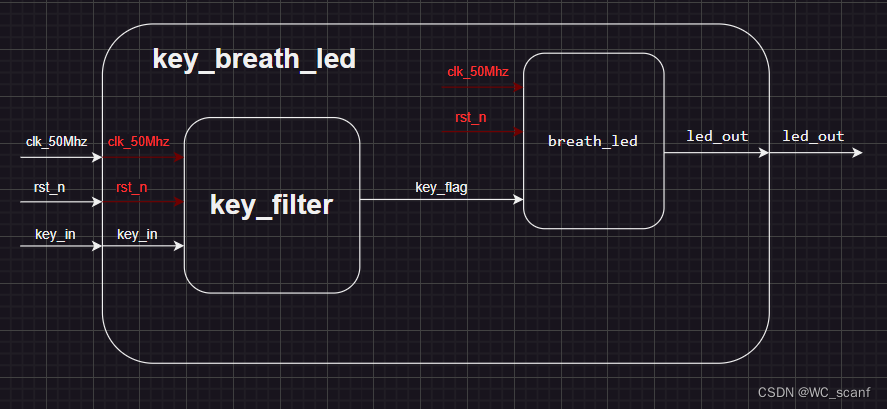

模块框图:

breath_led 模块代码 (该代码参考了野火的呼吸灯代码)

链接:16. 呼吸灯 — [野火]FPGA Verilog开发实战指南——基于Altera EP4CE10 征途Pro开发板 文档 (embedfire.com)

-

- module breath_led

- (

- input wire clk_50mhz , //系统时钟50Mhz

- input wire rst_n , //全局复位

- input wire led_flag , //输入信号,一个高电平周期

- output reg led_out //输出信号,控制led灯

- );

-

- parameter CNT_1US_MAX = 6'd49 ;

- parameter CNT_1MS_MAX = 10'd999 ;

- parameter CNT_1S_MAX = 10'd999 ;

-

-

- reg [5:0] cnt_1us ;

- reg [9:0] cnt_1ms ;

- reg [9:0] cnt_1s ;

- reg cnt_1s_en ;

-

- reg led_flag_h ;

-

- //把输入信号led_flag处理为电平反转信号

- always@( posedge clk_50mhz or negedge rst_n) begin

- if (rst_n==1'b0) begin

- led_flag_h <= 1'b0;

- end

- else if (led_flag == 1'b1) begin

- led_flag_h <= ~led_flag_h;

- end

- else begin

- led_flag_h <= led_flag_h;

- end

- end

-

- //cnt_1us:1us计数器

- always@(posedge clk_50mhz or negedge rst_n) begin

- if(rst_n == 1'b0) begin

- cnt_1us <= 6'b0;

- end

- else if(cnt_1us == CNT_1US_MAX) begin

- cnt_1us <= 6'b0;

- end

- else begin

- cnt_1us <= cnt_1us + 1'b1;

- end

-

- end

-

-

- //cnt_1ms:1ms计数器

- always@(posedge clk_50mhz or negedge rst_n) begin

- if(rst_n == 1'b0) begin

- cnt_1ms <= 10'b0;

- end

- else if(cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX) begin

- cnt_1ms <= 10'b0;

- end

- else if(cnt_1us == CNT_1US_MAX) begin

- cnt_1ms <= cnt_1ms + 1'b1;

- end

- end

-

-

- //cnt_1s:1s计数器

- always@(posedge clk_50mhz or negedge rst_n) begin

- if(rst_n == 1'b0) begin

- cnt_1s <= 10'b0;

- end

- else if(cnt_1s == CNT_1S_MAX && cnt_1ms == CNT_1MS_MAX

- && cnt_1us == CNT_1US_MAX) begin

- cnt_1s <= 10'b0;

- end

- else if(cnt_1ms == CNT_1MS_MAX && cnt_1us == CNT_1US_MAX) begin

- cnt_1s <= cnt_1s + 1'b1;

- end

- end

-

-

- //cnt_1s_en:1s计数器使能信号

- always@(posedge clk_50mhz or negedge rst_n) begin

- if(rst_n == 1'b0) begin

- cnt_1s_en <= 1'b0;

- end

- else if(cnt_1s == CNT_1S_MAX && cnt_1ms == CNT_1MS_MAX

- && cnt_1us == CNT_1US_MAX) begin

- cnt_1s_en <= ~cnt_1s_en;

- end

-

- end

-

-

- //led_out:输出信号连接到外部的led灯

- always@(posedge clk_50mhz or negedge rst_n) begin

- if(rst_n == 1'b0) begin

- led_out <= 1'b0;

- end

- else if(led_flag_h == 1'b1) begin

- led_out <= 1'b0;

- end

- else if((cnt_1s_en == 1'b1 && cnt_1ms < cnt_1s) ||

- (cnt_1s_en == 1'b0 && cnt_1ms > cnt_1s)) begin

- led_out <= 1'b0;

- end

- else begin

- led_out <= 1'b1;

- end

-

- end

-

-

- endmodule

key_filter模块代码,见我的这一篇文章 :用FPGA设计软件按键消抖-CSDN博客

key_breath_led 模块代码

- module key_breath_led (

- input wire clk_50mhz , //系统时钟50Mhz

- input wire rst_n , //全局复位

- input wire key_in , //按键输入信号

- output wire led_out //输出信号,控制led灯

-

- );

-

-

- wire key_flag;

-

-

- key_filter key_filter_inst

- (

- .clk_50mhz (clk_50mhz) , //系统时钟50Mhz

- .rst_n (rst_n ) , //全局复位

- .key_in (key_in ) , //按键输入信号

-

- .key_flag (key_flag ) //key_flag为1时表示消抖后检测到按键被按下

- //key_flag为0时表示没有检测到按键被按下

- );

-

-

- breath_led breath_led_inst

- (

- .clk_50mhz (clk_50mhz) , //系统时钟50Mhz

- .rst_n (rst_n ) , //全局复位

- .led_flag (key_flag ) , //输入信号,一个高电平周期

- .led_out (led_out ) //输出信号,控制led灯

- );

-

-

- endmodule //key_breath_led

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/我家自动化/article/detail/791164

推荐阅读

相关标签