- 1风控图算法之中心性算法(小数据集Python版)

- 2【项目】仿牛客网社区开发 第8章 项目发布与总结 5 常见面试题_仿牛客论坛项目面试题

- 3【建议收藏】Android面试必备:掌握常见题型和答题技巧_安卓开发面试问题回答技巧

- 4Java语言学习总结 高级篇 ArrayList类的创建和使用_编程建立一字符串对列(arraylist),依次添加字符串("one"), ,"three","fo

- 52024年最新Python Web开发从入门到放弃_pythonweb开发需要学什么(1),2024年最新面试必问的几大问题_python web技术栈

- 6华为OD机试C卷-- 结队编程(Java & JS & Python & C)_python 某部门计划通过结队编程来进行项目开发

- 7C语言力扣刷题1——最长回文字串[双指针]_力扣最长回文子串c语言

- 8Github 2024-06-27开源项目日报Top10

- 9python与excel结合-python3与Excel的完美结合

- 10VSCode常用技巧_vscode parameter

FPGA学习入门:(二)Verilog基础语法_fpga实例化和调用

赞

踩

FPGA学习入门:(二)Verilog基础语法

Verilog的逻辑值

逻辑 0:表示低电平,也就是对应我们电路的 GND;

逻辑 1:表示高电平,也就是对应我们电路的 VCC;

逻辑 X:表示未知,有可能是高电平,也有可能是低电平;

逻辑 Z:表示高阻态,外部没有激励信号是一个悬空状态。

数据类型

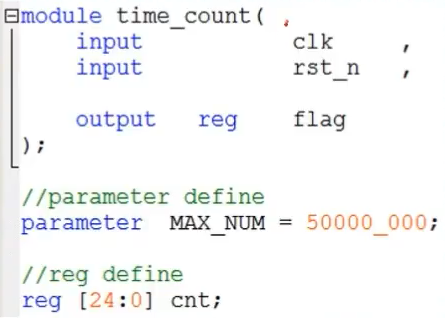

1.寄存器类型:最常用的就是 reg 类型,默认初始值为不定值x,它只能在 always 语句和 initial 语句中被赋值。

//reg define

reg [31:0] delay_cnt; //延时计数器

reg key_flag ; //按键标志

- 1

- 2

- 3

2.线网类型:表示 Verilog 结构化元件(例如门)之间的物理连线。线网类型的变量不能储存值,它的值是由驱动它的元件所决定的。常使用 tri 和 wire类型。

//wire define

wire data_en; //数据使能信号

wire [7:0] data ; //数据

- 1

- 2

- 3

3.参数类型:参数类型是一个常量,用parameter定义

//parameter define

parameter DATA_WIDTH = 8; //数据位宽为 8 位

- 1

- 2

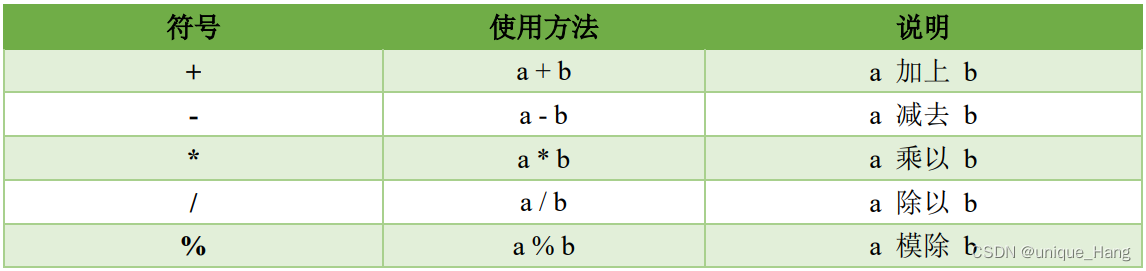

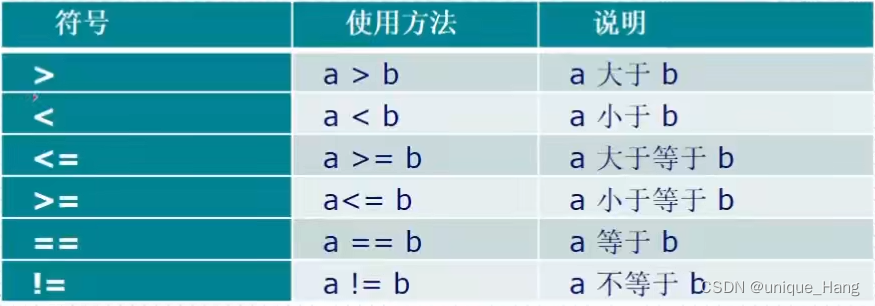

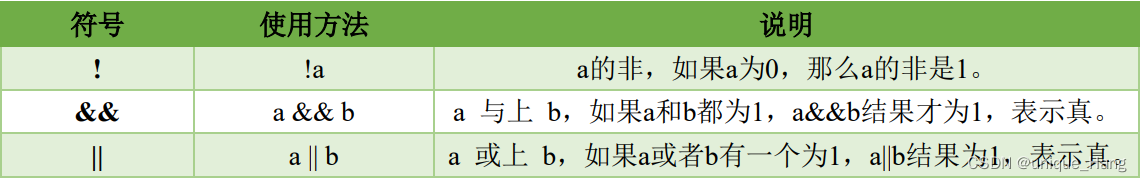

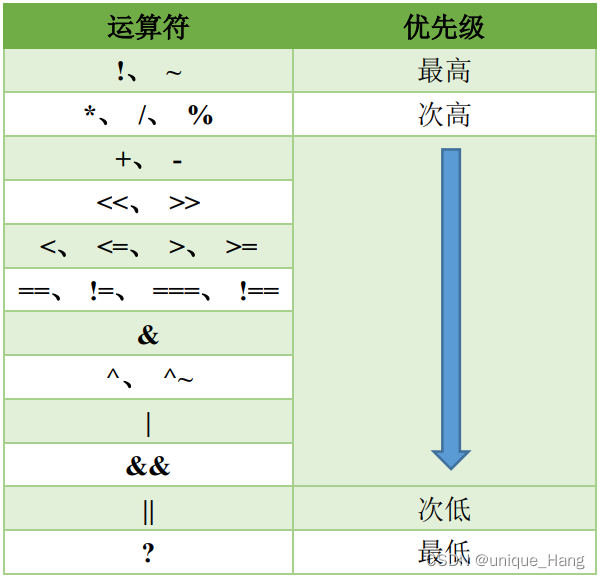

运算符

1.算术运算符

2.关系运算符

3.逻辑运算符

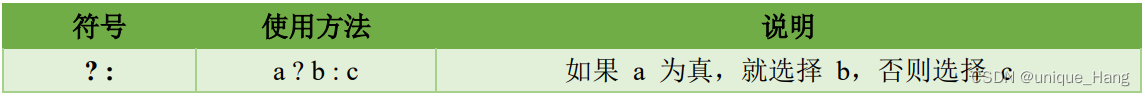

4.条件运算符

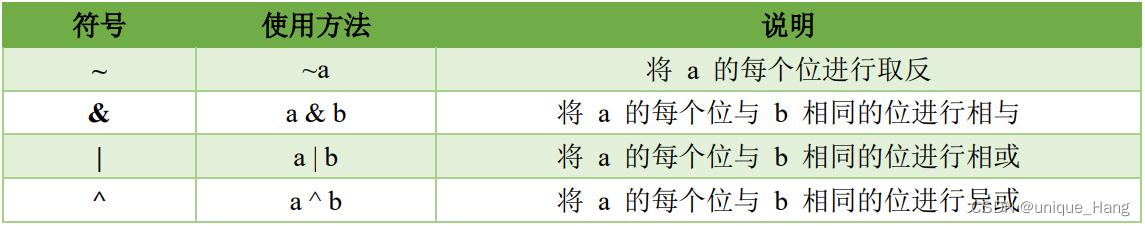

5.位运算符

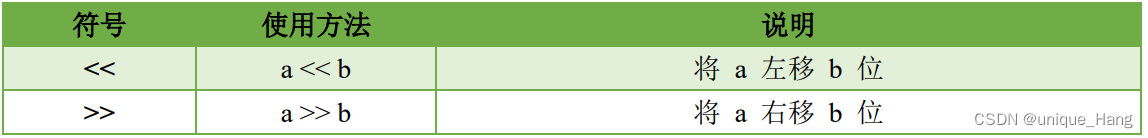

6.移位运算符

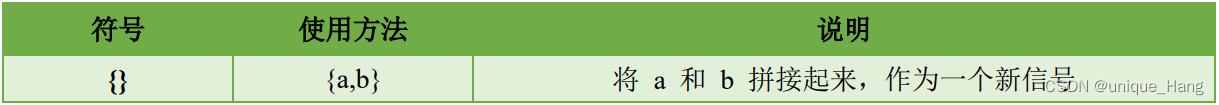

7.拼接运算符

8.运算符的优先级

常用语法

程序框架

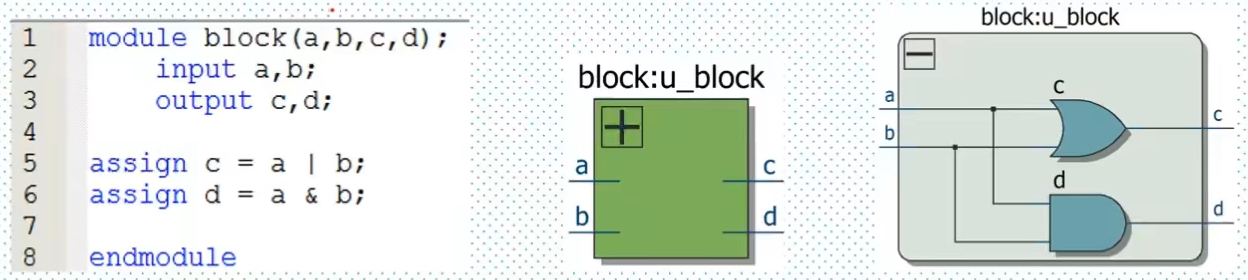

Verilog的基础单元是模块(block),

功能定义部分有三种方法:

1.assign语句:描述组合逻辑

2.always语句:描述组合/时序逻辑

3.例化实例元件

上述三种逻辑功能是并行的

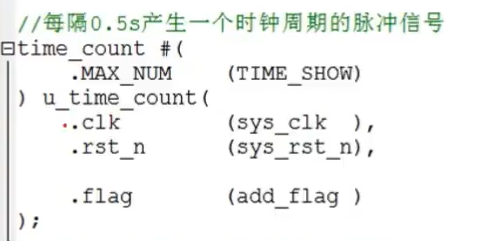

模块调用:

写一个模块

将模块实例化,将输入输出引脚连接到对应位置

赋值语句

在描述组合逻辑的always块中用阻塞赋值=,综合成组合逻辑的电路结构;

在描述时序逻辑的always块中用非阻塞赋值<=,综合成时序逻辑的电路结构;

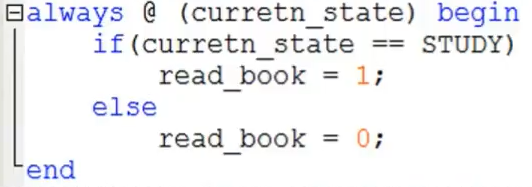

条件语句

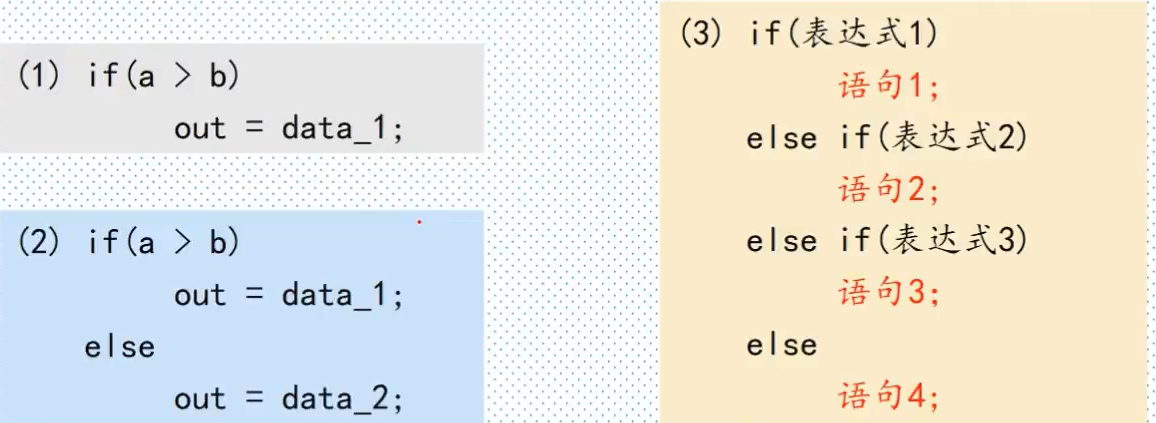

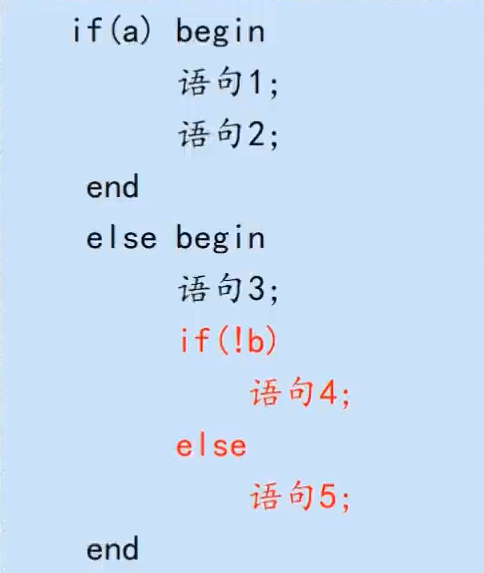

if_else语句

if和else后面的操作语句可以用begin和end包含多个语句。

注意:

1、允许一定形式的简写,如:

if(a)等同于if(a==1):

if(!a)等同于if(a!=1);

2、if语句对表达式的值进行判断,若为0,x,z,则按假处理,若为1,按真处理。

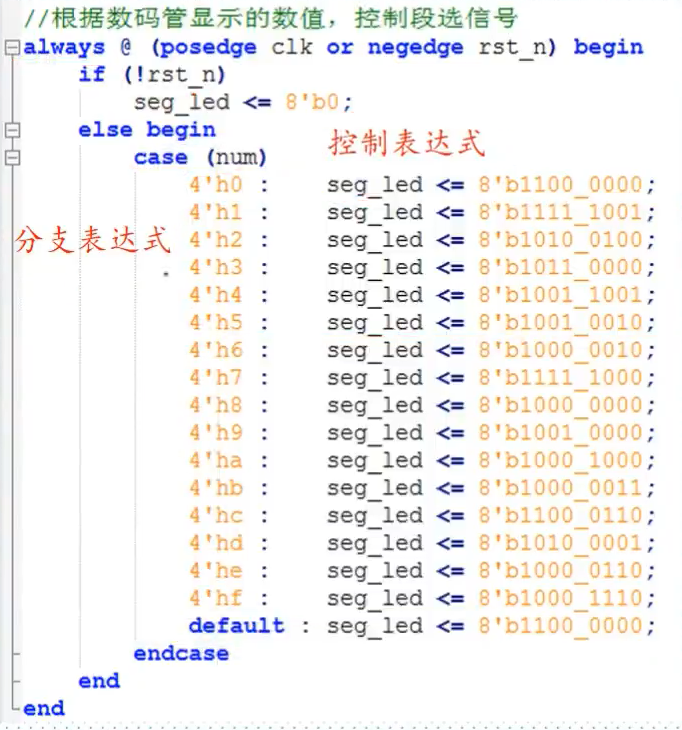

case语句(多分支选择语句)

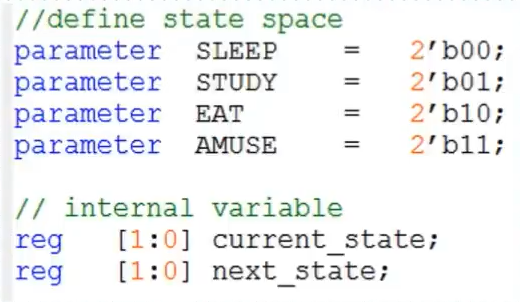

状态机

状态机(State Machine)指在有限个状态之间按一定规律转换的时序电路。

状态机设置的四段论:

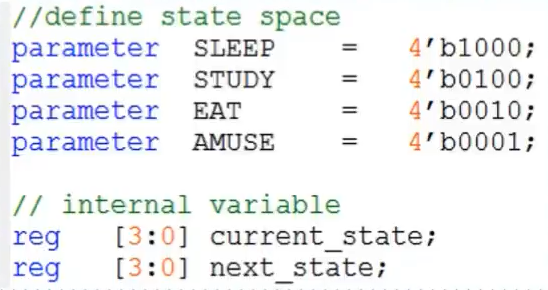

1. 状态空间定义

独热码:每个状态只有一个寄存器置位,译码逻辑简单

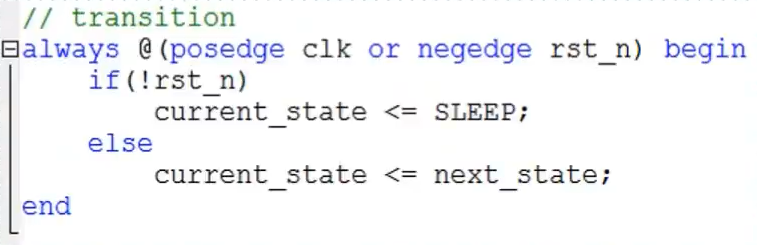

2. 状态跳转

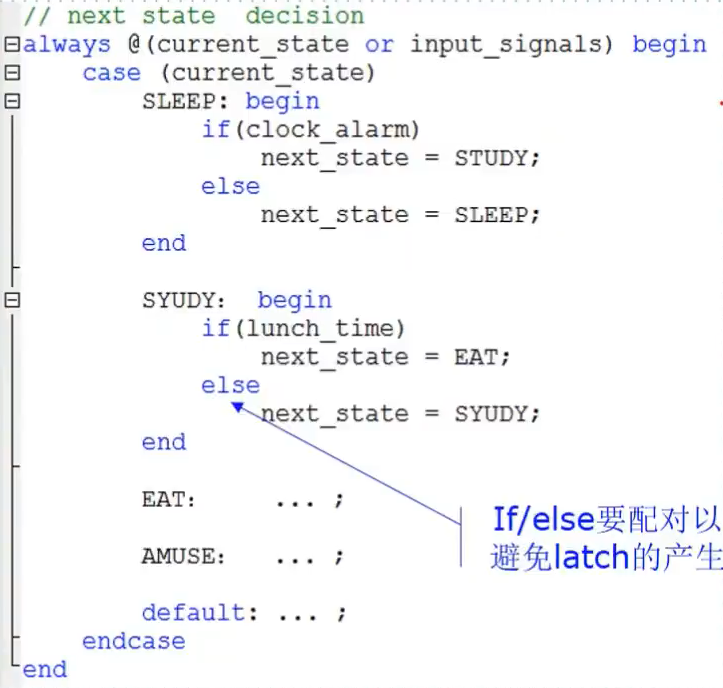

3. 下个状态判断

4. 各个状态下的动作