热门标签

热门文章

- 1Vue3+TS项目,eslint、prettier安装配置_vue3 ts 安装eslint

- 2Spring框架的学习心得_spring框架学习心得

- 3python简单的人脸识别_pycharm人脸识别源码

- 4「1024 程序员节」各大公司和程序员们都是怎么过的?你都做了哪些计划或安排?_程序员节日策划方案

- 5基于微信小程序的漫画阅读系统设计与实现

- 6用Python求数学题中阴影部分面积_python编写程序,求出图5_python 根据照片算阴影面积

- 7kali 安装 RabbitMQ_kali rabbitmq安装

- 8Python-正则表达式compile函数+常用表达式_compile正则

- 9Python爬虫实战(四):利用代理IP爬取某瓣电影排行榜并写入Excel(附上完整源码)_ip代理

- 102024年最新版68道Redis面试题,20000字干货,赶紧收藏起来备用!_redis面试问题

当前位置: article > 正文

基于FPGA的累加器及数码管显示VHDL代码Quartus仿真_quarters中如何和fpga的数码管结合起来

作者:你好赵伟 | 2024-06-20 04:41:10

赞

踩

quarters中如何和fpga的数码管结合起来

名称:基于FPGA的累加器及数码管显示VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

累加器及数码管显示

1、可以通过按键输入1~9

2、数字输入后进行累加,将累加结果显示在数码管

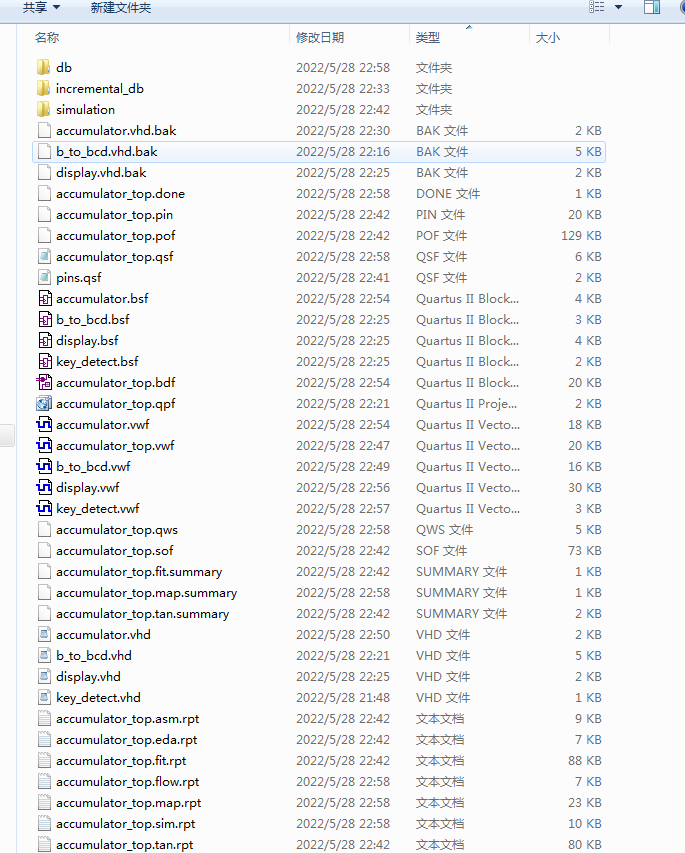

1. 工程文件

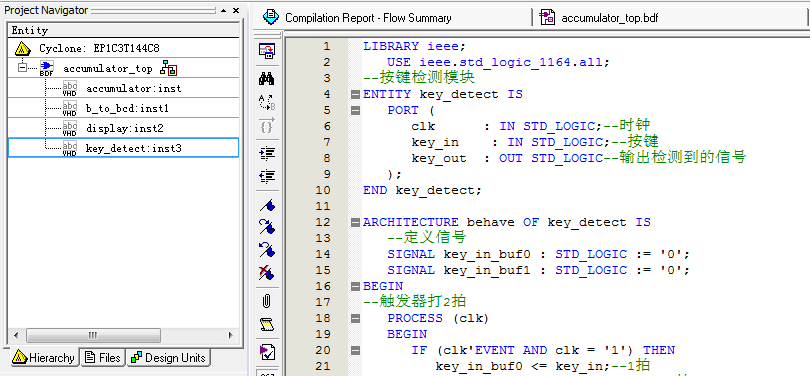

2. 程序文件

3. 程序编译

4. 管脚分配

时钟接1000Hz左右

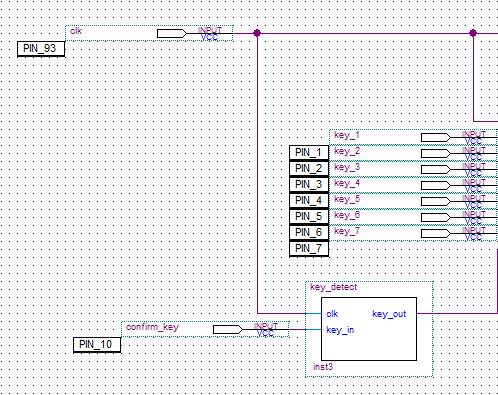

5. RTL图

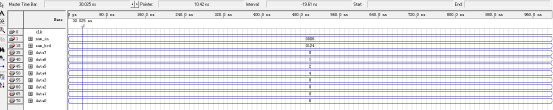

6. 仿真图

整体仿真图

按键模块

累加模块

BCD转换模块

显示模块

![]()

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --累加显示模块 ENTITY accumulator IS PORT ( clk : IN STD_LOGIC;--时钟 key_1 : IN STD_LOGIC;--按键1 key_2 : IN STD_LOGIC;--按键2 key_3 : IN STD_LOGIC;--按键3 key_4 : IN STD_LOGIC;--按键4 key_5 : IN STD_LOGIC;--按键5 key_6 : IN STD_LOGIC;--按键6 key_7 : IN STD_LOGIC;--按键7 key_conf : IN STD_LOGIC;--确认按键 num_in : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--加数 sum : OUT STD_LOGIC_VECTOR(15 DOWNTO 0)--累加和 ); END accumulator; ARCHITECTURE behave OF accumulator IS --定义信号 SIGNAL data_in : STD_LOGIC_VECTOR(15 DOWNTO 0) := x"0000";--输入加数 SIGNAL data_sum : STD_LOGIC_VECTOR(15 DOWNTO 0) := x"0000";--累加和 BEGIN PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN if(key_1='1')then--按键1 data_in<=x"0001";--输入1 elsif(key_2='1')then--按键2 data_in<=x"0002";--输入2 elsif(key_3='1')then--按键3 data_in<=x"0003";--输入3 elsif(key_4='1')then--按键4 data_in<=x"0004";--输入4 elsif(key_5='1')then--按键5 data_in<=x"0005";--输入5 elsif(key_6='1')then--按键6 data_in<=x"0006";--输入6 elsif(key_7='1')then--按键7 data_in<=x"0007";--输入7 end if; END IF; END PROCESS; PROCESS (clk) BEGIN IF (clk'EVENT AND clk = '1') THEN if(key_conf='1')then--确认按键 data_sum<=data_sum+data_in;--累加 end if; END IF; END PROCESS; num_in<=data_in; sum<=data_sum; END behave;

源代码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/738637

推荐阅读

相关标签