热门标签

热门文章

- 1em算法详细例子及推导_EM算法详解

- 2绝赞!B站投币20W+的Redis/MongoDB/Mysql性能优化宝藏库,我先磕了

- 3Flutter中的Firebase:如何使用Flutter连接Firebase数据库_firebase flutter

- 4深入理解Transformer架构的编码器-解码器结构_解码器 自注意力

- 5VBA获取某文件夹下所有文件和子文件目录的文件_excel vba 列出目录下所有子目录和文件

- 6大数据面试题之Presto[Trino](1)

- 7训练自己的GPT2-Chinese模型_gpt2模型下载

- 8关于抽象类和接口的易错概念选择题(JAVA基础)_在typescript中,关于抽象类和接口说法错误的是

- 9java反序列之CC1_java反序列化 cc1

- 10Kafka原生API使用Java代码-生产者-分区策略-默认分区策略&轮询分区策略_java kafka 多分区代码

当前位置: article > 正文

pcie读写ddr_一文详解PCIe内存空间到AXI内存空间的转换

作者:从前慢现在也慢 | 2024-06-15 07:36:14

赞

踩

pcie读主板内存

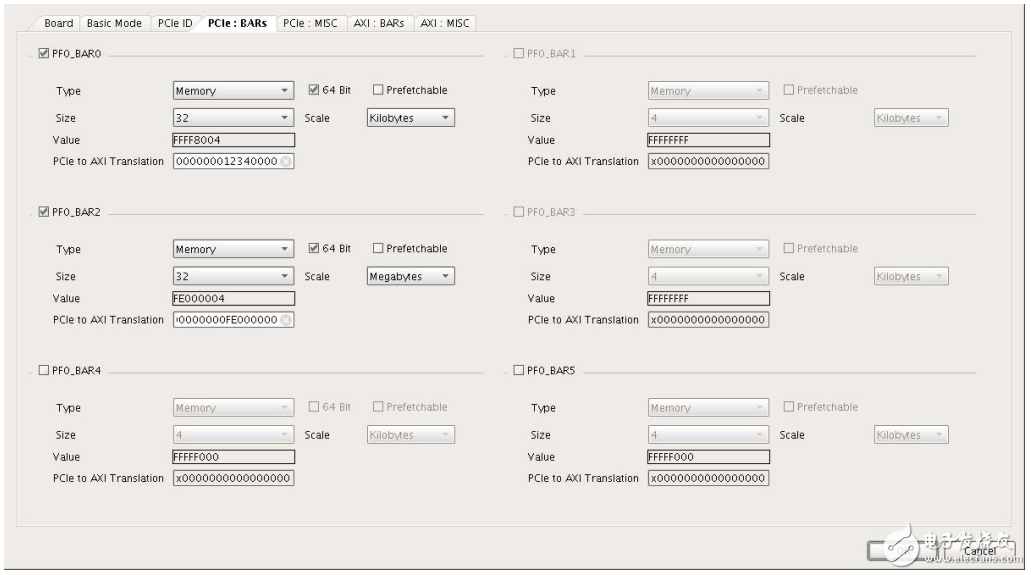

UltraScale系列芯片包含PCIe的Gen3 Integrated Block IP核在内的多种不同功能的IP核都会有一页设置为PCIe:BARs,设置IP核的Base address register 的相关参数,如图1所示:

图1 PCIe:BARs 配置图

一般来说在FPGA中使用PCIe核都是Endpoint mode,我们的PC主机端是Rootpoint mode,一般会有一个Root Complex的混合管理器,来管理接入PCIe总线的端点设备。对于PC机来说,当PC机识别该PCIe设备后便会识别到BAR n相对应的基地址和地址空间(不过该基地址是PC机的Root Complex主动分配的,还是PCIe设备内部固定的还有疑问)。设别基本配置信息后,PC机便可以对PCIe的内存空间进行读写操作了。

而PCIe IP核本身能够引出AXI总线接口,该AXI接口是memory map 型的,所以就肯定存在自己的地址空间,本文所提的PCIe to AXI Translation便是PCIe的地址空间到AXI的地址空间的转换。

这里就图1中的BAR0来说明下PCIe to AXI Translation的转换过程。BAR0的配置为:64bit数据位宽、32kilobytes地址范围、PCIe to AXI Translation为0x0000000012340000。此时的PCIe IP核的BAR0是拓展连接到外部的AXI总线的,该总线连接到另外一个DDR4 MIG IP核,如图2所示。图中

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/721423

推荐阅读

相关标签