热门标签

热门文章

- 1学会充分运用AI的自然语言理解能力_ai如何判案,利用自然语言能力去理解问题文本和语法

- 22020 年前端技术发展盘点_前端前沿思潮和技术

- 3libcurl简介及其编程应用

- 4使用ChatGPT进行SCI英文论文润色的最佳指令指南!_chatgpt润色sci

- 5JDK各个版本的更新特性_javajdk更新

- 6蓝桥杯欲伸手CTF?有多远爬多远_蓝桥杯ctf都需要会么

- 7红队攻防渗透技术实战流程:中间件安全:IIS&NGINX&APACHE&TOMCAT

- 8Selenium : error sending request for url.... 10054 问题_exception managing chrome: error sending request f

- 9智慧城市中的数据力量:大数据与AI的应用

- 10【Hive】如何对Hive表小文件进行合并_hive.merge.smallfiles.avgsize

当前位置: article > 正文

基于FPGA的交通灯设计Verilog代码ISE仿真_十字路口简易信号灯verilog测试代码

作者:不正经 | 2024-06-16 04:24:32

赞

踩

十字路口简易信号灯verilog测试代码

名称:基于FPGA的交通灯设计Verilog代码ISE仿真(文末获取)

软件:ISE

语言:Verilog

代码功能:

1、实现一个十字路口交通灯,每条路有红绿黄三色信号灯

2、使用数码管显示倒计时

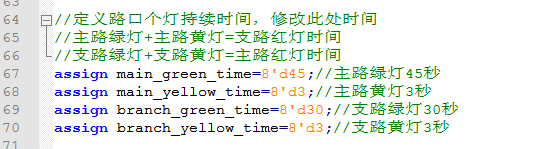

3、可通过代码修改通行时间

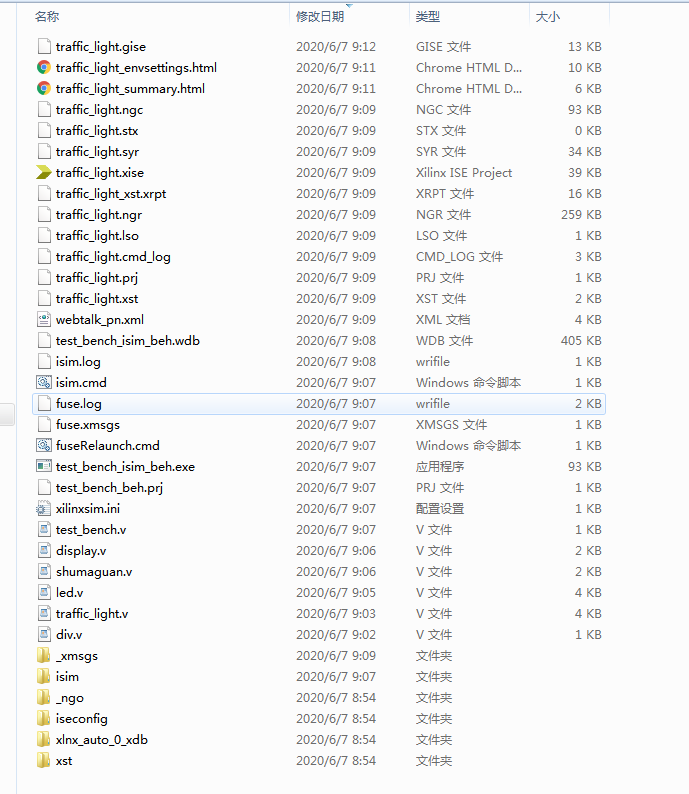

1. 工程文件

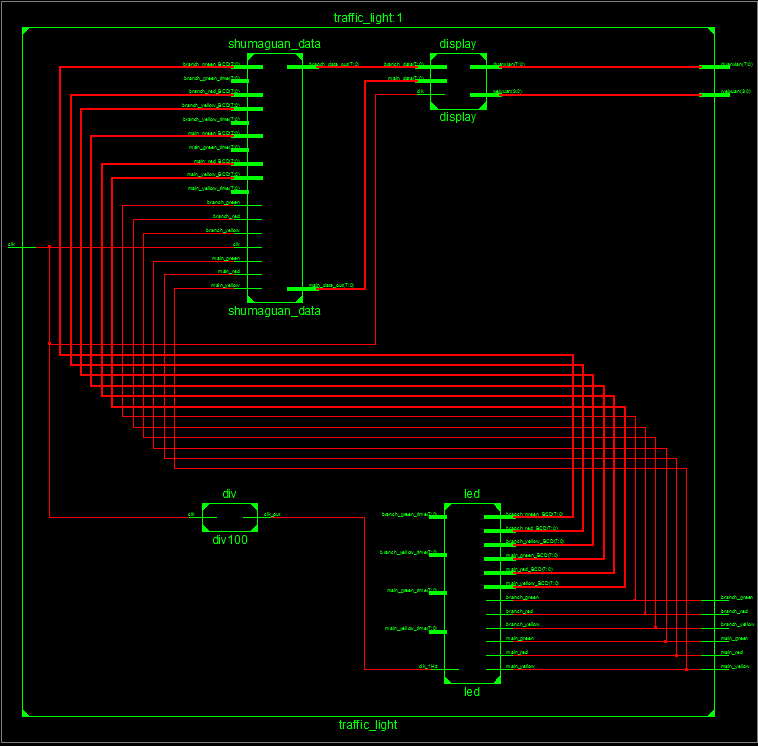

2. 程序文件

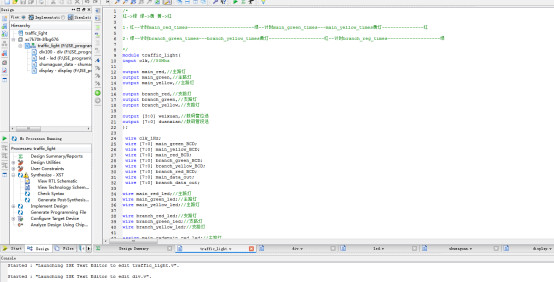

3. 程序编译

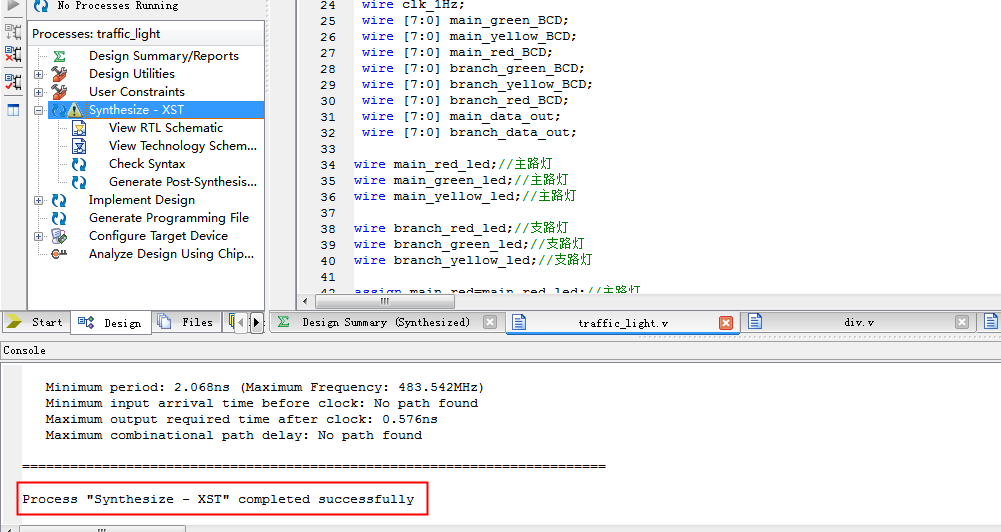

4. RTL图

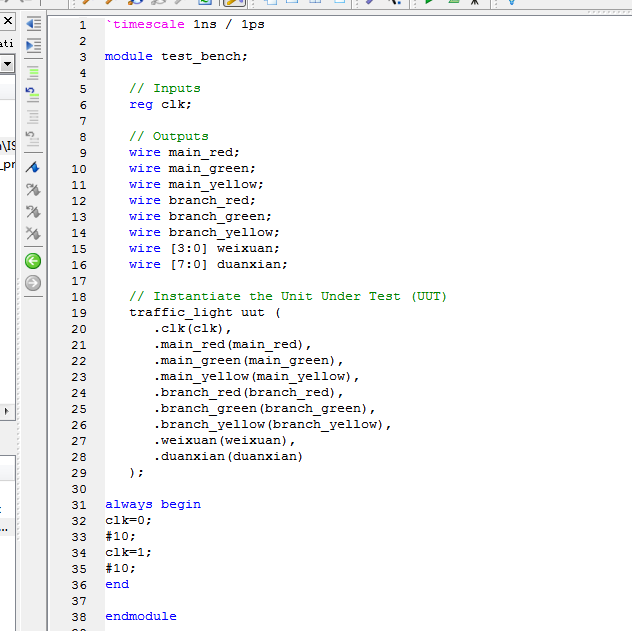

5. Testbench

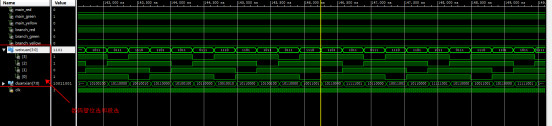

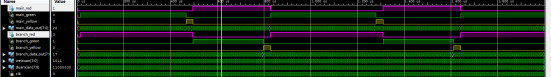

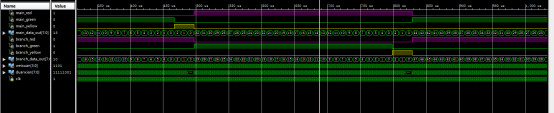

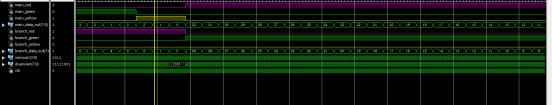

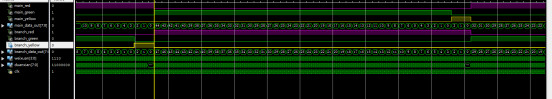

6. 仿真图

代码中定义了主路红灯33秒,绿灯45秒,黄灯3秒

支路红灯48秒,绿灯30秒,黄灯3秒

仿真图对应如下,下图中用不同颜色标记了不同灯

部分代码展示:

module display ( input clk, input [7:0] main_data,//主路,两个数码管 input [7:0] branch_data,//支路,两个数码管 output reg [3:0] weixuan,//位选,高电平亮 output reg [7:0] duanxian//段选,高电平亮 ); wire [3:0] main_data_ten;//十位 wire [3:0] main_data_one;//个位 wire [3:0] branch_data_ten;//十位 wire [3:0] branch_data_one;//个位 assign main_data_ten=main_data/10;//十位 assign main_data_one=main_data%10;//个位 assign branch_data_ten=branch_data/10;//十位 assign branch_data_one=branch_data%10;//个位 reg[15:0]jishu='d0; always@(posedge clk) begin jishu<=jishu+16'd1; end reg [3:0] display_data=4'd0; always@(posedge clk) begin case(jishu[5:4])//显示(仿真减小为[5:4]) 2'd0:display_data<=branch_data_one; 2'd1:display_data<=branch_data_ten; 2'd2:display_data<=main_data_one; 2'd3:display_data<=main_data_ten; default:; endcase end always@(posedge clk) begin case(jishu[5:4])//位选,低亮(仿真减小为[5:4]) 2'd0: weixuan<=4'b1110; 2'd1: weixuan<=4'b1101; 2'd2: weixuan<=4'b1011; 2'd3: weixuan<=4'b0111; default:weixuan<=4'b0111; endcase case(display_data)//段选,低亮 0 : duanxian= (8'hc0); 1 : duanxian= (8'hf9); 2 : duanxian= (8'ha4); 3 : duanxian= (8'hb0); 4 : duanxian= (8'h99); 5 : duanxian= (8'h92); 6 : duanxian= (8'h82); 7 : duanxian= (8'hf8); 8 : duanxian= (8'h80); 9 : duanxian= (8'h90); endcase end endmodule

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/725127

推荐阅读

相关标签