热门标签

热门文章

- 1网络资源模板--基于 Android Studio 实现的水果商城App_网络资源模板--基于android studio 水果商城仅需

- 2python 堆_python堆有什么用

- 3【数据库系统】数据库系统概论====第四章 数据库安全性_数据库系统为什么有自己的身份认证和访问控制机制,而不直接采用操作系统提供的这

- 42022-DISCO-分布式激光雷达协同SLAM框架_disco-slam

- 5贝叶斯③——Python实现贝叶斯文本分类(伯努利&多项式模型对比)_使用多项式朴素贝叶斯对给定的文本进行分类python

- 6UnityVR游乐园笔记#003_过山车场景(结束)_unity 过山车游戏 插件

- 7AIGC系列之:升级版的Stable Diffusion之SDXL介绍_sd xl base 1.0.safetensors[31e35c80fc]

- 8基于matlab的图像去噪算法设计与实现_图像降噪研究现状

- 9[已解决]Springboot项目启动时端口被占用_springboot启动端口被占用

- 10STC89C52的四个 外部中断 基本使用方法_89c52外部中断

当前位置: article > 正文

多功能数字钟设计VHDL代码Quartus仿真_vhdl数码管显示的仿真怎么设置输入的时钟

作者:Gausst松鼠会 | 2024-06-15 10:50:43

赞

踩

vhdl数码管显示的仿真怎么设置输入的时钟

名称:多功能数字钟设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

(1)输入信号3178kh基时钟信号。

(2)具有时、分、秒计时显示功能,以-12小时循环计时。

(3)采用6位七段扫描共阴极数码显示管计时显示,并具有秒闪指示功能。(4)利用一个按键开关完成系统复位功能。

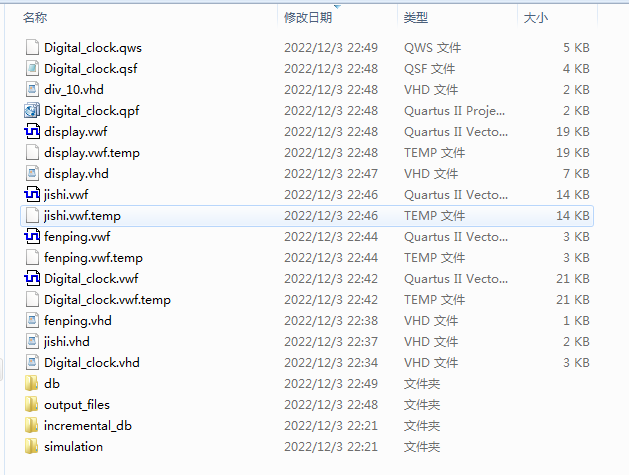

1. 工程文件

2. 程序文件

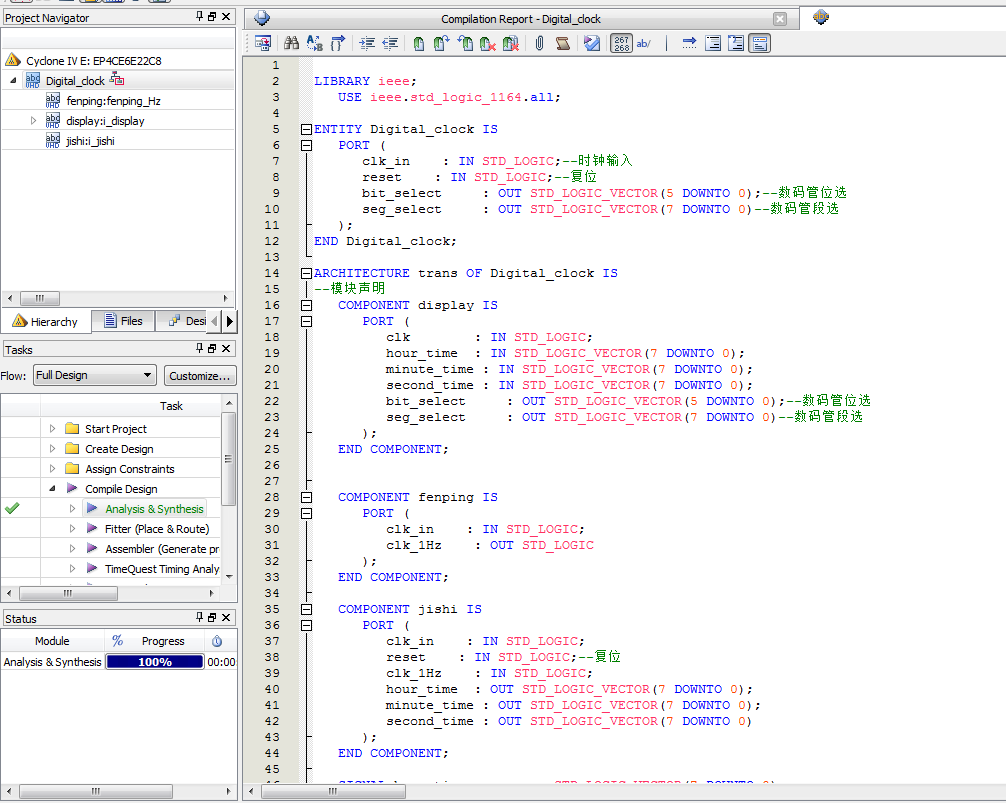

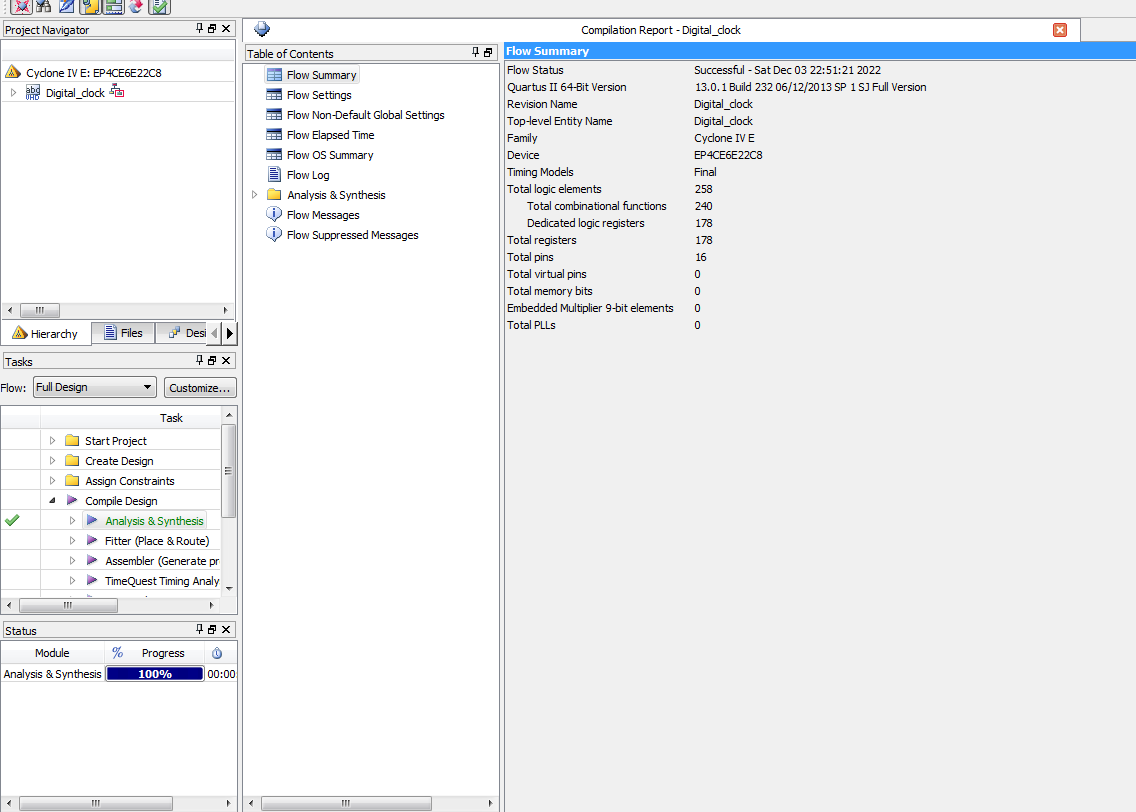

3. 程序编译

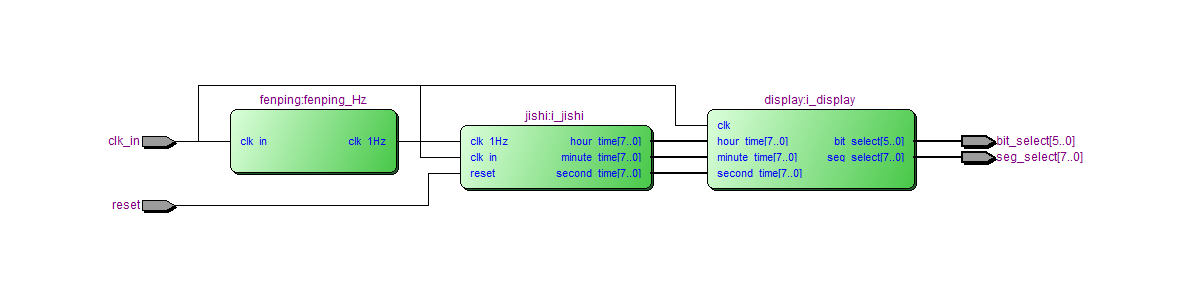

4. RTL图

5. 仿真图

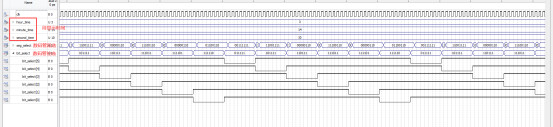

整体仿真图

分频模块

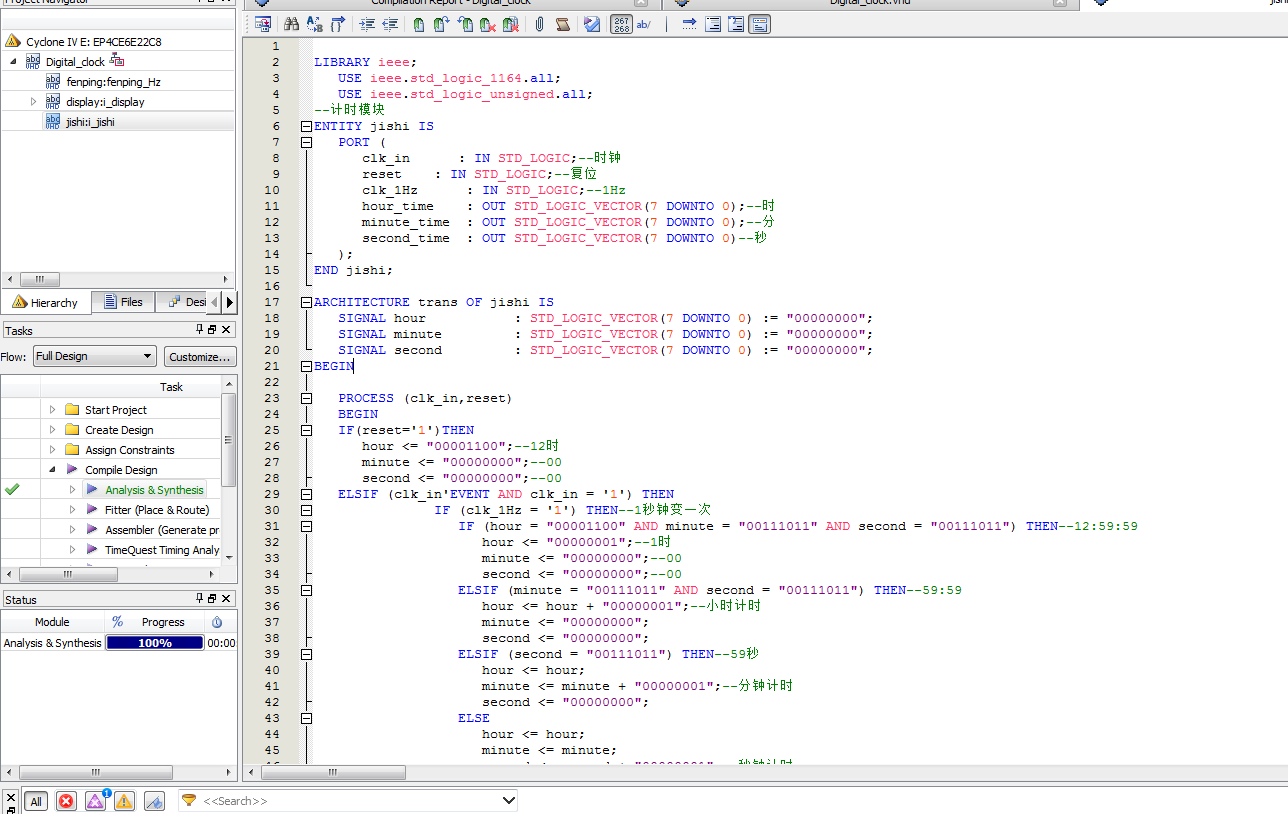

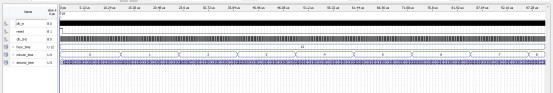

计时模块

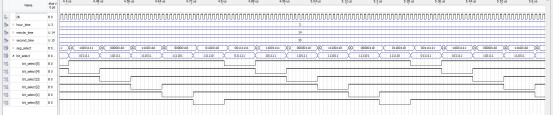

显示模块

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY Digital_clock IS PORT ( clk_in : IN STD_LOGIC;--时钟输入 reset : IN STD_LOGIC;--复位 bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END Digital_clock; ARCHITECTURE trans OF Digital_clock IS --模块声明 COMPONENT display IS PORT ( clk : IN STD_LOGIC; hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bit_select : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);--数码管位选 seg_select : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管段选 ); END COMPONENT; COMPONENT fenping IS PORT ( clk_in : IN STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; COMPONENT jishi IS PORT ( clk_in : IN STD_LOGIC; reset : IN STD_LOGIC;--复位 clk_1Hz : IN STD_LOGIC; hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; SIGNAL hour_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL minute_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL second_time : STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL clk_1Hz : STD_LOGIC; BEGIN --分频到1Hz fenping_Hz : fenping PORT MAP ( clk_in => clk_in, clk_1Hz => clk_1Hz ); --计时模块 i_jishi : jishi PORT MAP ( clk_in => clk_in, reset => reset,--复位 clk_1Hz => clk_1Hz, hour_time => hour_time,--时 minute_time => minute_time,--分 second_time => second_time--秒 ); --显示模块 i_display : display PORT MAP ( clk => clk_in, hour_time => hour_time, minute_time => minute_time, second_time => second_time, bit_select =>bit_select,--数码管位选 seg_select =>seg_select--数码管段选 ); END trans;

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/722021

推荐阅读

相关标签