热门标签

热门文章

- 1ATF 页表构建代码分析_atf code分析

- 2【SpringCloud】单体商城项目拆分微服务和各个组件学习①_黑马商城项目实战(微服务架构)

- 3Windows下的应急响应思路及其基本命令_应急响应 windows 停止服务 修改参数

- 4苹果电脑玩Windows游戏怎么实现 mac想玩windows游戏怎么办 parallels desktop激活密钥 虚拟机玩游戏_mac玩windows游戏

- 5项目二 ImageNet图像识别模型与CIFAR-10_图像识别cifar-10

- 6Stable Diffusion【3D模型】:场景精细与逼真,人物表情丰富的3D大模型AWPoly3D(附模型包)_stable diffusion 3d建模

- 7【大咖解读】谢国彤:疾病预测的机器学习、深度学习和经典回归方法

- 8Pandas库qcut( )与cut( )的用法与区别_pd qcut什么意思

- 9FPGA产业发展现状及人才培养研究报告_fpga的发展现状与分析

- 10日常开发-myBatis时间段查找_mybatis between and 日期

当前位置: article > 正文

Verilog有限状态机设计

作者:运维做开发 | 2024-08-01 19:30:07

赞

踩

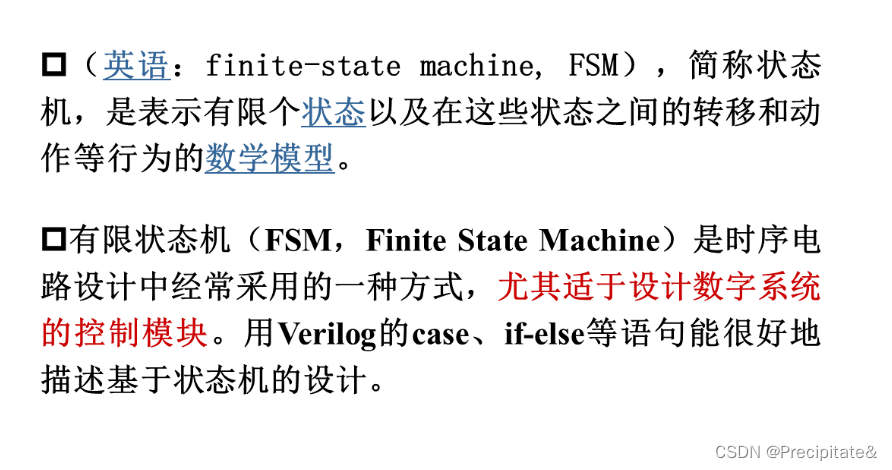

有限状态机设计

一、 什么使有限状态机

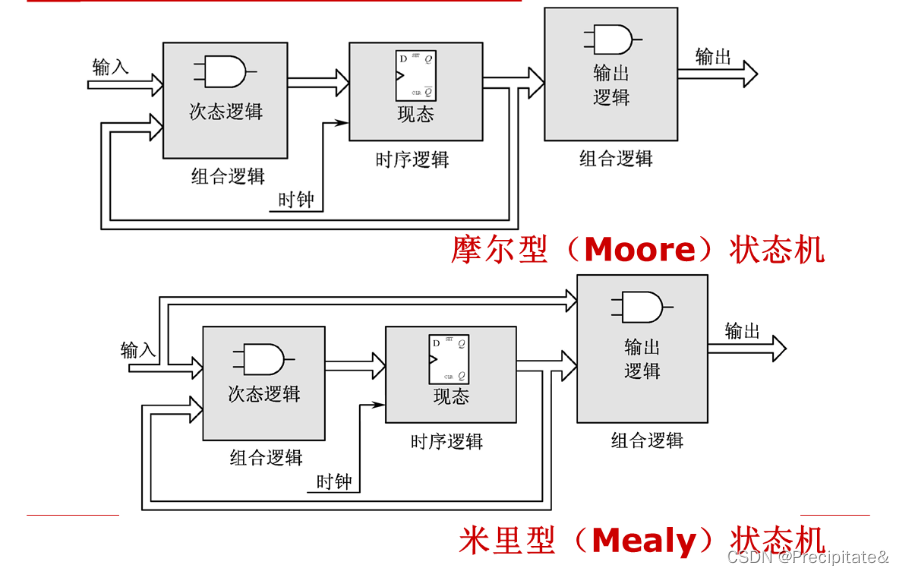

二、 有限状态机的分类

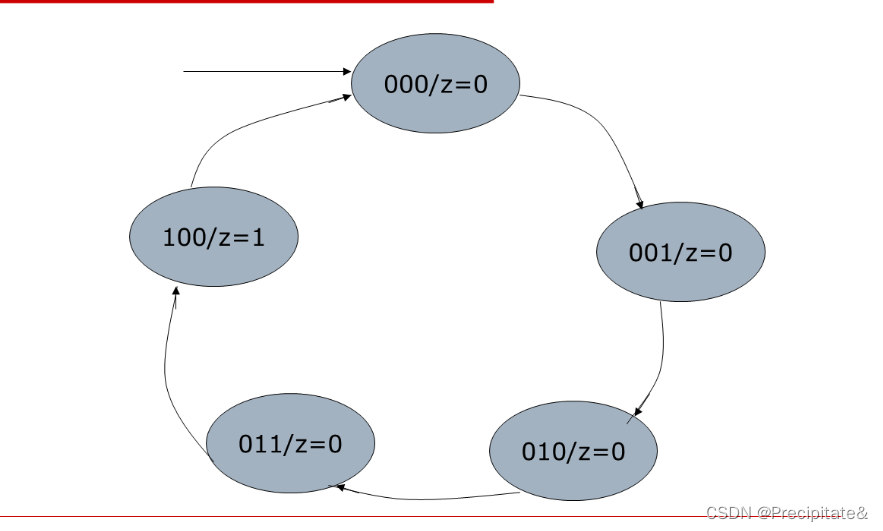

三、用状态机实现模5计数器

实现步骤:

1、状态编码

2、定义状态存储变量cs,ns

3、3个always,分别实现当前状态的更新cs、下一个状态的更新以及输出的更新。

verilog代码

- module count5(clk,z);

- input clk;

- output z;

- parameter s0=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100;//状态编码

- reg [2:0] cs,ns; //定义状态存储变量current state,next state;

- always@(posedge clk)//基于clk,当前状态的更新

- cs=ns;

- always@(cs)//基于cs,ns的更新

- begin

- case(cs)

- s0:ns=s1;

- s1:ns=s2;

- s2:ns=s3;

- s3:ns=s4;

- s4:ns=s0;

- defualt:ns=s0;

- endcase

- end

- always@(cs)//基于cs,输出z的更新

- begin

- if(cs==s4) z=1;

- else z=0;

- end

- endmodle

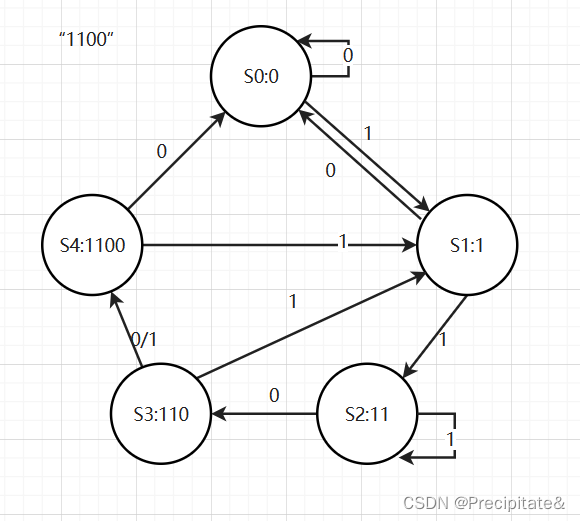

四、“101”序列检测器的Verilog描述

Verilog代码

- module sy(x,clk,clr,z);

- input x,clk,clr;

- output reg z;

- parameter s0=0,s1=1,s2=2,s3=3,s4=4;

- reg [2:0] cs,ns;

- always@(posedge clk or posedge clr)

- begin

- if(clr) cs=s0;

- eles cs=ns;

- end

- always@(cs or x)

- begin

- case(cs)

- s0:begin if(x) ns=s1;else ns=s0;end

- s1:begin if(x) ns=s2;else ns=s0;end

- s2:begin if(x) ns=s2;else ns=s3;end

- s3:begin if(x) ns=s1;else ns=s4;end

- s4:begin if(x) ns=s1;else ns=s0;end

- defualt ns=s0;

- endcase

- end

- always@(cs)

- begin

- if(cs==s4) z=1;

- else z=0;

- end

- endmodule

如果要对当前状态进行修改,如使用清零信号clr,则放在第一个always中。

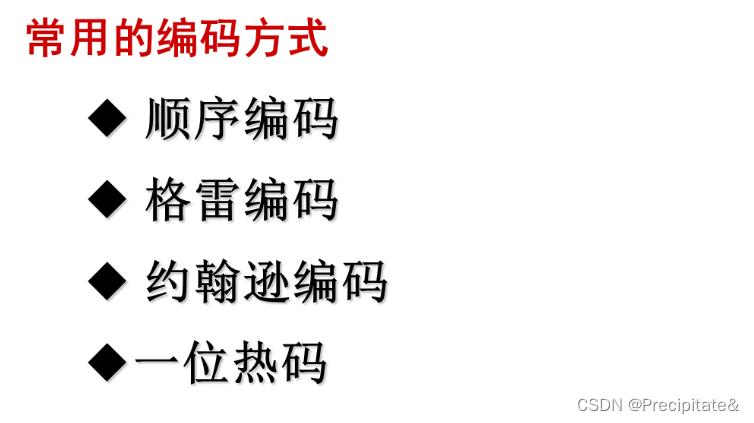

五、状态编码

后三种编码方式都是相邻编码,即相邻两个编码只有一位数字不同。

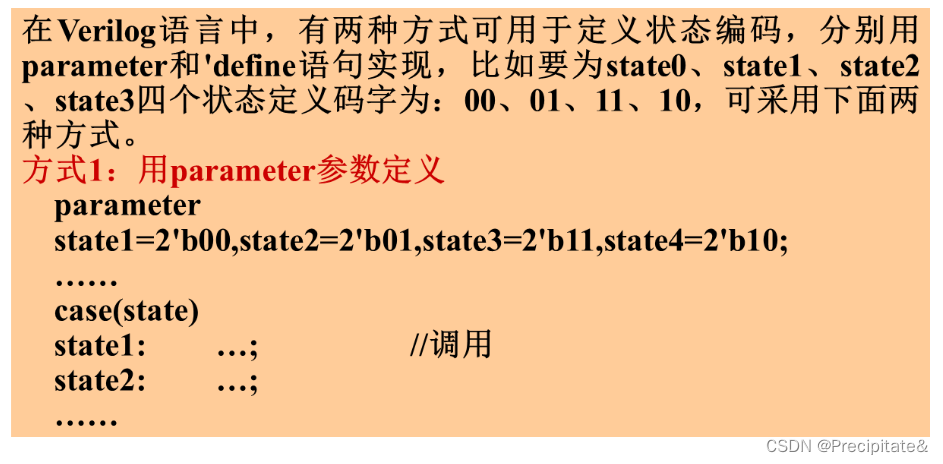

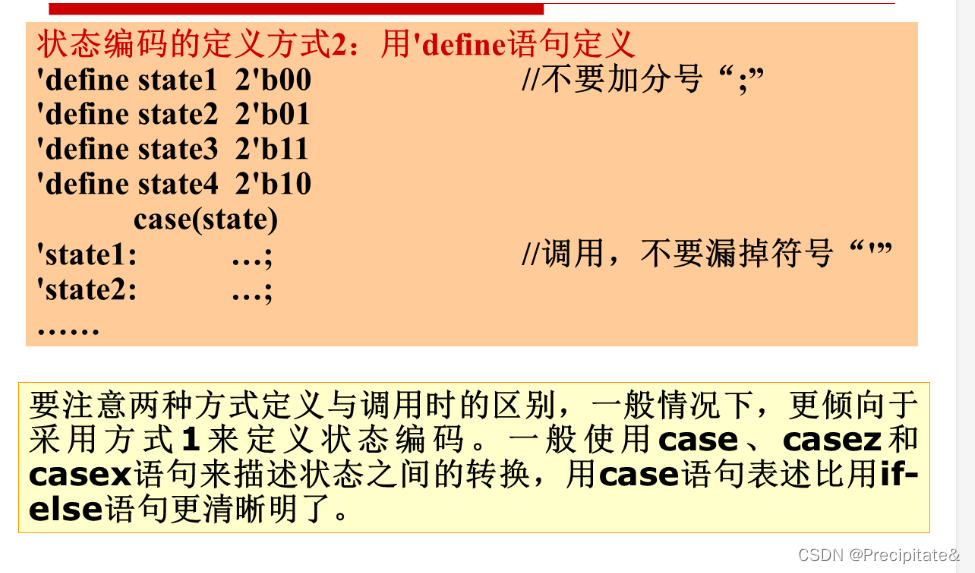

状态编码的定义

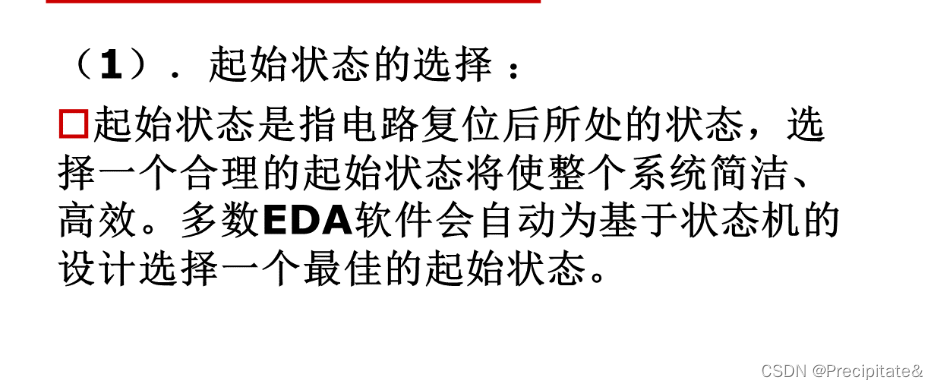

六、有限状态机的设计要点

多余状态的处理

七、用状态机设置流水灯

1、控制4个led灯从左往右顺序循坏点亮

- module sy(clk1,en,led);

- input clk1,en;//1HZ的时钟,使能开关

- output reg [3:0] led;//4个led灯

- parameter s0=0,s1=1,s2=2,s3=3;

- reg [1:0] cs,ns;

- always@(posedge clk)

- cs=ns;

- always@(cs)

- begin

- case(cs)

- s0:ns=s1;

- s1:ns=s2;

- s2:ns=s3;

- s3:ns=s0;

- default:ns=s0;

- endcase

- end

- always@(cs)

- begin

- if(`en) led=4'bz;

- else

- begin

- case(cs)

- s0:led=4'b1000;

- s1:led=4'b0100;

- s2:led=4'b0010;

- s3:led=4'b0001;

- defualt:led=4'bz;

- endcase

- end

- end

- endmolue

2、控制18个led灯从两边往中间逐个亮后全灭,再从中间往两边逐个亮后全灭,循环执行上述过程。

过程1(除全灭)一共有18/2=9个状态,过程2亦有9个状态,再加上2个全灭状态(这两个状态并不相同,因为其下一状态不是同一个状态),一共20个状态。

Verilog代码

- module sy(clk1,led,en);

- input clk1,en;

- output reg [17:0] led;

- parameter s0=0,s1=1,s2=2,s3=3,s4=4,...,s19=19;//20个状态

- reg[4:0] cs,ns;

- always@(posedge clk) cs=ns;

- always@(cs)

- begin

- case(cs)

- s0:ns=s1;

- s1:ns=s2;

- s2:ns=s3;

- ...

- s19:ns=s0;

- default:ns=s0;

- endcase

- end

- always@(cs)

- begin

- if(~en) led=18'bz;

- else

- begin

- case(cs)

- s0:led=18'b0;

- s1:led=18'100000000000000001;

- s2:led=18'b11000000000000011;

- ...

- s19:led=18'b1111111111111111;

- defualt:led=18'bz;

- endcase

- end

- end

- endmodule

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/运维做开发/article/detail/915581

推荐阅读

相关标签