- 1数据分析之机器学习(整理笔记)_《数据分析之机器学习》

- 2二叉树的存储结构

- 3【javaweb】学习日记Day12 - tlias智能管理系统 - 登录校验 JWT令牌 过滤器 拦截器 全局异常处理_tlias智能辅助系统

- 4【雷达检测】多目标情况下不同毫米波雷达恒虚警率(CA、CMLD、GO、IC、OS、ODGO、OSSO、SO、TM)-CFAR算法性能检测算法的仿真研究matlab实现_在多目标环境下ca-cfar存在更多的虚警

- 5数据结构---字典树(Tire)_tire树状结构

- 6解决gitlab限制上传大小文件的问题

- 7spring boot基于redis的分布式定时任务_springboot redistemplate处理分布式任务

- 8【Github】pull request 创建_创建pull request

- 9深度学习(二)—— TensorFlow入门

- 10最新【ES专题】ElasticSearch集群架构剖析_es集群(3),2024年最新大数据开发常见面试题知乎_es 3集群搭建

Modelsim的使用以及设计、激励文件testbench的说明_modedim激励文件

赞

踩

其实有很多可以用来做FPGA开发的软件,如Vivado、Quartus和Modelsim,但是这里向大家推荐使用modelsim是因为大家现在要做的只是简单的一个数电知识的verilog实现和仿真,所以用不到很多东西,比如一个Vivado装完就要几十个G上百个G,这对电脑的要求不低,而一个modelsim也就几百兆一个多G,且用起来也比较方便,仿真速度也快,即使是在用Vivado进行大型项目的开发,也经常关联modelsim用它进行仿真,接下来主要介绍设计文件、激励文件以及modelsim使用的方法,更加详细的使用大家可以自己在网上查找一下,非常方便。

一、设计文件

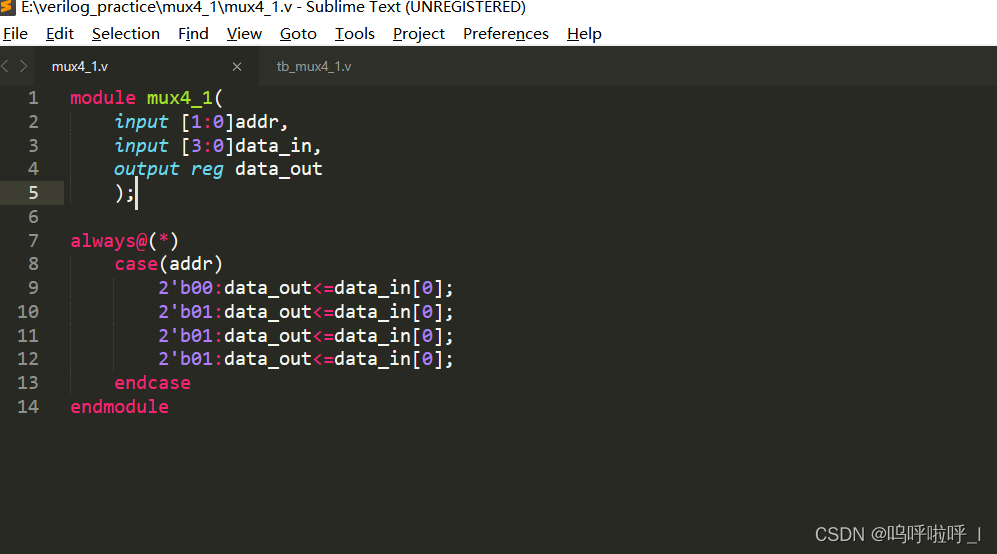

何为设计文件,就是利用Verilog实现某一特定功能的.v文件,比如实现一个选择器,那我们可以得到如下的.v文件。

module mux4_1(

input [1:0]addr,

input [3:0]data_in,

output reg data_out

);

always@(*)

case(addr)

2'b00:data_out<=data_in[0];

2'b01:data_out<=data_in[0];

2'b01:data_out<=data_in[0];

2'b01:data_out<=data_in[0];

endcase

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

二、激励文件

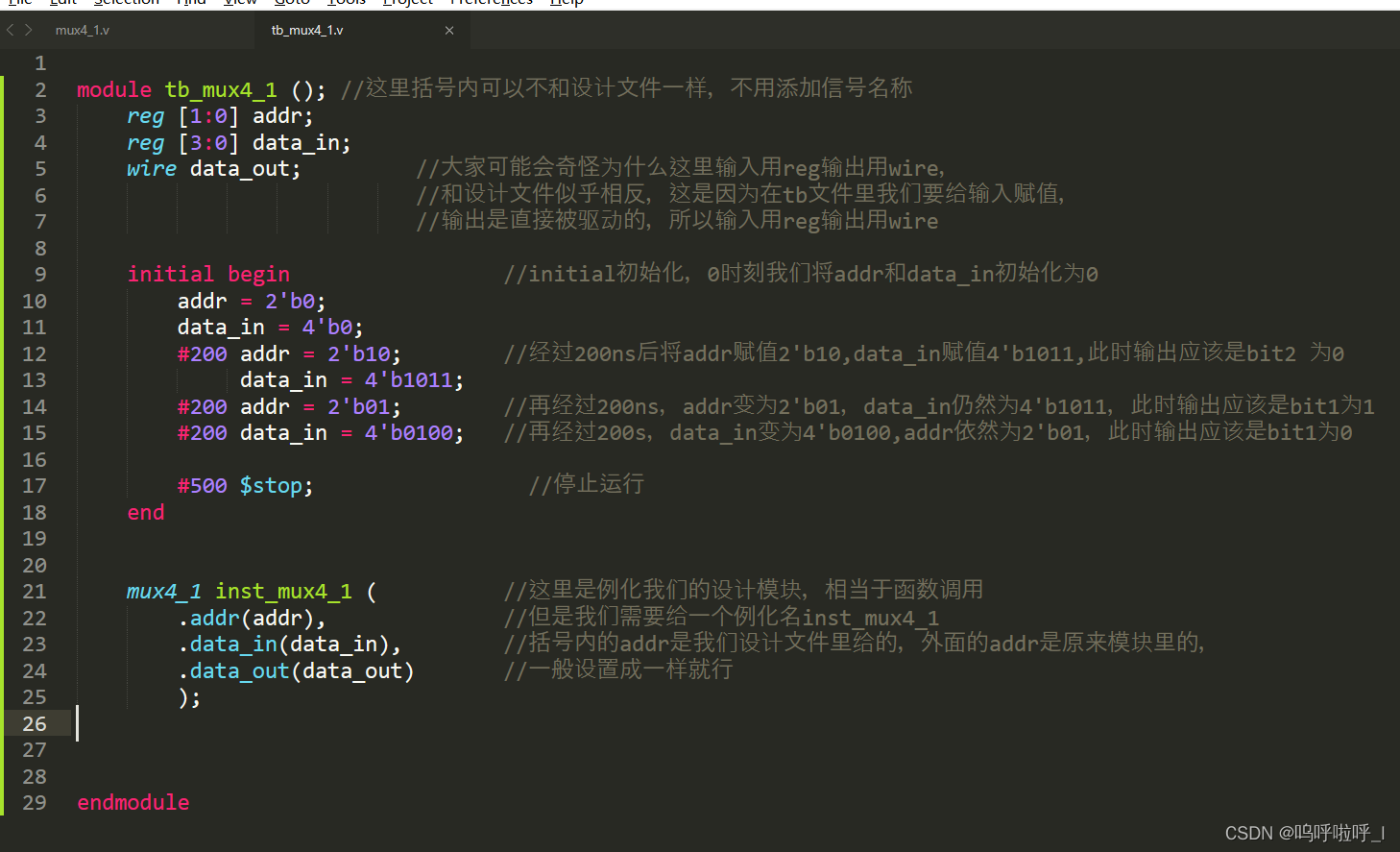

那么我们得到设计文件之后,如何验证我们的设计文件能否实现我们预想的功能?没错一般我们就需要进行仿真,仿真无疑就是希望它能工作起来,那此时我们就需要从设计的模块外部给他一个激励,让他能够运转起来。在设计文件中,我们有input、output,但是如果我们不给输入激励它完全是没法运转起来的,换个说法,大家最近在用quartus做电子线路实验,设计好代码之后大家会添加波形文件,给输入信号激励,我记得在“判断是否能整除2、3、5”的这个是严重输入是逐步加1的,可能大家是按照教学视频去操作的并没太关注他到底在做什么,是怎么实现的,其实我们可以设计各种各样的激励文件,我们一般称之为testbench,想让输入怎么变他都可以怎么变,接下来对照上面的选择器,我们写一个激励文件testbench。

module tb_mux4_1 (); //这里括号内可以不和设计文件一样,不用添加信号名称 reg [1:0] addr; reg [3:0] data_in; wire data_out; //大家可能会奇怪为什么这里输入用reg输出用wire, //和设计文件似乎相反,这是因为在tb文件里我们要给输入赋值, //输出是直接被驱动的,所以输入用reg输出用wire initial begin //initial初始化,0时刻我们将addr和data_in初始化为0 addr = 2'b0; data_in = 4'b0; #200 addr = 2'b10; //经过200ns后将addr赋值2'b10,data_in赋值4'b1011,此时输出应该是bit2 为0 data_in = 4'b1011; #200 addr = 2'b01; //再经过200ns,addr变为2'b01,data_in仍然为4'b1011,此时输出应该是bit1为1 #200 data_in = 4'b0100; //再经过200s,data_in变为4'b0100,addr依然为2'b01,此时输出应该是bit1为0 #500 $stop; //停止运行 end mux4_1 inst_mux4_1 ( //这里是例化我们的设计模块,相当于函数调用 .addr(addr), //但是我们需要给一个例化名inst_mux4_1 .data_in(data_in), //括号内的addr是我们设计文件里给的,外面的addr是原来模块里的, .data_out(data_out) //一般设置成一样就行 ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

三、Modelsim使用教程

(1)打开Modelsim

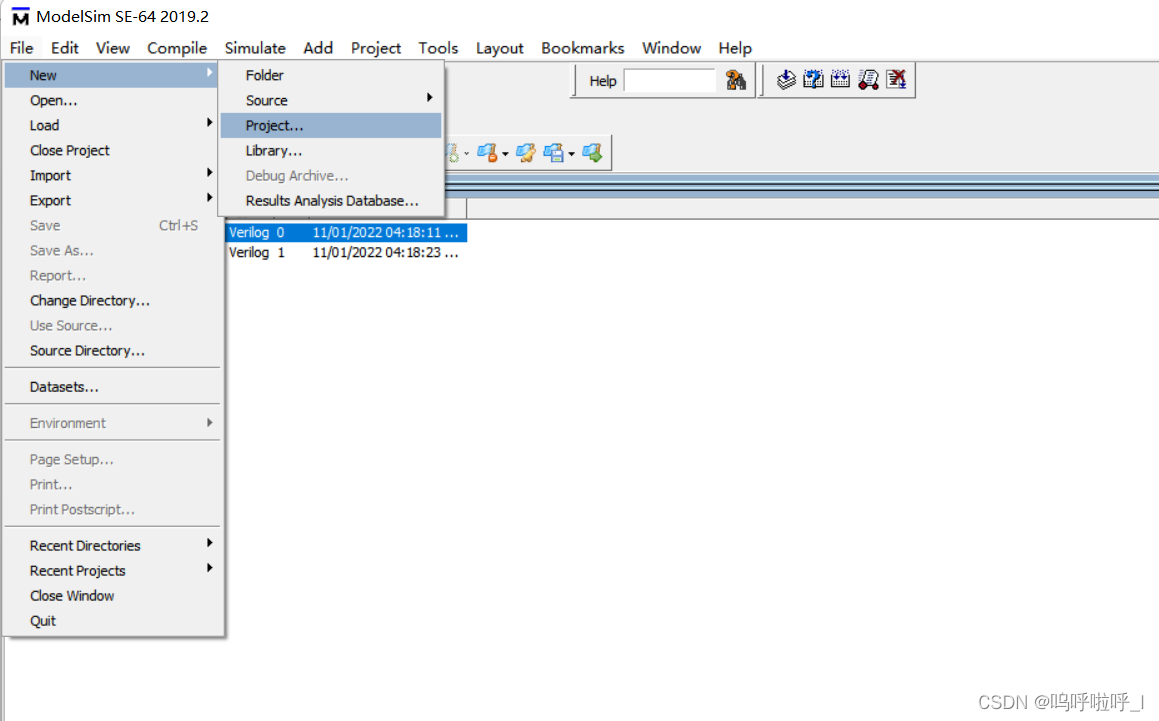

点击右上角file→New→Project

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存失败,源站可能有防盗链机制,建议将图片保存下来直接上传下上传(iFhxWW9W1-1667293573100)(https://s-cure2.wostatic.cn/static/eqDqm6xV8vSf61jzpVijNa/image.pDg?auth_key=nn-1667292207-qBdhApHUihV3QfmbTu2CSD-0-d1596fbb372b225d0c2f88650efdd669)(

https://secure2.wostatic.cn/static/eqDq86xVnvSf61jzpVijNa/image.png?auth_key=1667292207-qBdhApHUihV3QfmbTu2CSD-0-d1596fbb372b225d0c2f88650efdd669)]

[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-HwRhAYUV-1667293600035)(https://secure2.wostatic.cn/static/eqDq86xVnvSf61jzpVijNa/image.png?auth_key=1667292207-qBdhApHUihV3QfmbTu2CSD-0-d1596fbb372b225d0c2f88650efdd669)]](https://img-blog.csdnimg.cn/85dfbe690599490a9927e670b03dfab0.png)

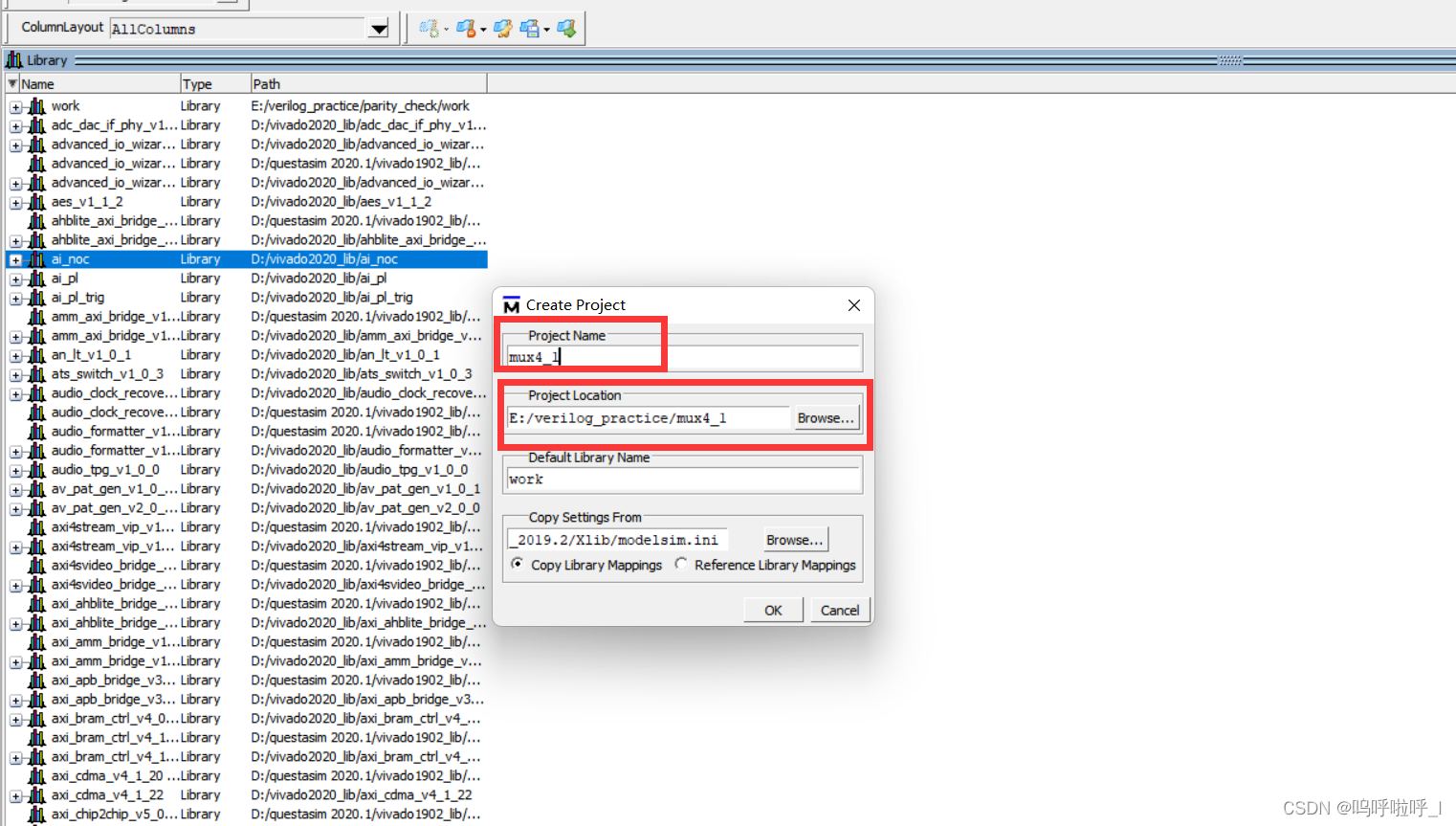

(2)设置工程名字以及所在文件夹,其他默认不用管

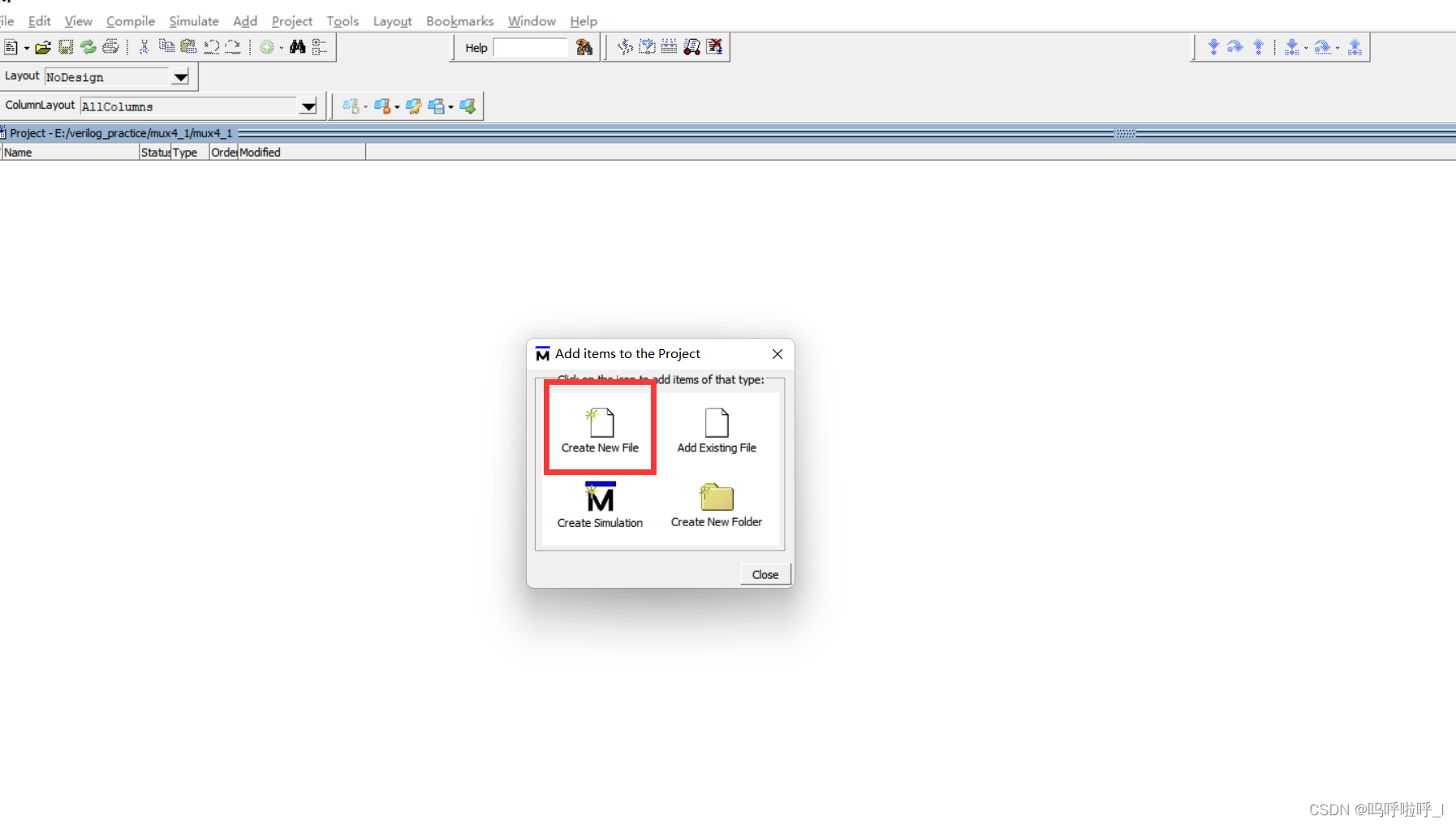

(3)添加设计文件

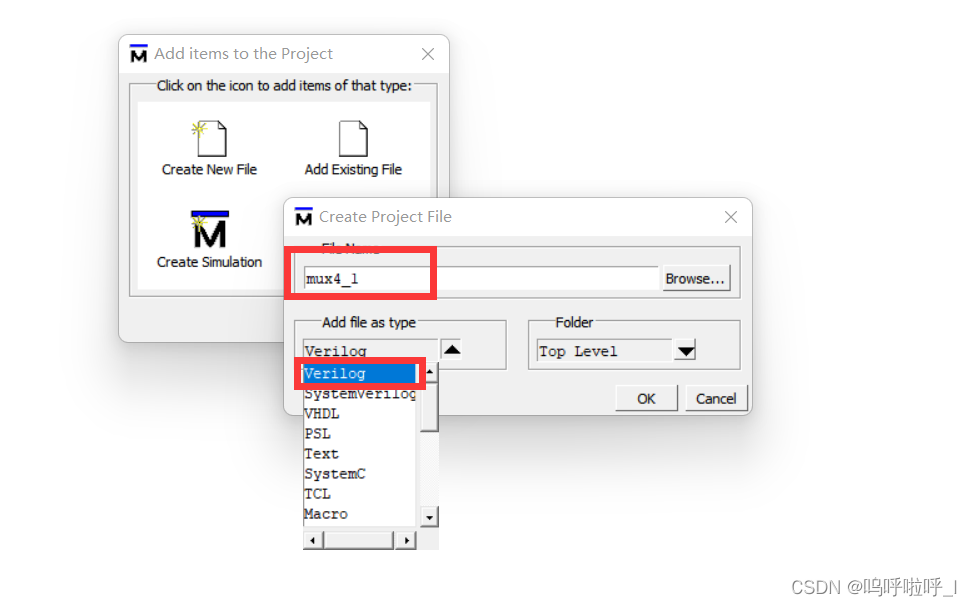

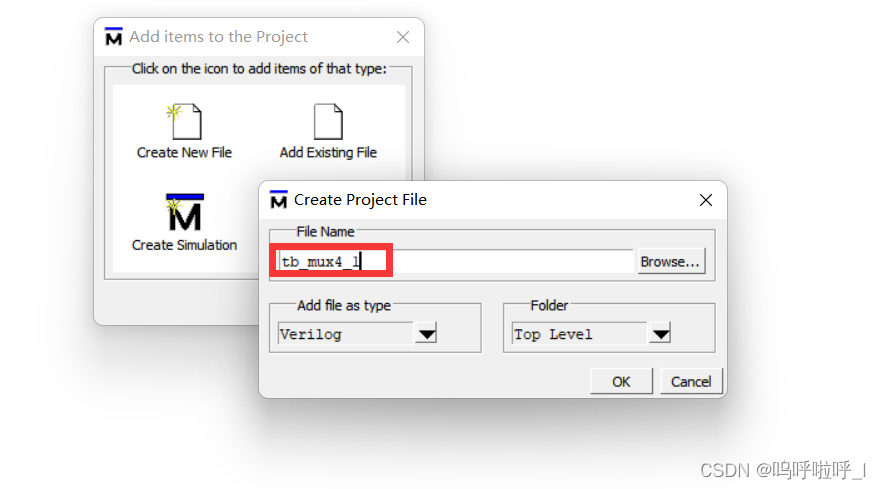

点击Create New File,设置设计文件名字,这里设置为mux4-1,选择文件类型ADD files as type为Verilog(不要选成VHDL),同时也可以把激励文件添加进去(我这里将tb_mux4_1激励文件也添加进去了,也可以后续单独添加)

(4)编写设计文件和激励文件

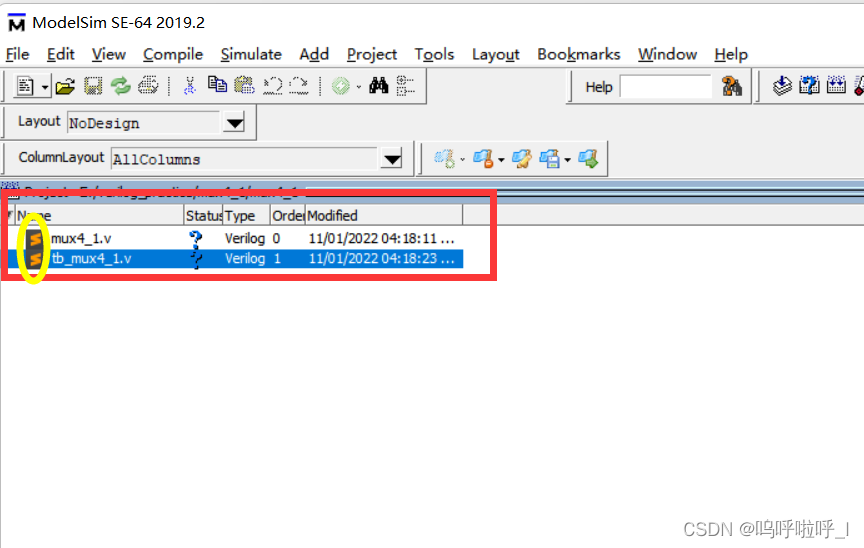

双击添加好的文件即可打开编写

大家可能会发现自己的和我图中黄色圈起来的地方标志不一样,没有关系这是因为我用的第三方编辑器,大家双击之后应该直接退弹出modelsim自带的编辑器,正常编辑就好。

(5)编译文件

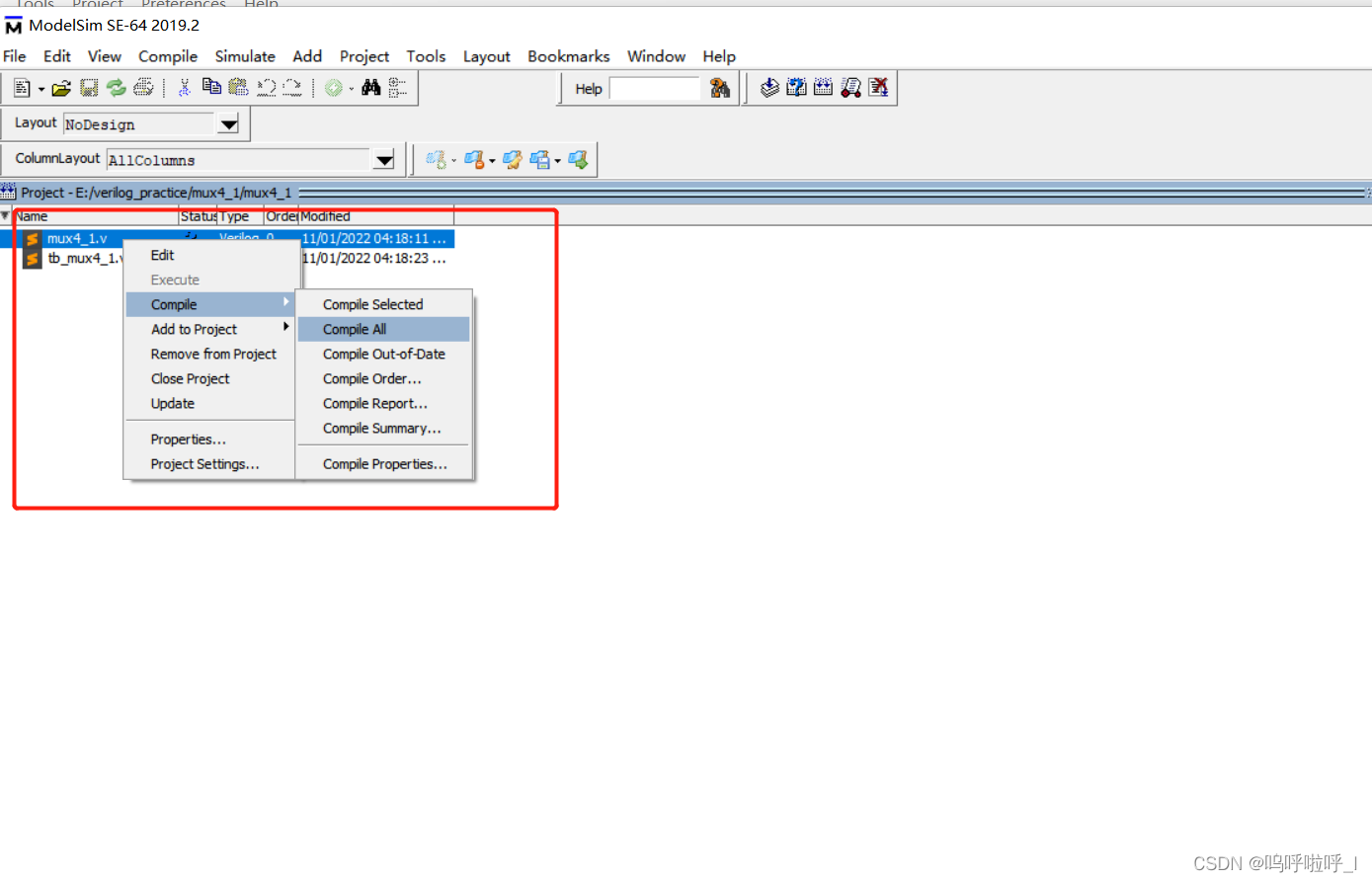

编写好文件后,选中一个文件右键单击,选择Compi→Compile All

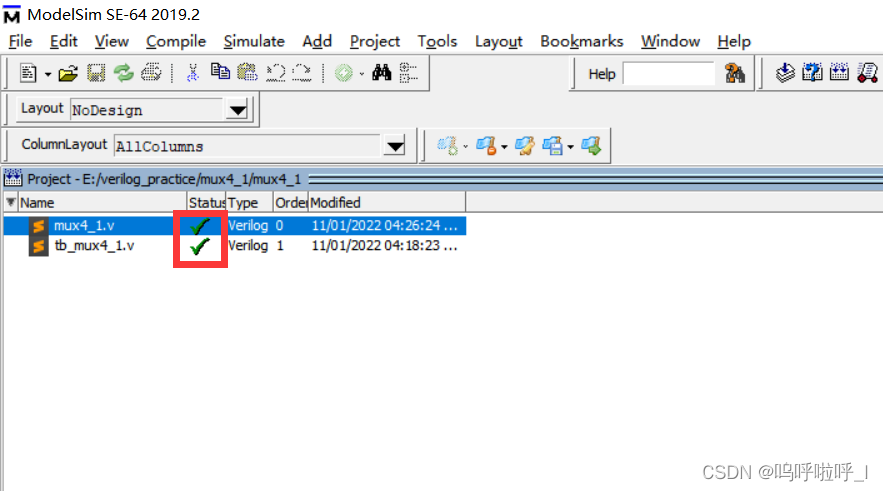

编译好没有问题后会显示绿色的√,如果报错根据报错信息检查代码进行修改。

(6)仿真

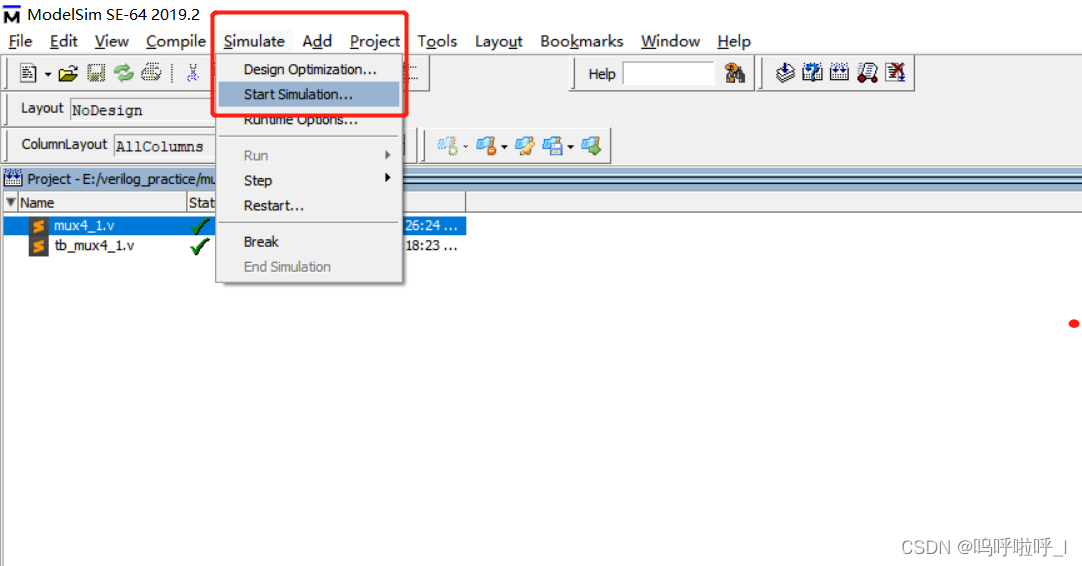

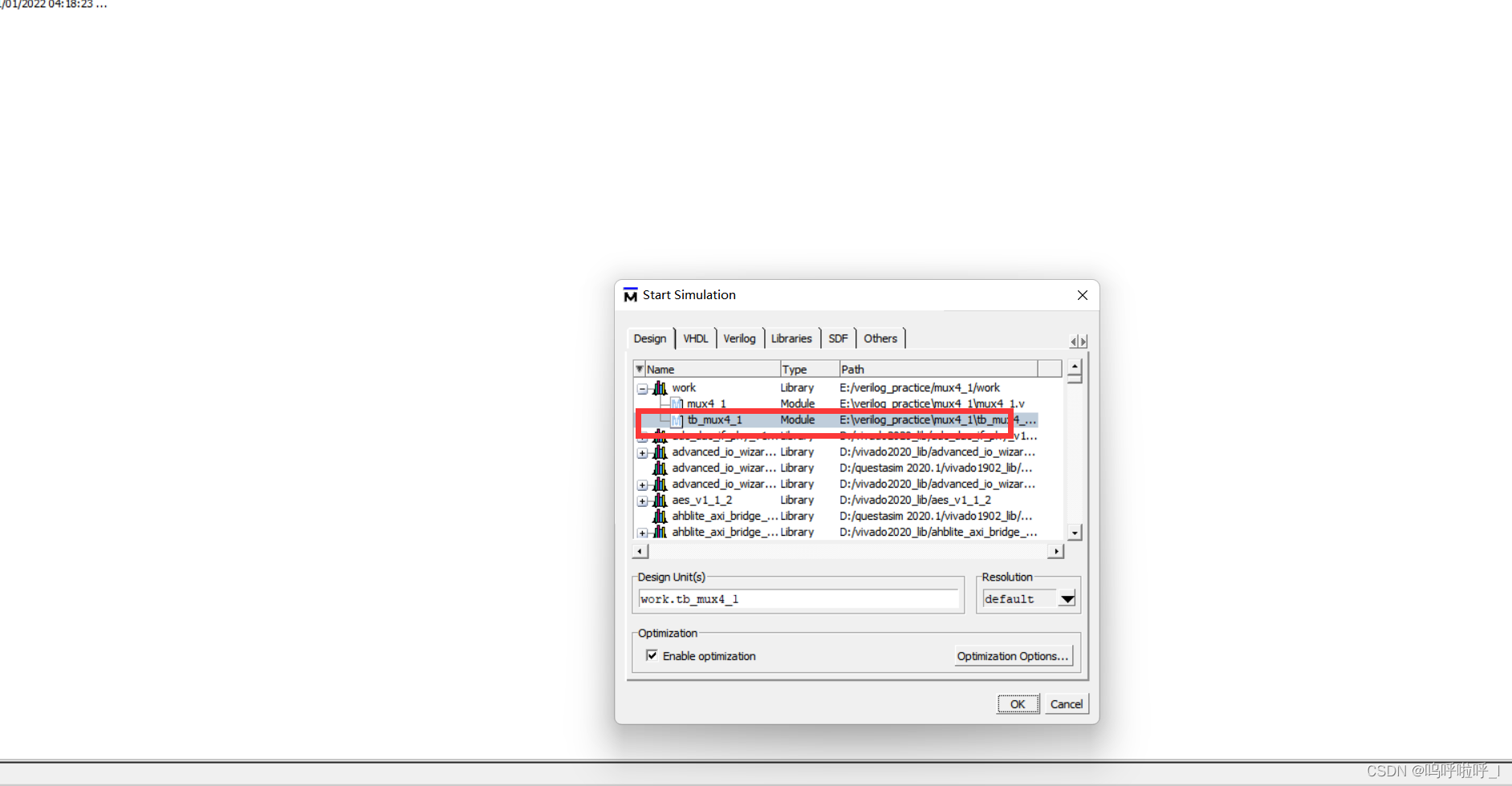

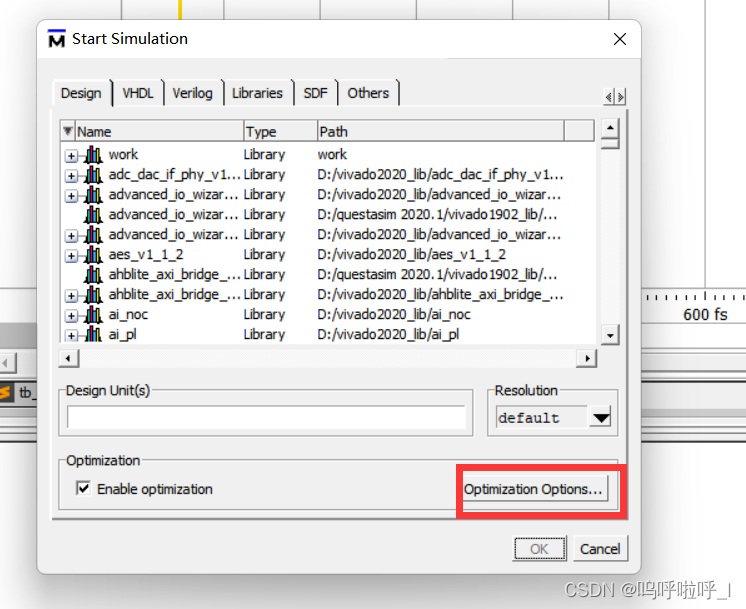

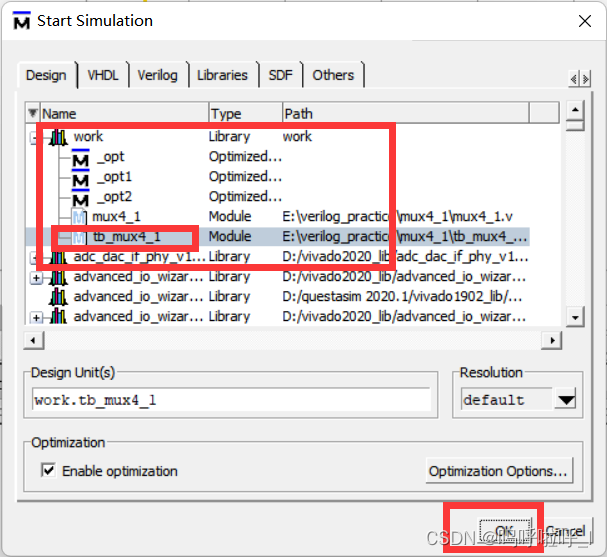

在最上面一栏找到Simulate→Start Simulation,点击,会弹出来一个框,然后我们选择我们的激励文件tb_mux4_1,点击ok。

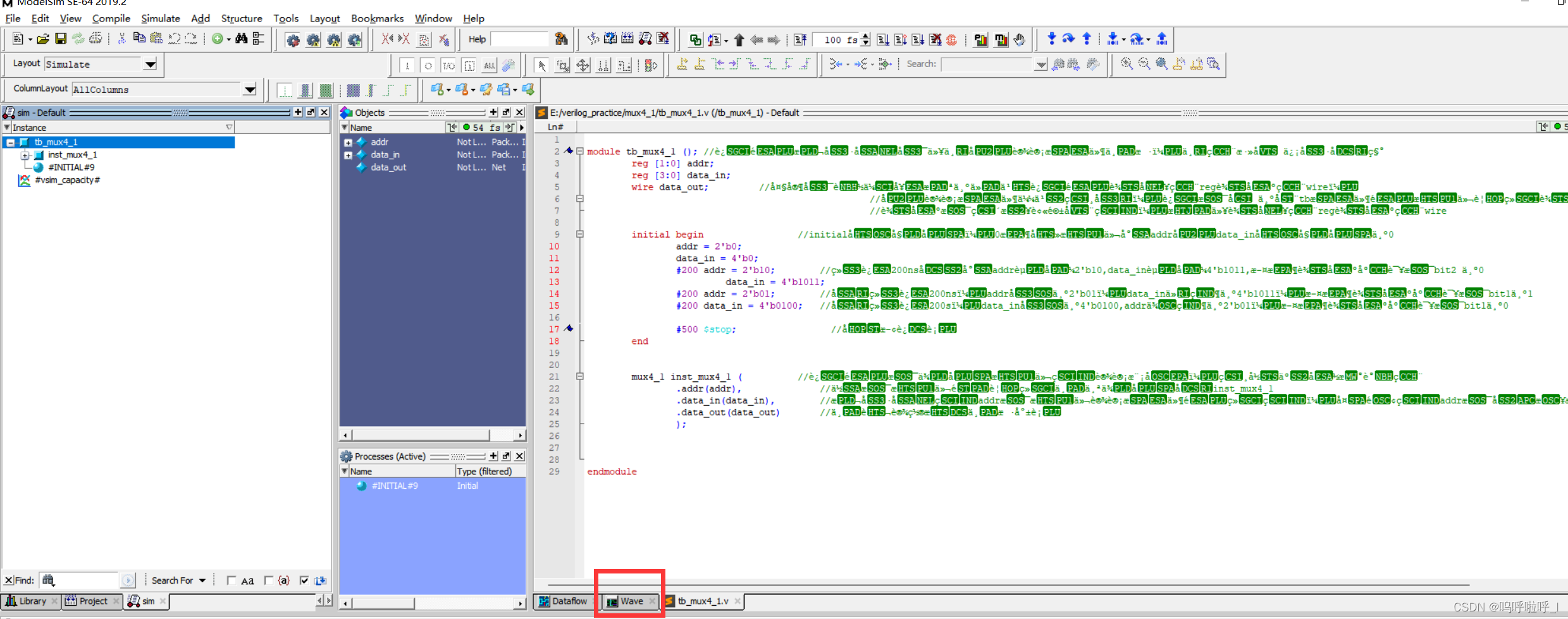

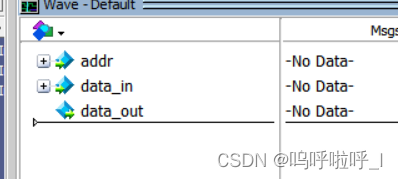

我们点击红色框中标出来的Wave,发现一片空白,只因为我们没有把要观察的信号添加到波形中

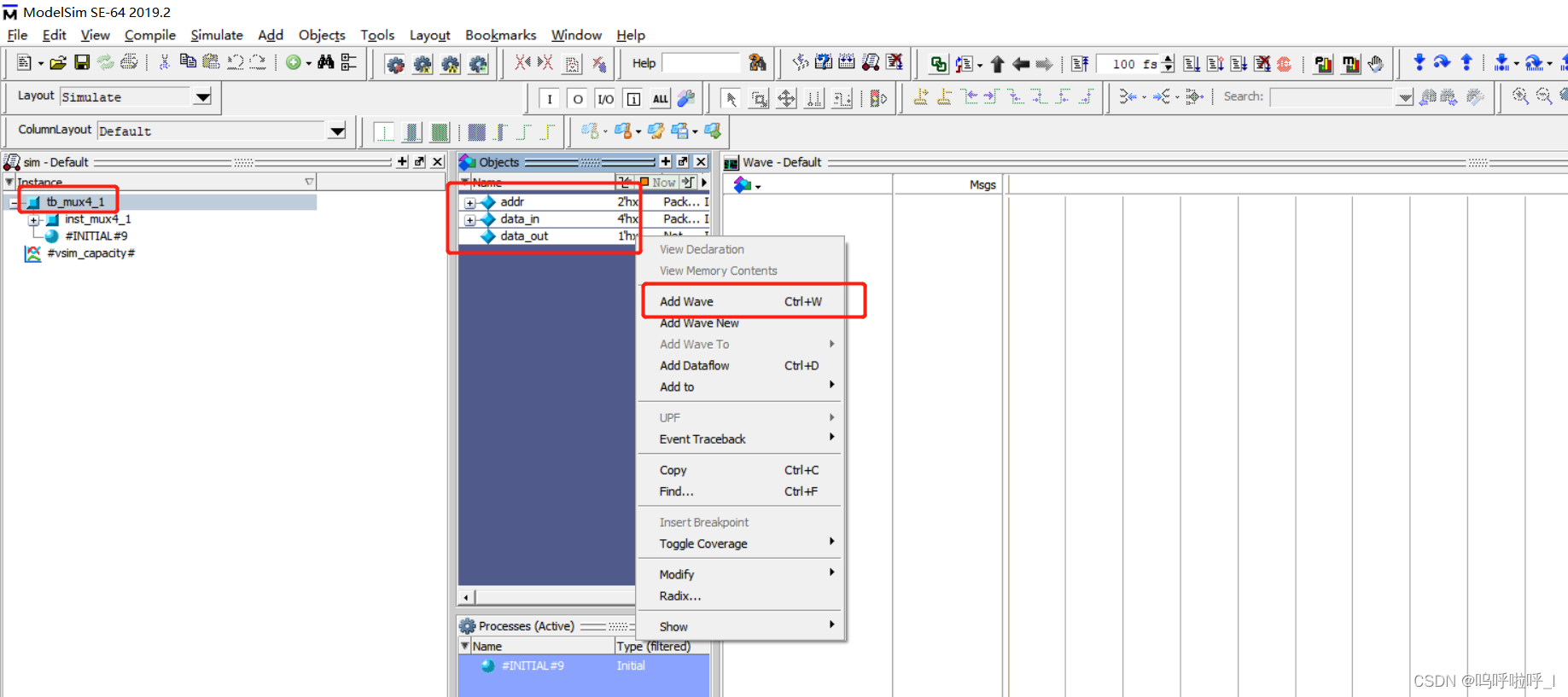

我们点击tb_mux4_1,选中Objects中的信号右键,Add Wave

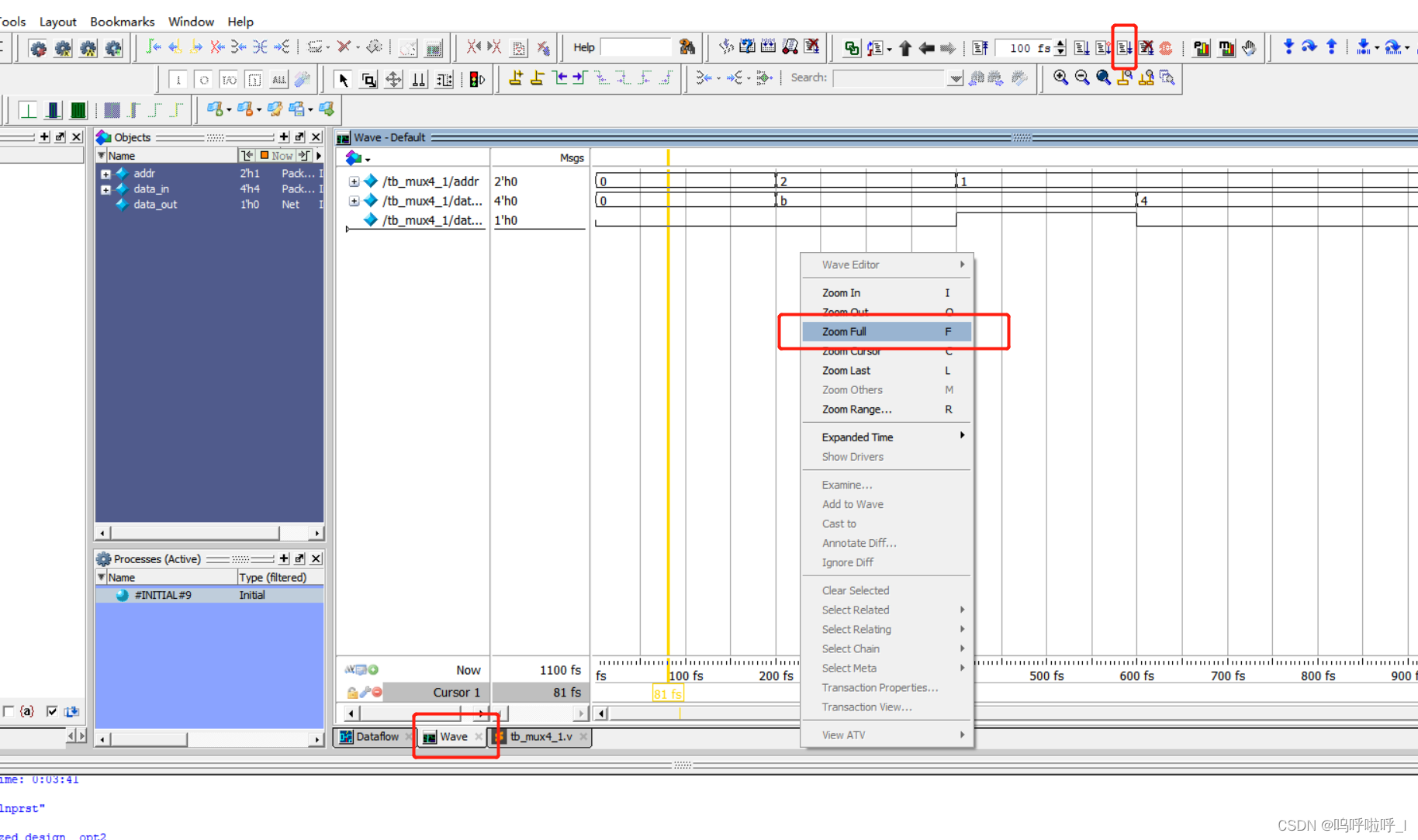

点击右上角红色框圈起来的Run All,会跳转到代码界面,再点击圈起来的Wave文件

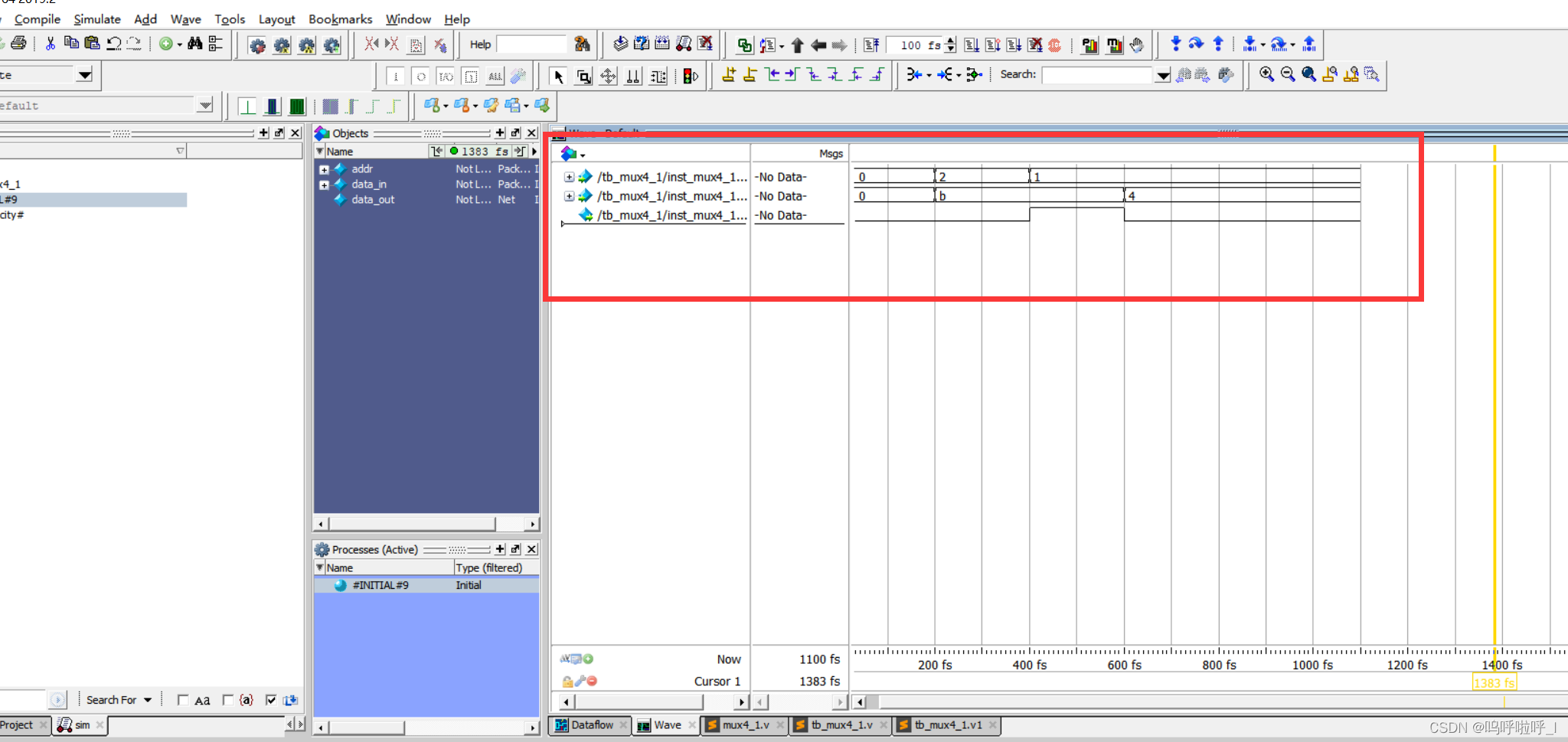

得到仿真波形文件

●在波形处右键Zoom full可以观看整个波形,想放大某一部分时鼠标点击某一处,按住ctrl转动鼠标滑轮可以放大和缩小;

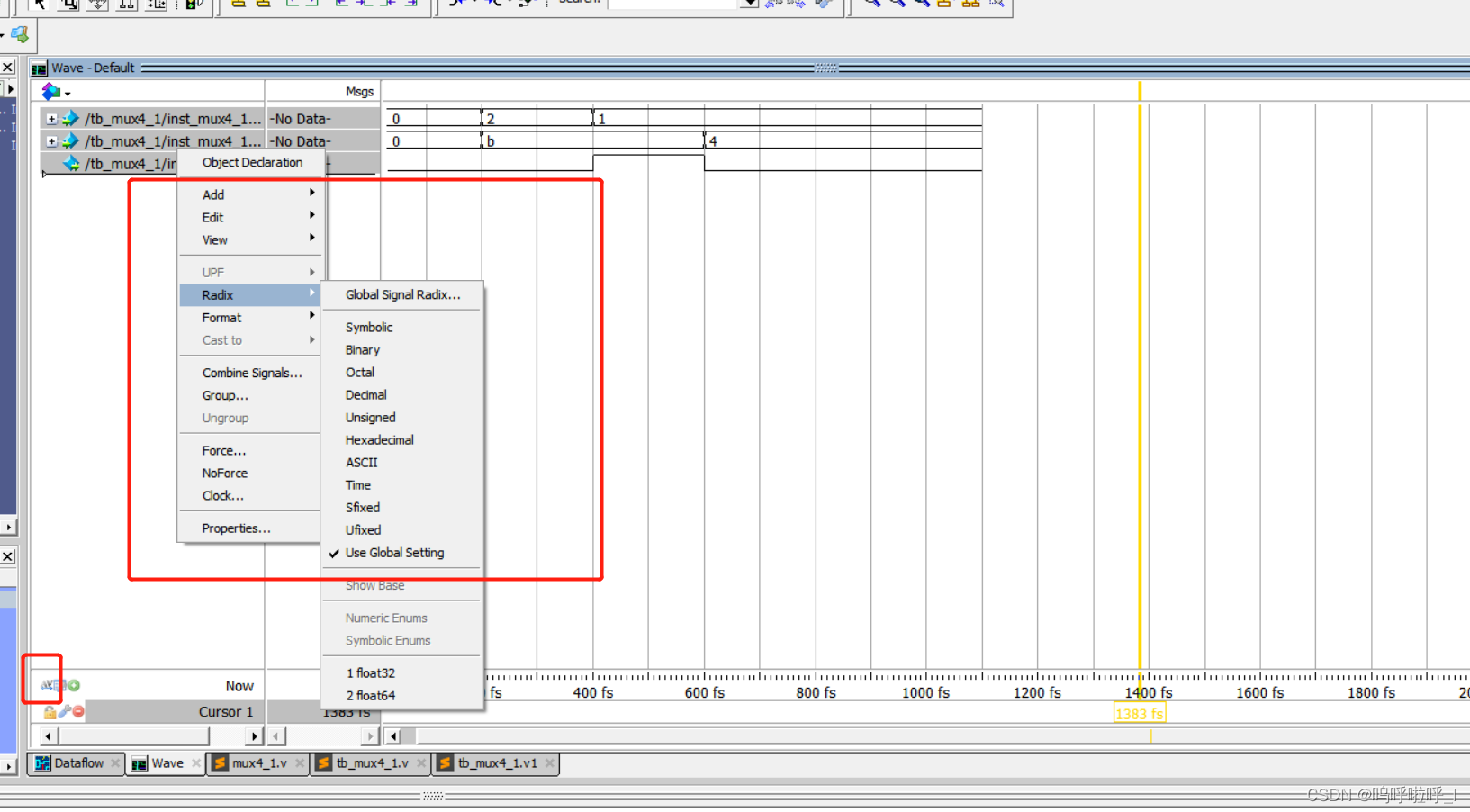

●选中信号右键点击Radix可以选择现实的进制;左下角小方框中框起来的东西点一下,就不会显示信号的路径名称了,方便观察。

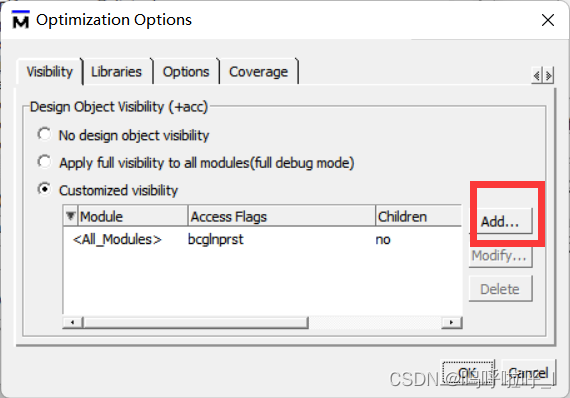

可能会碰到以下问题

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-N3vWWBrL-1667293471092)(https://secure2.wostatic.cn/static/sU3BM13DTDus4zNPqQzpnx/image.png?auth_key=1667292552-trHwiEfHGP1P1VK5TEg59s-0-9b7968d05f3af198b1f5a34702b0cd53)]](https://img-blog.csdnimg.cn/d4aa136ab5bb4b4caea3a9f94dbc8363.png)

但这种方法只能解决本次仿真问题,无法从根本上解决,下一次打开时可能又得重新设置(但这个我也是机率性碰到,后续有空了从根本上解决掉再发出来)。

ok,以上就是简单的使用教程了,另外给大家附上一些如何设置波形颜色、波形高度等方便观察的文章链接。更加具体的使用方法大家可以自己搜索一下,有很多讲解文章。

Modelsim波形颜色设置

Modelsim波形颜色及高度设置