- 1本地部署Ollama+qwen本地大语言模型Web交互界面_[apps.ollama.main] connection error: cannot connec

- 2iPhone苹果手机iOS系统怎么修复?教你自己修复iOS故障_ios系统修复

- 3动手搭建的第一个区块链_搭建区块链的第一个环节

- 4【风速预测】基于matlab DBN算法风速预测【含Matlab源码 1400期】_提出的风速预测方法的代码

- 5HarmonyOS 开发知识:去繁化简,实战整理的开发者清单【NEXT版本】_鸿蒙 record与map的区别

- 6Linux交叉编译opencv(ARM)_linux下编译opencv4_linux opencv 交叉编译

- 7java接入AI大模型个人实践(一)_spring ai

- 8PostgreSQL 为适配等保测评要求的安全性配置方法汇总(Linux&Windows)

- 97-zip删除密码的4种方法_7zip怎么删除密码

- 10docker启动报错:Job for docker.service failed because the control process exited with error code.

FPGA状态机详解_fpga状态机怎么跳出去

赞

踩

FPGA的特点是并行执行,但如果需要处理一些具有前后顺序的事件,就需要使用状态机。状态机是一种用于处理具有前后顺序的事件的计算机模型,包含现态、条件、动作和次态四个要素,它可以将一个复杂的控制流程分解成多个互相独立的状态,从而简化设计过程并提高了系统的可靠性和性能。本文将对FPGA状态机进行详细介绍,帮助大家了解状态机的设计和应用。

一、FPGA状态机基础

1、基础概念

FPGA状态机是一种能够描述对象在运行周期内的所有状态,以及从一个状态到另一个状态转换的过程的抽象模型。状态机可归纳为4个要素,即现态、条件、动作、次态。

①现态:当前所处的状态。

②条件:当一个条件被满足,将会触发一个动作,或者执行一次运行状态的变化。

③动作:条件满足后执行的动作。动作不是必需的,也可以直接迁移到新状态而不进行任何动作。

④次态:条件满足后要跳转到的新状态。其中,“次态”是相对于“现态”而言的,一旦被跳转后,“次态”就转变成新的“现态”了。

2、状态机分类

通常情况下,FPGA状态机一般有两种类型:

-

Moore型状态机:下一状态只由当前状态决定 。

-

Mealy 型状态机:下一状态不但与当前状态有关,还与当前输入值有关 。

由于Mealy型状态机的输出与输入有关,输出信号很容易出现毛刺,所以一般采用Moore型状态机。

(1)Mealy状态机

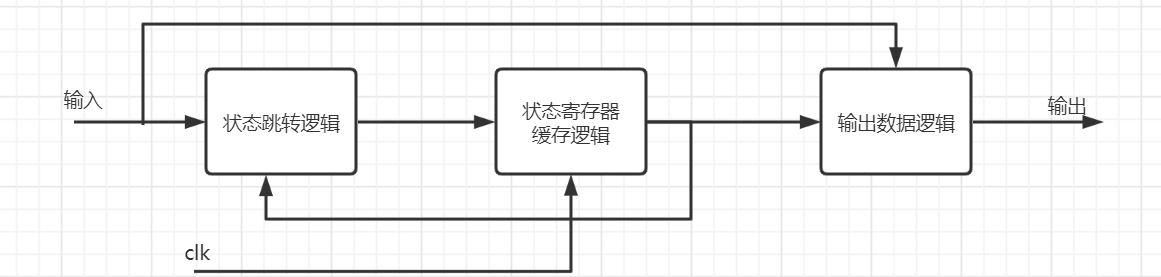

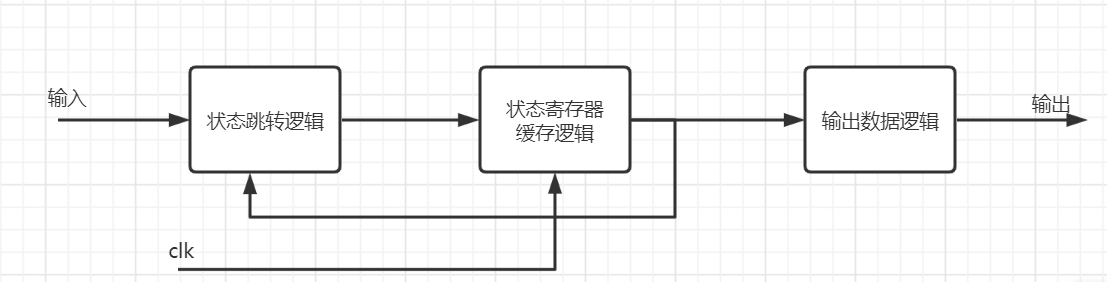

输出逻辑不但取决于当前“状态”还取决于“输入”,如图所示。

(2)Moore状态机

输出逻辑仅仅取决于当前状态,且与当前时刻的输入无关,如图所示。

二、FPGA状态机实现方式

FPGA状态机的描述方式主要分为3种,分别是一段式、两段式、三段式。

1、一段式状态机

一段式状态机使用1个always块,把状态跳转和寄存器输出逻辑都写在一起,其输出是寄存器输出,无毛刺,但是这种方式代码较混乱,逻辑不清晰,难于修改和调试,应该尽量避免使用。

下面给出一个一段式的Mealy状态机示例:

- module one_state_machine (

- input clk,

- input rst_n,

- input [1:0] inp,

- output reg outp

- );

-

- // 定义状态

- localparam STATE_0 = 0,

- STATE_1 = 1,

- STATE_2 = 2,

- STATE_3 = 3;

-

- // 定义状态寄存器和初始状态

- reg [1:0] state_r;

-

- // 初始化状态寄存器

- always @(posedge clk or negedge rst_n) begin

- if (~rst_n) begin

- state_r<= STATE_0;

- end else begin

- case (state_reg)

- STATE_0: begin

- if (inp == 2'b00) begin

- state_r <= STATE_0;

- outp <= 0;

- end else if (inp == 2'b01) begin

- state_r <= STATE_1;

- outp <= 1;

- end else if (inp == 2'b10) begin

- state_r <= STATE_2;

- outp <= 0;

- end else begin

- state_r <= STATE_3;

- outp <= 1;

- end

- end

-

- STATE_1: begin

- if (inp == 2'b00) begin

- state_r <= STATE_1;

- outp <= 1;

- end else if (inp == 2'b01) begin

- state_r <= STATE_2;

- outp <= 0;

- end else if (inp == 2'b10) begin

- state_r <= STATE_3;

- outp <= 1;

- end else begin

- state_r <= STATE_0;

- outp <= 0;

- end

- end

-

- STATE_2: begin

- if (inp == 2'b00) begin

- state_r <= STATE_2;

- outp <= 0;

- end else if (inp == 2'b01) begin

- state_r <= STATE_3;

- outp <= 1;

- end else if (inp == 2'b10) begin

- state_r <= STATE_0;

- outp <= 0;

- end else begin

- state_r <= STATE_1;

- outp <= 1;

- end

- end

-

- STATE_3: begin

- if (inp == 2'b00) begin

- state_r <= STATE_3;

- outp <= 1;

- end else if (inp == 2'b01) begin

- state_r <= STATE_0;

- outp <= 0;

- end else if (inp == 2'b10) begin

- state_r <= STATE_1;

- outp <= 1;

- end else begin

- state_reg <= STATE_2;

- outp <= 0;

- end

- end

- endcase

- end

- end

-

- endmodule

2、二段式状态机

二段式状态机使用2个always块,都是时序逻辑,其中一个always块用于写状态机的状态跳转逻辑,另一个always块用于写当前状态下的寄存器输出逻辑。这种方式逻辑代码清晰,易于调试和理解,是比较推荐的一个方式。

下面给出一个二段式的Moore状态机示例:

- module state_machine (

- input clk,

- input rst_n,

- output reg out_reg

- );

-

- // 状态寄存器和下一个状态寄存器

- reg [1:0] state_r;

-

- // 状态定义

- parameter IDLE = 2'b00;

- parameter STATE1 = 2'b01;

- parameter STATE2 = 2'b10;

- parameter STATE3 = 2'b11;

-

- // always @(posedge clk or negedge rst_n) 时序逻辑代码块,实现状态跳转逻辑

- always@(posedge clk or negedge rst_n) begin

- if(~rst_n) begin

- state_r <= IDLE;

- end else begin

- case(state_r)

- IDLE: begin

- state_r <= STATE1;

- end

-

- STATE1: begin

- state_r <= STATE2;

- end

-

- STATE2: begin

- state_r <= STATE3;

- end

-

- STATE3: begin

- state_r <= IDLE;

- end

- endcase

- end

- end

-

- // always @(*) 时序逻辑代码块,实现状态输出逻辑

- always@(posedge clk or negedge rst_n) begin

- if(~rst_n) begin

- out_reg <= 1'b0;

- end else begin

- case(state_r)

- IDLE: begin

- out_reg <= 1'b0;

- end

-

- STATE1: begin

- out_reg <= 1'b1;

- end

-

- STATE2: begin

- out_reg <= 1'b1;

- end

-

- STATE3: begin

- out_reg <= 1'b0;

- end

- endcase

- end

- end

- endmodule

3、三段式状态机

三段式状态机使用3个always块,其中一个组合always块用于写状态机的状态跳转逻辑,一个时序always块用于缓存状态寄存器,另一个always块用于写当前状态下的寄存器输出逻辑。这种方式逻辑代码清晰,易于调试和理解,也是比较推荐的一个方式。

- module state_machine (

- input clk,

- input rst_n,

- input [1:0] inp,

- output reg outp

- );

-

- // 定义状态

- localparam STATE_0 = 0,

- STATE_1 = 1,

- STATE_2 = 2,

- STATE_3 = 3;

-

- // 定义状态寄存器和初始状态

- reg [1:0] state_r, next_state ;

-

- // 定义状态寄存器

- always @(posedge clk or negedge rst_n) begin

- if (~rst_n) begin

- state_r <= STATE_0;

- end else begin

- state_r <= next_state;

- end

- end

-

- // 定义状态转移逻辑

- always @(*) begin

- case (state_r)

- STATE_0: begin

- if (inp == 2'b00) begin

- next_state = STATE_0;

- end else if (inp == 2'b01) begin

- next_state = STATE_1;

- end else if (inp == 2'b10) begin

- next_state = STATE_2;

- end else begin

- next_state = STATE_3;

- end

- end

-

- STATE_1: begin

- if (inp == 2'b00) begin

- next_state = STATE_1;

- end else if (inp == 2'b01) begin

- next_state = STATE_2;

- end else if (inp == 2'b10) begin

- next_state = STATE_3;

- end else begin

- next_state = STATE_0;

- end

- end

-

- STATE_2: begin

- if (inp == 2'b00) begin

- next_state = STATE_2;

- end else if (inp == 2'b01) begin

- next_state = STATE_3;

- end else if (inp == 2'b10) begin

- next_state = STATE_0;

- end else begin

- next_state = STATE_1;

- end

- end

-

- STATE_3: begin

- if (inp == 2'b00) begin

- next_state = STATE_3;

- end else if (inp == 2'b01) begin

- next_state = STATE_0;

- end else if (inp == 2'b10) begin

- next_state = STATE_1;

- end else begin

- next_state = STATE_2;

- end

- end

- endcase

- end

-

- // 定义输出逻辑

- always @(*) begin

- case (state_r)

- STATE_0: outp = 0;

- STATE_1: outp = 1;

- STATE_2: outp = 0;

- STATE_3: outp = 1;

- endcase

- end

-

- endmodule

注意:组合逻辑代码中,if语句和case语句必须写满,否则容易形成latch,导致实际运行出问题。

三、状态机的编码方式

1、独热码

独热码(One-hot)是一种状态编码方式,其特点是对于任意给定的状态,状态寄存器中只有1位为1,其余位都为0。使用独热码可以简化译码逻辑电路,因为状态机只需对寄存器中的一位进行译码,同时可用省下的面积抵消额外触发器占用的面积。相比于其他类型的有限状态机,加入更多的状态时,独热码的译码逻辑并不会变得更加复杂,速度仅取决于到某特定状态的转移数量。

此外,独热码还具有诸如设计简单、修改灵活、易于综合和调试等优点。但值得注意的是,相对于二进制码,独热码速度更快但占用面积较大。

- module state_machine(

- input clk,

- output reg [3:0] state_out

- );

-

- localparam STATE_A = 4'b0001;

- localparam STATE_B = 4'b0010;

- localparam STATE_C = 4'b0100;

- localparam STATE_D = 4'b1000;

-

- reg [3:0] current_state, next_state;

-

- always @(posedge clk) begin

- current_state <= next_state; // 当时钟上升沿到来时更新状态

- end

-

- always @(*) begin

- case (current_state)

- STATE_A: next_state = STATE_B;

- STATE_B: next_state = STATE_C;

- STATE_C: next_state = STATE_D;

- STATE_D: next_state = STATE_A;

- default: next_state = STATE_A; // 默认情况下返回初始状态

- endcase

- end

-

- assign state_out = current_state; // 将当前状态作为输出

-

- endmodule

2、格雷码

格雷码是一种相邻的两个码组之间仅有一位不同的编码方式。在格雷码中,相邻的两个码组之间仅有一位不同,这种编码方式可以用于实现相邻的两个状态之间只有一位不同的状态机;

FPGA 中的状态机通常需要高速运行,因此使用格雷码可以减少状态转换的开销,并提高时序性能。

- module gray_code_state_machine(

- input clk,

- output reg [3:0] state_out

- );

-

- localparam G0 = 4'b0000;

- localparam G1 = 4'b0001;

- localparam G2 = 4'b0011;

- localparam G3 = 4'b0010;

-

- reg [3:0] current_state, next_state;

-

- always @(posedge clk) begin

- current_state <= next_state; // 当时钟上升沿到来时更新状态

- end

-

- always @(*) begin

- case (current_state)

- G0: next_state = G1;

- G1: next_state = G3;

- G2: next_state = G0;

- G3: next_state = G2;

- default: next_state = G0; // 默认情况下返回初始状态

- endcase

- end

-

- assign state_out = current_state; // 将当前状态作为输出

-

- endmodule

3、普通二进制码

FPGA状态机可以用普通二进制码表示,不同状态按照二进制数累加表示,是常用的一种方式,仿真调试时,状态显示清晰,易于理解代码。

- module binary_state_machine(

- input clk,

- output reg [1:0] state_out

- );

-

- localparam STATE_A = 2'b00;

- localparam STATE_B = 2'b01;

- localparam STATE_C = 2'b10;

- reg [1:0] current_state, next_state;

- always @(posedge clk) begin

- current_state <= next_state; // 当时钟上升沿到来时更新状态

- end

- always @(*) begin

- case (current_state)

- STATE_A: next_state = STATE_B;

- STATE_B: next_state = STATE_C;

- STATE_C: next_state = STATE_A;

- default: next_state = STATE_A; // 默认情况下返回初始状态

- endcase

- end

- assign state_out = current_state; // 将当前状态作为输出

- endmodule

4、格雷码与普通二进制码互转

-

二进制码:一个n位的二进制码可以表示2^n种状态,它有2^(n-1)个相邻状态之间只有一个位不同。

-

格雷码:一个n位的格雷码可以表示2^n种状态,它有2^(n-1)个相邻状态之间只有一位变化。

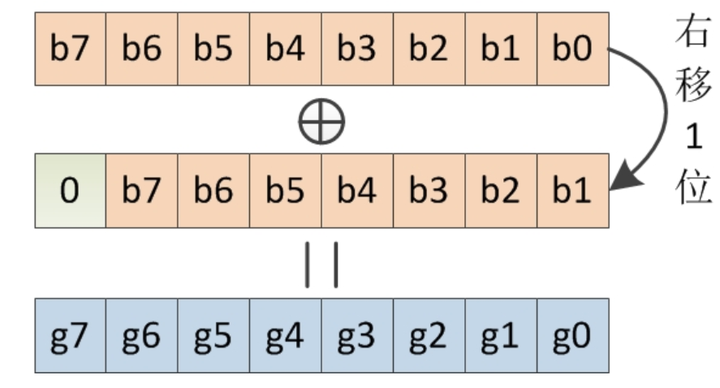

(1)二进制码转换成格雷码

假设当前的状态用二进制码表示为B,那么它所对应的格雷码G可以按照以下方式计算得出:

g[n-1]=b[n-1], g[i]=b[i]^b[i+1], i=[0,1,...,n-2]

下面给出“二进制码转格雷码”的示例代码:

- module bin2gray#(

- parameter DATA_WIDTH = 8

- )(

- input [DATA_WIDTH-1:0] bin,

- output [DATA_WIDTH-1:0] gray

- );

-

- assign gray = {1'b0, bin[DATA_WIDTH-1:1]} ^ bin;

- endmodule

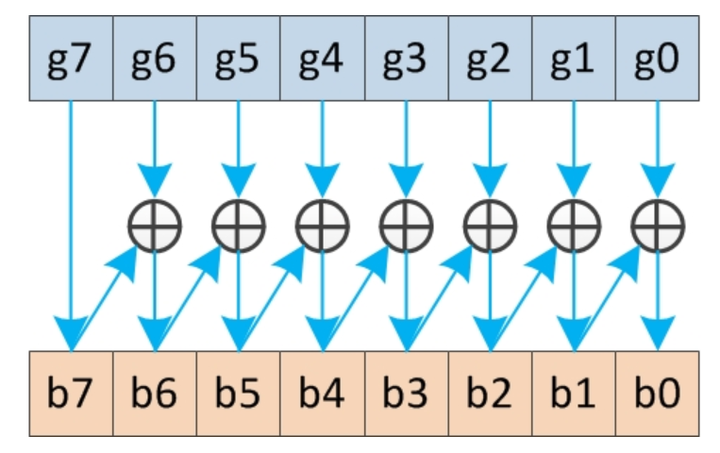

(2)格雷码转换成二进制码

假设当前的状态用格雷码表示为G,那么它所对应的二进制码B可以按照以下方式计算得出:

b[n-1]=g[n-1], b[i]=gray[i]^b[i+1], i=[0,1,...,n-2]

B = G xor (G >> 1)

下面给出“二进制码转格雷码”的示例代码:

- module gray2bin#(

- parameter DATA_WIDTH = 8

- )(

- input [DATA_WIDTH-1:0] gray,

- output [DATA_WIDTH-1:0] bin

- );

-

- genvar i;

-

- assign bin[DATA_WIDTH-1] = gray[DATA_WIDTH-1];

-

- generate

- for(i = 0; i < DATA_WIDTH-1; i = i+1) begin : gray_to_bin

- assign bin[i] = gray[i]^bin[i+1];

- end

- endgenerate

-

- endmodule

四、总结

以上总结了FPGA状态机中有关的知识点,大家可以参考下,建议状态机的写法一般用二段式或三段式,代码逻辑清晰,易于理解和调试,同时需要注意always@(*)块中的组合逻辑,使用if和case语句都要写满,否则综合后容易形成latch,导致上板与仿真结果不一致。

本文将不断定期更新中,点⭐️赞,收⭐️藏一下,不走丢哦

有任何问题,都可以在评论区和我交流哦

本文由FPGA入门到精通原创,公众号为“FPGA入门到精通”,github开源代码:“FPGA知识库”

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。