热门标签

热门文章

- 1智驭未来!百望云强势登榜“2024中国AI应用层创新企业”

- 2一文搞懂编程界中最基础最常见【必知必会】的十一个算法,再也别说你只是听说过【建议收藏+关注】_编程基础算法讲解_程序算法有哪些

- 3正确解决AttributeError: ‘str‘ object has no attribute ‘decode‘异常的有效解决方法_linux 上编程报错"str" object has no attribute "decode

- 4AI助力前端开发:探索智能网页编写的新纪元_前端如何写ai

- 5珈和科技和比昂科技达成战略合作,共创智慧农业领域新篇章

- 6【Python数据分析系列】一文总结dataframe截取/选择/切片的几种方式_dataframe横切选择

- 7关于Java反射的详解及实战案例_java反射实例

- 8tm1639c语言程序,51单片机各种汇编延时子程序整理汇总

- 9Taro 框架中 vue3 request.ts 请求封装_taro.request 封装

- 10Apache Flink X Apache Doris 构建极速易用的实时数仓架构_flinkcdc+flink+doris 实时数仓

当前位置: article > 正文

三、在Xilinx FPGA上使用Cortex M1 软核——Keil中使用J-Link调试Cortex-M1嵌入式工程_紫光fpga cortex m1 jlink

作者:繁依Fanyi0 | 2024-06-14 16:08:28

赞

踩

紫光fpga cortex m1 jlink

在Xilinx FPGA上使用Cortex M1 软核——Keil中使用J-Link调试Cortex-M1嵌入式工程

本文的软件代码部分参考自ARM提供的例程。

本文适合第一章(https://blog.csdn.net/lai823177557/article/details/99691926)中创建的FPGA工程。理论上所有使用J-Link(JTAG模式)调试接口的CM1均适用。

这里有本文的工程:

https://download.csdn.net/download/lai823177557/11607865

- 1

连接硬件

将FPGA中分配的J-Link IO与J-Link调试器一一连接,

配置FPGA

下载第一章中生成的bit流文件

配置debug

- 将J-Link调试器连接到电脑后打开Keil中的

Options for Target配置界面。 - 在

Debug标签下选择J-Link后点击“Settings”。

不出意外调试器能直接读取软核的信息:

- 在

Debug标签下,设置其他选项:

其中“RAM.ini”是调试的初始化文件,用于加载程序文件到软核并设置软核的堆栈信息。RAM.ini的内容如下:

//*** <<< Use Configuration Wizard in Context Menu >>> ***

FUNC void Setup (void)

{

SP = _RDWORD(0x00000000);

PC = _RDWORD(0x00000004);

_WDWORD(0xE000ED08, 0x00000000);

}

LOAD Objects\exec.axf INCREMENTAL

Setup();

g, main

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

其中,“Objects\exec.axf”是工程的输出,名字来源于Output标签中的“Name of Executable”

- 在

Utilities标签中,取消“Update Target before Debugging”复选框:

- 配置完成

现在可以调试了:

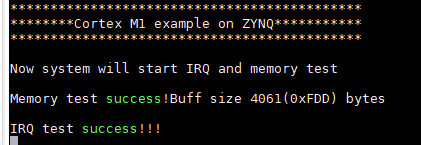

在进入调试界面后,务必复位CM1一次,否则CM1会一直处于Handler模式无法响应用户中断。具体原因不明确,猜测时bit文件中没有CM1的程序文件,导致其进入LOCKED状态导致的。固化程序后一切正常。 - 调试结果

中断(Systick、定时器)、GPIO、串口均正常工作

下一章将分享如何固化Cortex-M1代码到FPGA的BIN文件中。

如发现有错误或者疏漏,请留言~~~

声明:本文内容由网友自发贡献,转载请注明出处:【wpsshop博客】

推荐阅读

相关标签