热门标签

热门文章

- 1V字形研发模式中的测试_v字测试流程

- 2项目管理工具git_git管理工具

- 3LVGL移植到ARM开发板(GEC6818)_gec6818移植lvgl

- 4LeetCode 算法:找到字符串中所有字母异位词c++

- 5《IT 领域准新生暑期预习指南:开启未来科技之旅》

- 6在Linux系统yum安装报错Cannot find a valid baseurl for repo解决方案_error: cannot find a valid baseurl for repo: livna

- 7谷粒商城--分布式基础篇(P1~P27)_谷粒商城分布式基础篇课件

- 8在ROS中用opencv订阅摄像头图像并显示_ros2查看订阅到的图片

- 9dockerfile更改docker镜像源(1)_dockerfile指定镜像源

- 10pycorrector训练自己的模型,pycharm如何训练模型_pycharm中基于keras的模型搭建

当前位置: article > 正文

AD7606时序控制及PWM输出Verilog代码Quartus仿真_ad7606程序

作者:神奇cpp | 2024-07-15 12:57:30

赞

踩

ad7606程序

名称:AD7606时序控制及PWM输出Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

AD7606B输入,(4800-输入)/8(仿真时=学号后

3位),PWM输出(600=100%)

每位交一个pdf文档,包括方案分析(联系应用)、FPGA连线

图、VHD文件(含注释)、编译报告、完整功能仿真结果(详

加说明)、亮点(研究性内容)、参考文献(规范引用)。

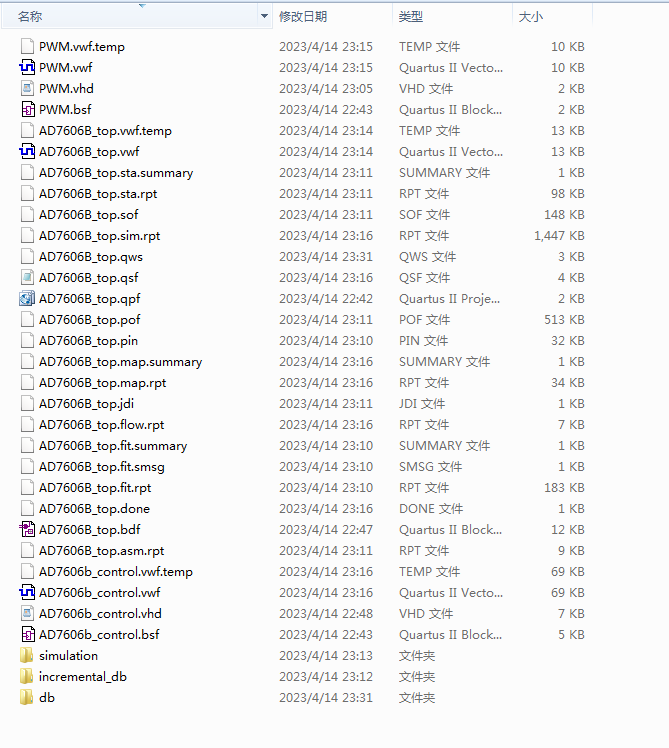

1. 工程文件

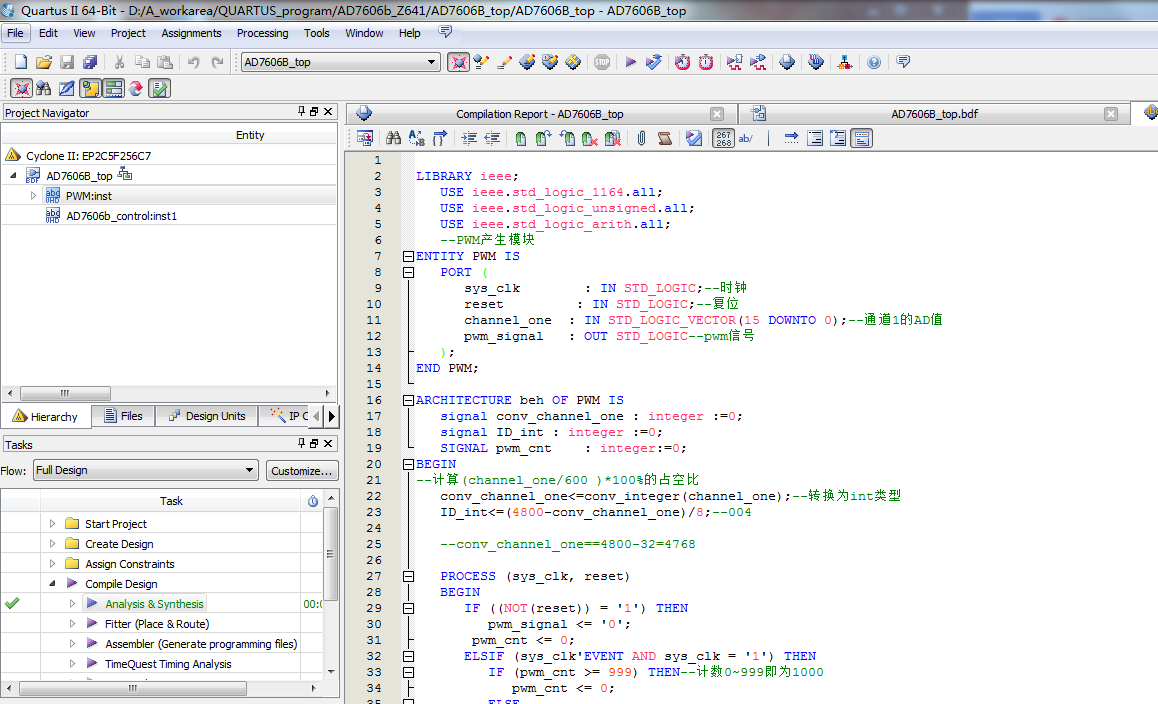

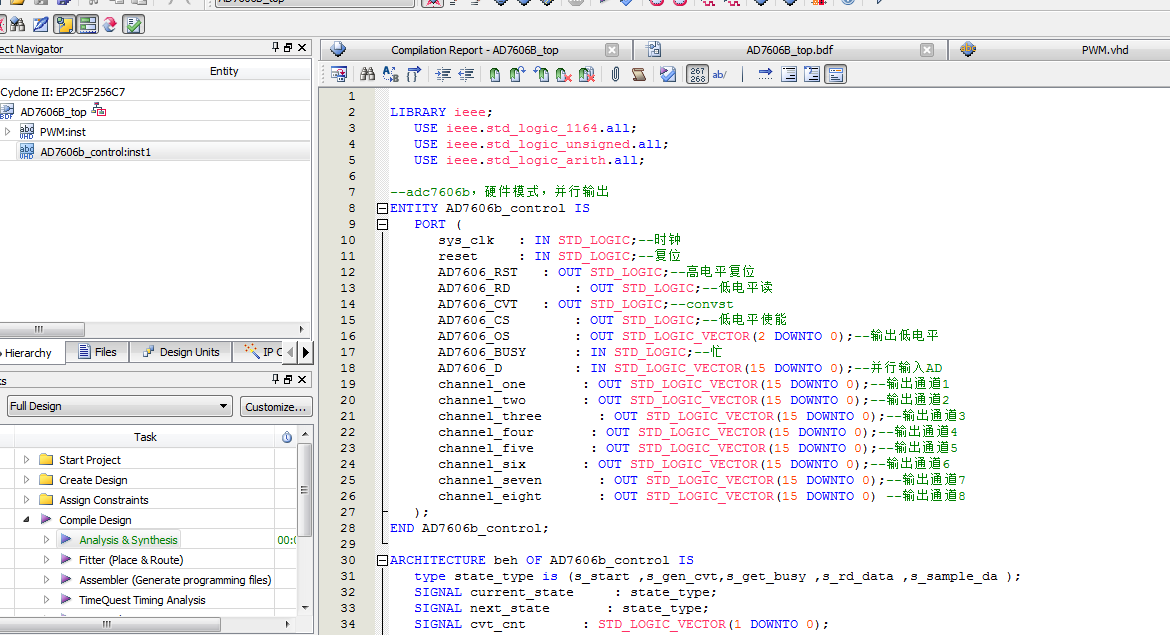

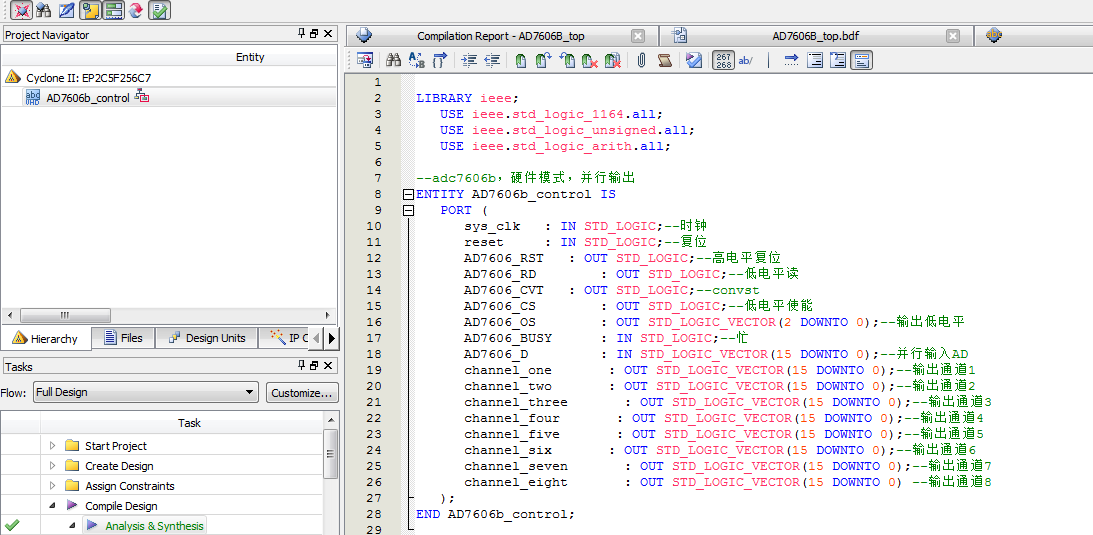

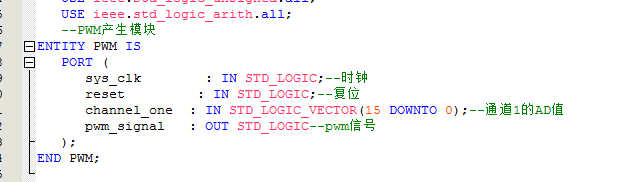

2. 程序文件

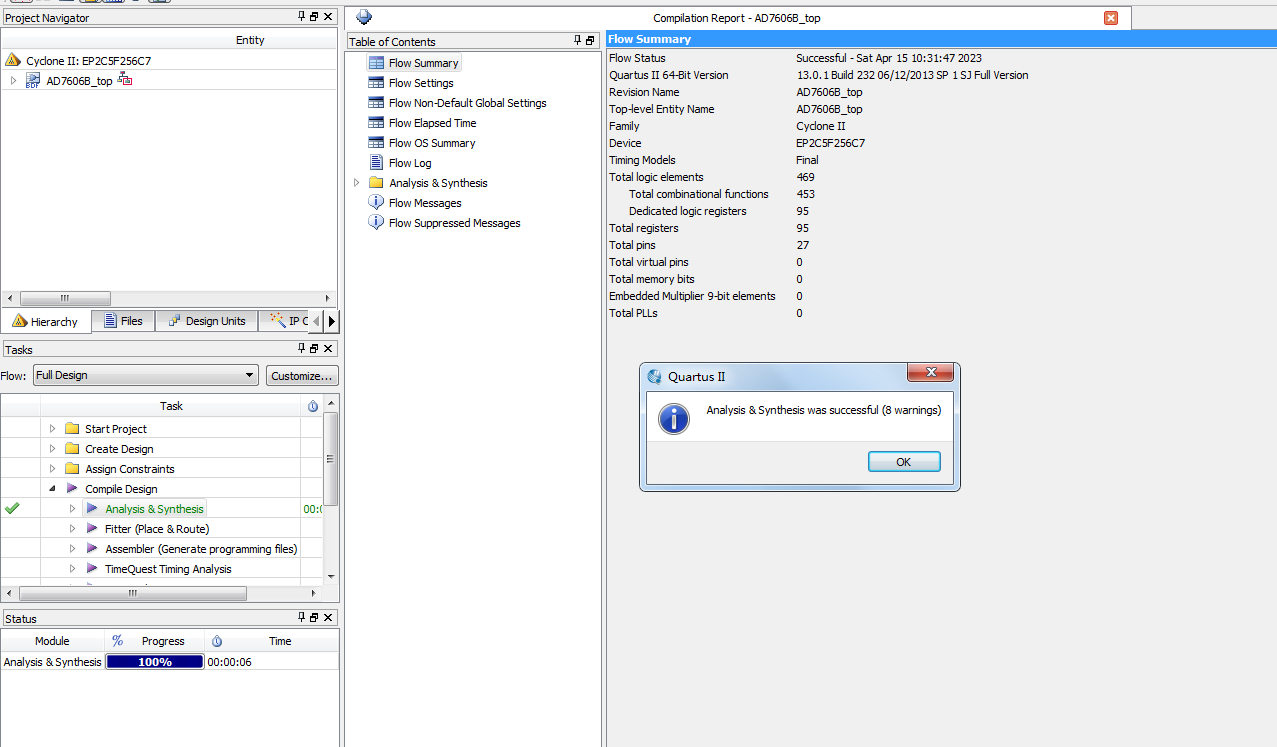

3. 程序编译

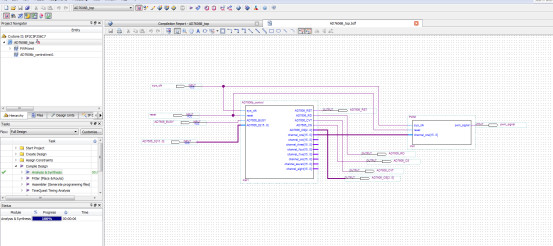

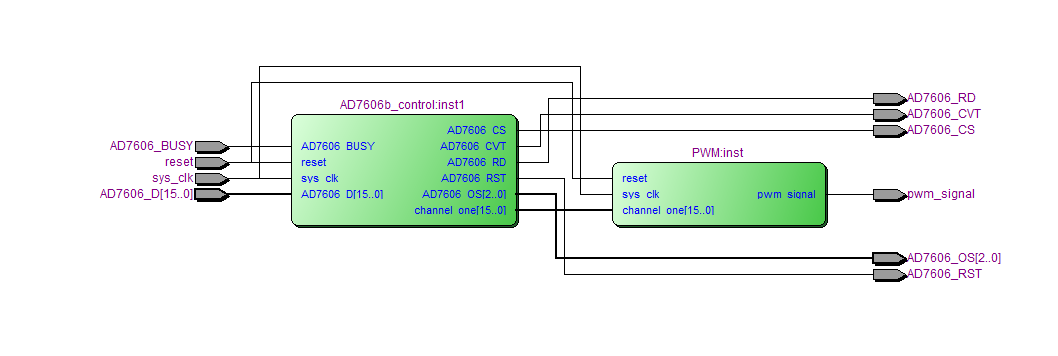

4. RTL图

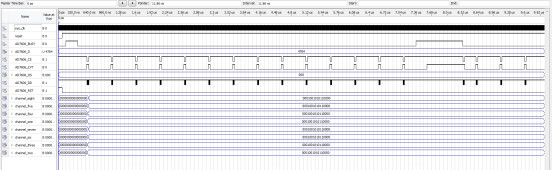

5. 仿真图

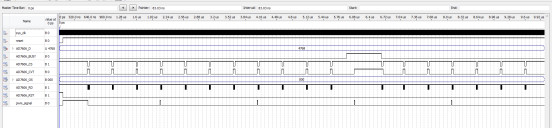

整体仿真图

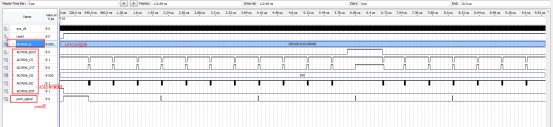

AD7606B模块仿真

PWM模块仿真

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; USE ieee.std_logic_arith.all; --adc7606b,硬件模式,并行输出 ENTITY AD7606b_control IS PORT ( sys_clk : IN STD_LOGIC;--时钟 reset : IN STD_LOGIC;--复位 AD7606_RST : OUT STD_LOGIC;--高电平复位 AD7606_RD : OUT STD_LOGIC;--低电平读 AD7606_CVT : OUT STD_LOGIC;--convst AD7606_CS : OUT STD_LOGIC;--低电平使能 AD7606_OS : OUT STD_LOGIC_VECTOR(2 DOWNTO 0);--输出低电平 AD7606_BUSY : IN STD_LOGIC;--忙 AD7606_D : IN STD_LOGIC_VECTOR(15 DOWNTO 0);--并行输入AD channel_one : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道1 channel_two : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道2 channel_three : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道3 channel_four : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道4 channel_five : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道5 channel_six : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道6 channel_seven : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);--输出通道7 channel_eight : OUT STD_LOGIC_VECTOR(15 DOWNTO 0) --输出通道8 ); END AD7606b_control; ARCHITECTURE beh OF AD7606b_control IS type state_type is (s_start ,s_gen_cvt,s_get_busy ,s_rd_data ,s_sample_da ); SIGNAL current_state : state_type; SIGNAL next_state : state_type; SIGNAL cvt_cnt : STD_LOGIC_VECTOR(1 DOWNTO 0); SIGNAL channel_cnt : STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL AD7606_CVT_s : STD_LOGIC; SIGNAL AD7606_read : STD_LOGIC; SIGNAL read_over : STD_LOGIC; SIGNAL sample_pulse : STD_LOGIC; SIGNAL sample_cnt : integer; BEGIN --状态切换 PROCESS (sys_clk, reset) BEGIN IF (reset= '0') THEN current_state <= s_start; ELSIF (sys_clk'EVENT AND sys_clk = '1') THEN current_state <= next_state; END IF; END PROCESS; --状态控制 PROCESS (current_state, sample_pulse, AD7606_CVT_s, AD7606_BUSY, read_over) BEGIN next_state <= current_state; CASE current_state IS WHEN s_start => IF (sample_pulse = '1') THEN--开始采样 next_state <= s_gen_cvt; END IF; WHEN s_gen_cvt => IF (AD7606_CVT_s = '1') THEN--高电平后跳转 next_state <= s_get_busy; END IF; WHEN s_get_busy => IF ((NOT(AD7606_BUSY)) = '1') THEN next_state <= s_rd_data;--空闲后开始读数 END IF; WHEN s_rd_data =>--读数 next_state <= s_sample_da; WHEN s_sample_da => IF (read_over = '1') THEN--读完 next_state <= s_start; END IF; WHEN OTHERS => next_state <= s_start; END CASE; END PROCESS; --输出控制 PROCESS (sys_clk, reset) BEGIN IF (reset= '0') THEN AD7606_CS <= '1'; AD7606_CVT_s <= '0'; cvt_cnt <= "00"; AD7606_read <= '1'; read_over <= '0'; ELSIF (sys_clk'EVENT AND sys_clk = '1') THEN CASE current_state IS WHEN s_start =>--开始状态 AD7606_CS <= '1'; cvt_cnt <= "00"; AD7606_CVT_s <= '0'; AD7606_read <= '1'; read_over <= '0'; WHEN s_gen_cvt =>--拉高CVT IF (cvt_cnt < "10") THEN cvt_cnt <= cvt_cnt + "01"; ELSE AD7606_CVT_s <= '1'; cvt_cnt <= "00"; END IF; WHEN s_rd_data =>--cs使能信号 AD7606_CS <= '0'; WHEN s_sample_da =>--读数据 IF (AD7606_read = '1') THEN AD7606_read <= '0';--读信号 ELSE AD7606_read <= '1'; END IF; IF (channel_cnt = "111") THEN--读完 read_over <= '1'; END IF; WHEN OTHERS =>NULL; END CASE; END IF; END PROCESS; --输出AD采样值 PROCESS (sys_clk, reset) BEGIN IF (reset= '0') THEN channel_one <= "0000000000000000"; channel_two <= "0000000000000000"; channel_three <= "0000000000000000"; channel_four <= "0000000000000000"; channel_five <= "0000000000000000"; channel_six <= "0000000000000000"; channel_seven <= "0000000000000000"; channel_eight <= "0000000000000000"; channel_cnt <= "000"; ELSIF (sys_clk'EVENT AND sys_clk = '1') THEN IF( current_state =s_sample_da )THEN IF (AD7606_read = '0') THEN channel_cnt <= channel_cnt + "001";--计数 CASE channel_cnt IS WHEN "000" => channel_one <= AD7606_D;--通道1 WHEN "001" => channel_two <= AD7606_D;--通道2 WHEN "010" => channel_three <= AD7606_D;--通道3 WHEN "011" => channel_four <= AD7606_D;--通道4 WHEN "100" => channel_five <= AD7606_D;--通道5 WHEN "101" => channel_six <= AD7606_D;--通道6 WHEN "110" => channel_seven <= AD7606_D;--通道7 WHEN "111" => channel_eight <= AD7606_D;--通道8 END CASE; END IF; ELSE channel_cnt <= "000"; END IF; END IF; END PROCESS; --计数 PROCESS (sys_clk, reset) BEGIN IF (reset= '0') THEN sample_cnt <= 0; ELSIF (sys_clk'EVENT AND sys_clk = '1') THEN IF (sample_cnt = 249) THEN sample_cnt <= 0;--计数到249 ELSE sample_cnt <= sample_cnt + 1;--计数 END IF; END IF; END PROCESS; --输出 AD7606_OS <= "000";--0 AD7606_RST <= NOT reset ;--取反 AD7606_CVT <= AD7606_CVT_s; AD7606_RD <= AD7606_read; sample_pulse <= '1' when (sample_cnt = 249) else '0';--采样 END beh;

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/神奇cpp/article/detail/829464

推荐阅读

相关标签