热门标签

热门文章

- 1使用亚马逊云科技Amazon Bedrock Guardrails构建可靠的AI应用

- 2详解数据结构之二叉树(二叉链,使用递归)

- 3Github 如何设置 master 为默认分支_github设置默认分支

- 4本地生活抽佣系统搭建:如何让系统具有竞争优势?

- 5iOS 解决真机调试找不到设备问题_hx ios真机调试没有查询到设备

- 6elasticsearch笔记_精确值搜索_filter(四)_searchfilter

- 7CosyVoice 语音合成TTS、声音克隆自定义api服务搭建;requests请求使用_cosyvoice 部署

- 8知乎热议!学完Python之后,我的编程能力竟然退化了!

- 9CTP-API开发系列之三:柜台系统简介_ctp柜台

- 10多组件卡片式问答引擎_大模型的卡片式回答

当前位置: article > 正文

使用STARTUPE3原语通过SPI Flash实现UltraScale FPGA的局部重配置(一)

作者:知新_RL | 2024-08-08 11:58:05

赞

踩

startupe3

介绍

最近有用到FPGA的动态重加载,发现手册中有关于KCU105 重加载的明确步骤,但是顶层文件是VHDL,使用Tcl指令,因此参考该手册步骤,使之适用于自己的板卡。

FPGA:KU040

串口调试助手:tera term

编程语言:verilog

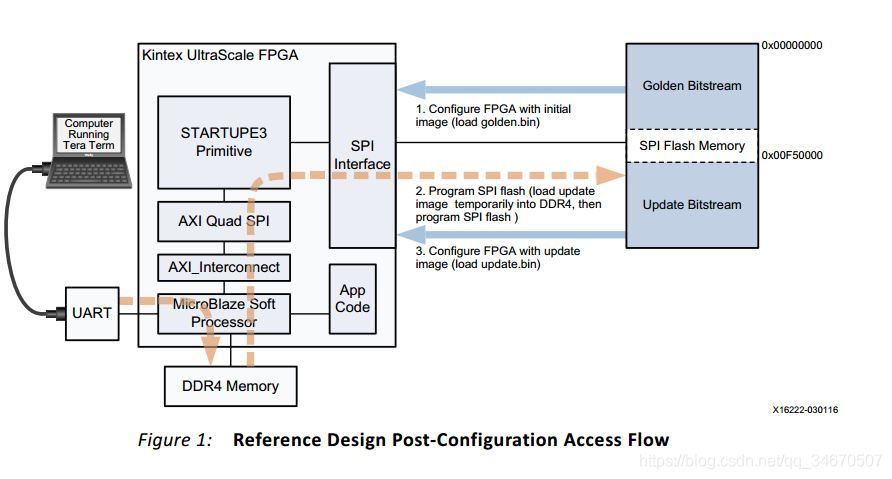

本应用中的参考设计使用MicroBlaze®软处理器内核连接到AXI Quad SPI内核,并使用STARTUPE3原语通过专用SPI接口实现对配置后的读写访问,以访问板载SPI闪存。 图1显示了配置后参考设计的操作。

程序的操作步骤如下:

step1:生成golden bitstream image (golden.bin),并存入Flash;

step2:生成 update bitstream image (update.bin)

step3:通过UART/Tera Term将update.bin存入相应的地址

step4:断电后上电update bitstream image(update.bin)重新配置FPGA

参考设计文件

推荐阅读

相关标签