- 1十四、事务——Undo日志_undo日志中的rollpoint指向哪里

- 2Hive之数据类型

- 3区块链——公有链,私有链,联盟链_区块链 公链 私链

- 4Spring不止AOP与IOC:Spring生态详解

- 5杭电和苏大计算机考研,江苏省各高校“排行榜”出炉,江苏大学10名开外,南大当属第一!...

- 6PostgresSQL存储过程和触发器_postgrel的存储过程和触发器怎么写

- 7Fucking on [non-breakable space] and [trailing space]

- 8git上传gitee(超过100MB的文件问题)_gitee lfs

- 92022信息安全保研_华科网安保研

- 10Java课程设计【学生信息管理系统】_学生信息管理系统java课程设计

AD9361从入门到入土系列----AD9361工作在LVDS模式下数据传输_ad9361软核lvds模式

赞

踩

因最近公司需要,借此机会和大家一起学习AD9361

制作不易,记得三连哦,给我动力,持续更新!

工程文件下载:纯硬件SPI配置AD9361 提取码:g9jy

目录

------------------------------------------------------------------------------

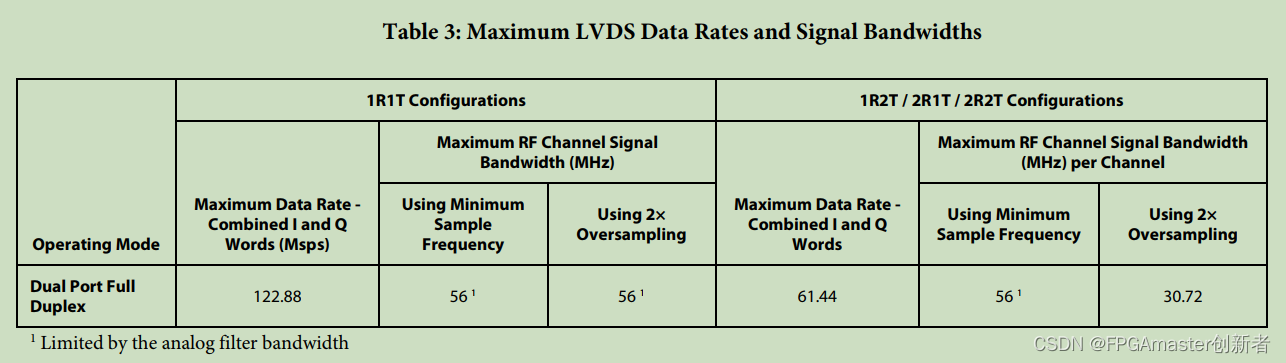

工作在LVDS模式下的最大时钟速率和信号带宽:

双端口全双工模式(LVDS)

双总线全双工LVDS模式通过写入SPI寄存器来启用。在这种模式下,P0和P1都作为LVDS信号使能,数据总线(D[11:0])被分成独立的子总线(RX_D[5:0]和TX_D[5:0])。每个子总线同时工作,允许BBP和AD9361之间的发送和接收数据全双工。传输数据(TX_D[5:0])、FB_CLK和TX_FRAME由BBP驱动,使得FB_CLK之间的建立和保持时间。

I和Q数据样本在每个数据总线上是时间交织的。

1R1T系统:

对于1R1T系统,I和Q采样以4路交错方式进行,如下所示:

对于这种情况,TX_FRAME和RX_FRAME信号与数据切换重合。当使能50%占空比成帧时,iMSB和QMSB分别处于高电平状态,iLSB和QLSB处于低电平状态。这些信号然后以iMSB再次切换为高电平,以指示新帧的开始。

2R2T系统:

对于2R2T系统,来自RF路径1和2的I和Q采样以8路交错方式传输,如下所示:

对于这种情况,TX_FRAME和RX_FRAME信号与数据切换重合。当使能50%占空比成帧时,每个i1MSB、Q1MSB、i1LSB、 Q1LSB处于高电平状态,i2MSB、Q2MSB、I2LSB和Q2LSB处于低电平状态。这些信号然后切换高低,以指示新帧的开始。

2R1T或1R2T系统:

在仅使用单个通道的路径中,每个数据组中的禁用通道的I-Q对是未使用的。AD9361忽略这些未使用的插槽。例如,对于使用TX信道1的2R1T系统,发送突发将有四个未使用的时隙,如下所示:

对于这种情况,TX_FRAME和RX_FRAME与数据切换重合,对于i1MSB、Q1MSB、I1LSB、Q1LSB为高电平,然后对于未使用的时隙为低电平。这些信号然后以i1MSB再次切换为高电平,以指示新帧的开始。未使用的"X"槽可以由BBP填充任意数据值。这些值可以是常数值,也可以重复前面的数据样本值,以减少总线开关因子,从而降低功耗。

1、发送数据:

发送数据样本以二进制补码格式进行,每个数据包中的第一个6位字节包含MSB,第二个6位字节包含LSB。最正的样本值为0x7FF,第一个字为0x1f,第二个字为0x3f,最负的值为0x800,第一个字为0x20,第二个字为0x00。TX_D[5]是最高有效位,TX_D[0]是每个字中的最低有效位。

2、接收数据:

接收数据样本以二进制的补码格式携带,每个数据包中的第一个6位字节包含MSB,第二个6位字 节包含LSB。这意味着最正的样本值是0x7ff,第一个字是0x1f,第二个字是0x3f,最负的值是0x800,第一个字是0x20,第二 个字是0x00。RX_D[5]是最高有效位,D[0]是每个字中的最低有效位。

3、 说明:

时序图中的差分数据用实线和虚线绘制,以说明数据线的差分性质。正腿的实线与差分对的负腿的实线匹配,正腿对的虚线与负腿的虚线匹配。注意,因为2R1T和1R2T系统遵循2R2T时序图,所以从这些图中省略它们。

下期更新,AD9361串行外设接口(SPI),以及讲解!