- 1西安华为OD面试经验(德科)_华为od背调

- 2python入门14:os库,遍历文件夹下的所有文件,一些常用函数(获取文件目录、判断文件是否存在、合并路径、删除文件等),以及应用举例_os库遍历删除文件

- 3在linux操作系统上安装sqlserver_linux安装sqlserver

- 4【机器学习】Exam4

- 5UniApp与React的比较:移动应用开发框架的对比_uniapp react

- 6ComfyUI + Stable Diffusion 3(Windows 11)本地部署教程_stable diffusion 3.0 windows本地部署

- 7运行stable-diffusion出现的问题_checkout your internet connection or see how to ru

- 8如何降低AI辅写疑似度?7招助你论文过关!_aigc论文降低

- 9MySQL索引的正确使用姿势_mysql index lookup

- 10Visual Studio Code 常见的配置、常用好用插件以及【vsCode 开发相应项目推荐安装的插件】_vscode structure

FPGA之旅设计99例之第十九例----OV5640上电及初始化_ob5460 fpga

赞

踩

一. 简介

在上例中,介绍了配置OV5640所需的SCCB时序,以及具体的实现。本例将介绍与初始化相关的重要寄存器,以及上电时序。

OV5640的寄存器非常多,从它的寄存器的地址为16bit就可以看出,在商家提供的一些例程中,可以看到配置寄存器的语句多达200行,无法一时间学习掌握所有的寄存器。所以只需要掌握一些重要即可,例如控制图像输出格式、控制图像输出大小、控制图像输出帧率的寄存器。下面就开始介绍吧

完整程序关注微信公众号 FPGA之旅 回复 FPGA之旅设计99例之第十九例 获取下载链接

二. 重要寄存器讲解

一般来说,只需要了解三大类寄存器即可 : 时钟PCLK输出频率寄存器 , 图像输出大小寄存器 , 图像输出格式寄存器

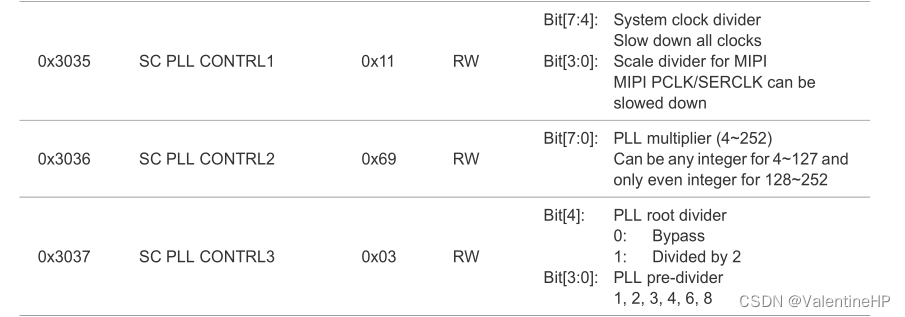

(1). 时钟PCLK输出频率寄存器

PCLK时钟主要由0x3035 - 0x3037三个寄存器控制(其余寄存器也有,可以不看),详情如下,一般来说完整的配置参数会给你配置到48MHz / 84MHz,如果想要配置成其他的频率,可以调整0x3036寄存器的值即可。具体是怎么对应的话,手册上好像没有给出。

(2). 图像输出大小寄存器

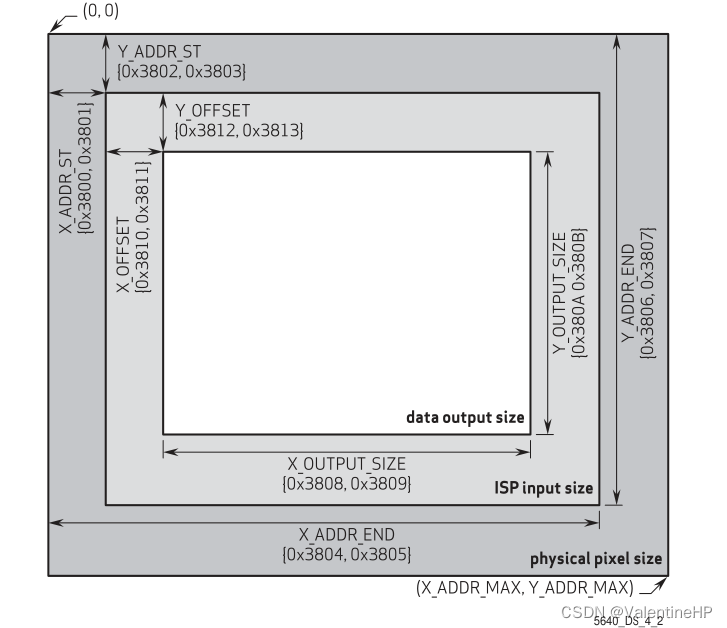

这部分比较关键,同时也比较容易,看下面这张图片即可,physical pixel size为物理感光的尺寸,也就是摄像头能够感光的大小。ISP input size为图像处理单元输入的大小,由物理感光的尺寸经过一定的处理,输入进ISP进行处理,data output size 为实际摄像头输出的像素大小,为经过ISP进行处理缩放之后的图像数据。

在实际使用的过程中,只需要关心data output size的大小即可。即只需要配置0x3808-0x3809 和0x380a-0x380b四个寄存器即可。

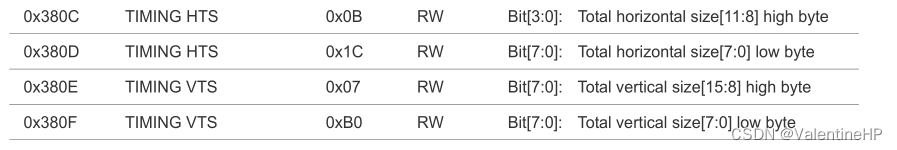

另外,有四个寄存器也是需要关注的,0x380c-0x380f,这四个寄存器分别配置水平输出的像素总个数,以及竖直输出像素的总个数,这个配置要比data output size要大,和VGA的行列消影类似

(3). 图像输出格式寄存器

这个配置只需要配置0x4300寄存器即可,类别比较多,可以自行查看手册。

以上需要关注的寄存器,都是在其他寄存器配置好的前提下,然后进行修改。完整的寄存器配置可以去正点原子或者GitHub上copy,本例使用的是在GitHub上copy下来的。

三. 上电时序讲解

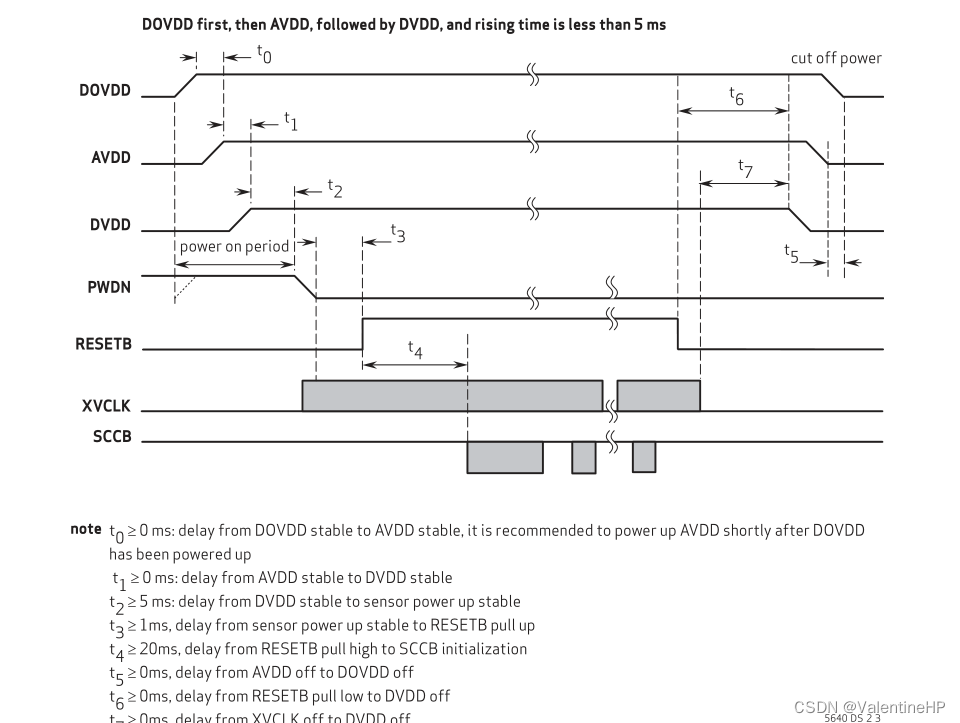

这部分在手册中以给出,通过下图,可以看出,还是比较容易的。初始化时序只需要看到t4结束,后面就不要管了,后面是掉电时序。

第一步. 上电后,将PWDN拉高,RESETB拉低

第二步. 延时大于等于t2(5ms)时间后,将PWDN拉低,并且一直保持

第三步. 在延时大于等于t3(1ms)时间后,将RESETB拉高,将PWDN拉低,并且一直保持

第四步.最后延时t4(20ms),完成上电

完成上电后,即可开始SCCB对寄存器进行初始化

四. 程序介绍

程序主要包括三个部分,上电时序,然后是寄存器初始化,最后就是接收图像数据了。这部分比较容易,就不做介绍了。

always@(*)

begin

case(state)

S_POWER_UP:

if( ov5640_powerup_ack == 1'b1 )

next_state <= S_INIT;

else

next_state <= S_POWER_UP;

S_INIT:

if( ov5640_init_ack == 1'b1 )

next_state <= S_WORK;

else

next_state <= S_INIT;

S_WORK:

next_state <= S_WORK;

default : next_state <= S_POWER_UP;

endcase

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

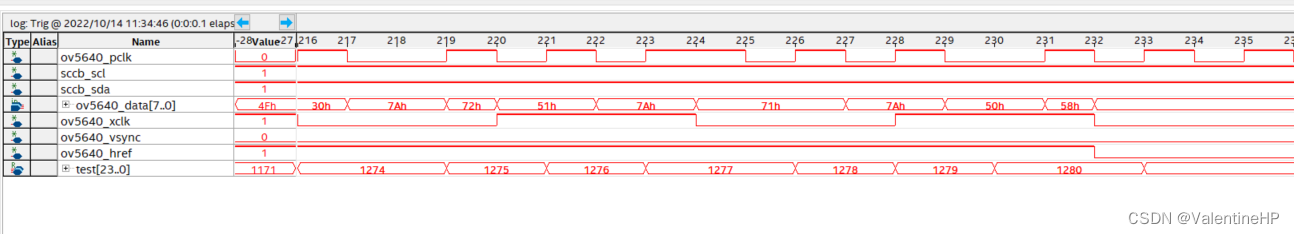

最终ov5640配置为640 x 480 大小的输出,通过逻辑分析仪可以看到每一行输出1280个数据,也就是640个像素点(每次输出8bit,两种时钟输出一个完整的RGB565数据)。

完整程序关注微信公众号 FPGA之旅 回复 FPGA之旅设计99例之第十九例 获取下载链接,最终将图像显示在VGA显示器上,没有经过存储,仅测试使用,后期将加上SDRAM或者DDR存储器。