热门标签

热门文章

- 1基于SpringBoot+Vue实现的仿掘金论坛系统(包含完整源码以及部署教程)

- 2设备巡检管理系统,为企业降本增效_设施设备运维巡检系统

- 3vue使用国密SM4进行加密、解密

- 4解决安装Fiddler后无法上网的问题_安装fiddler后电脑无法上网

- 5五子棋-单机游戏-微信小游戏项目开发入门_小程序游戏代码game.js

- 6云计算虚拟化技术:颠覆传统,引领未来之争_服务器虚拟化,网络虚拟化,存储虚拟化

- 7毕业设计:python图书推荐系统+可视化+协同过滤推荐算法+Django框架(源码)✅_基于python的图书推荐系统毕业设计

- 8数据仓库——ETL(详细教程)_etl教程

- 9docker搭建mysql 主从复制_operation create user failed for 'master-slave1'@'

- 10JS混淆基本类型和原理_js 常见混淆方式

当前位置: article > 正文

Quartus-II13.1三种方式实现D触发器及时序仿真_quartus ii 13.1

作者:正经夜光杯 | 2024-07-10 06:22:46

赞

踩

quartus ii 13.1

一、Quartus-II输入原理图及时序仿真

(一)创建工程

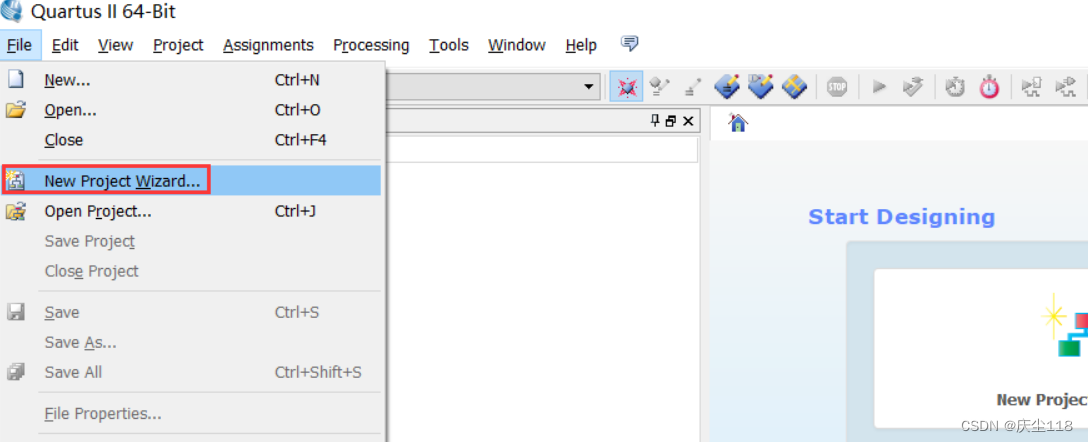

File->New Project Wizard

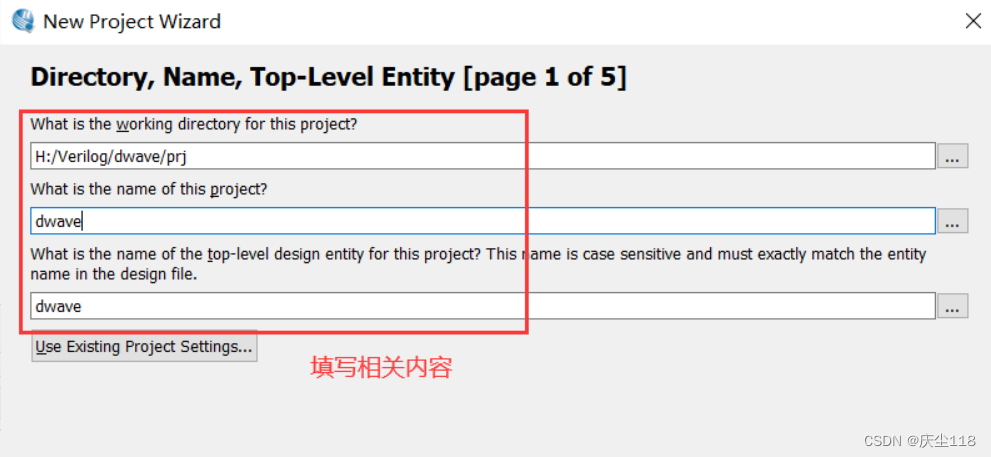

填写工程名称

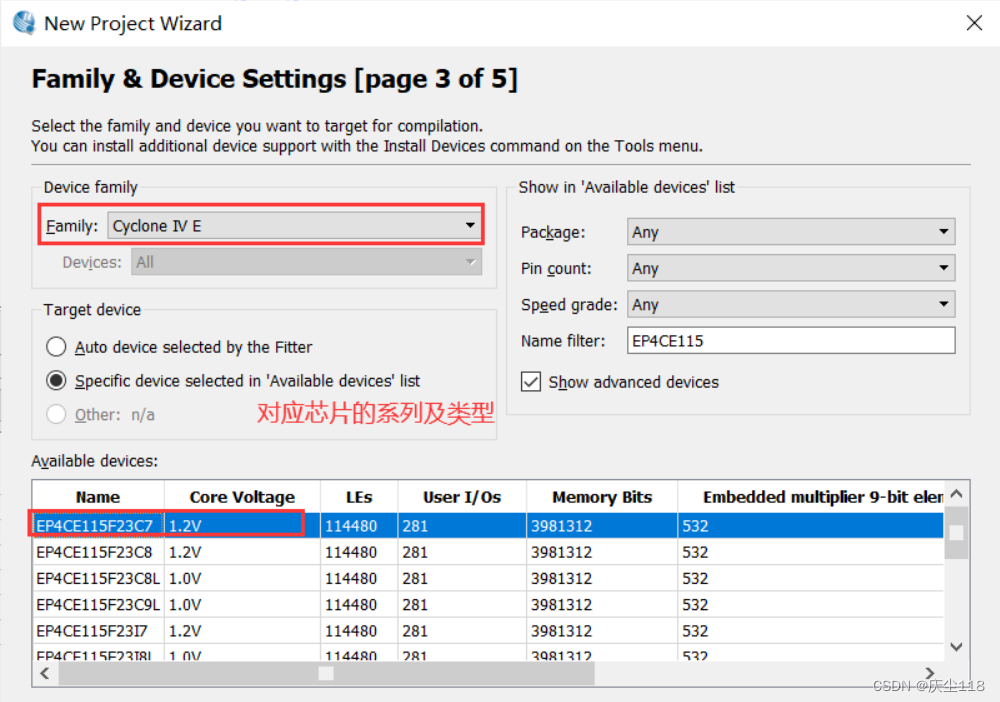

根据使用的FPGA,进行选择芯片系列及类型

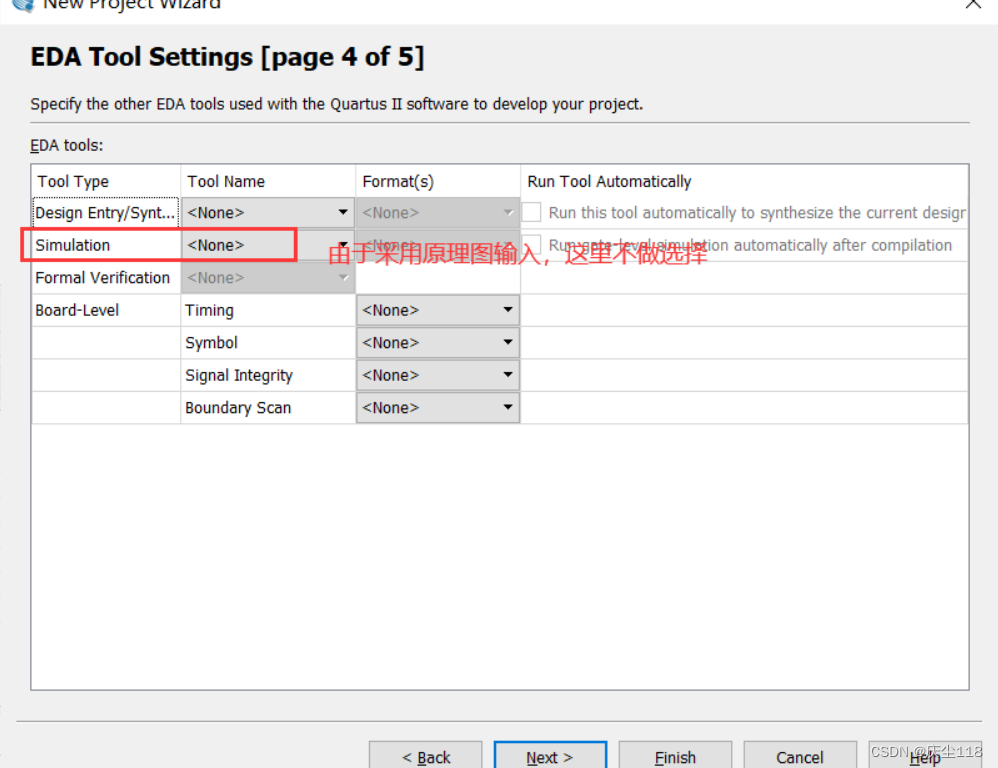

直接Next

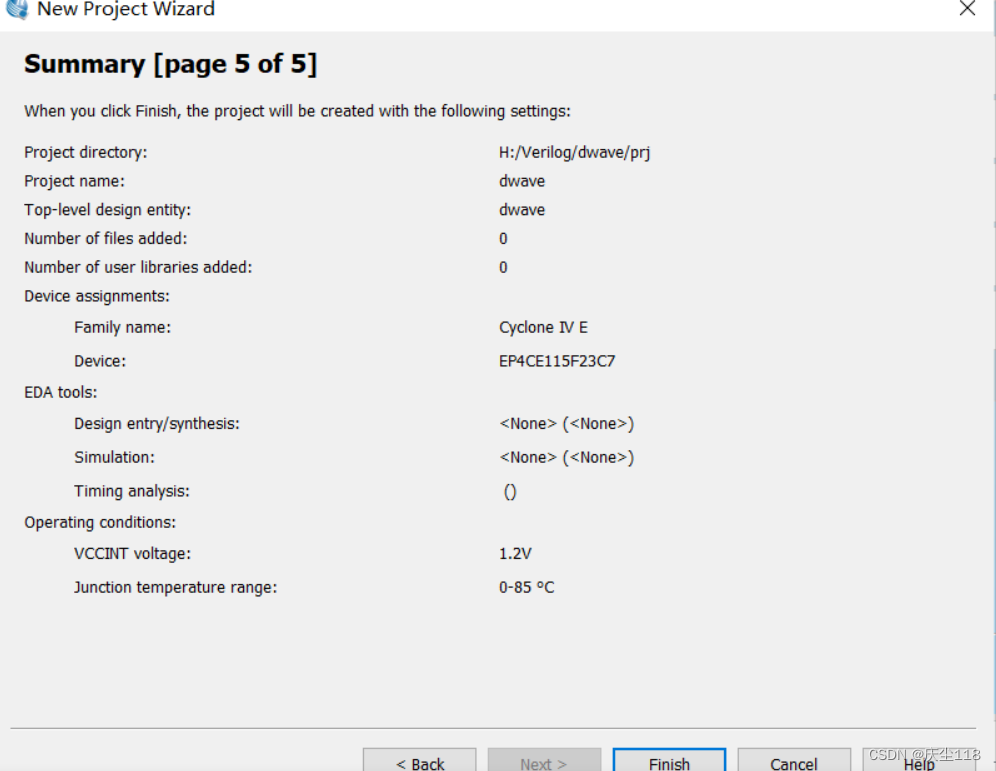

完成工程创建,点击Finish

(二)创建方框文件

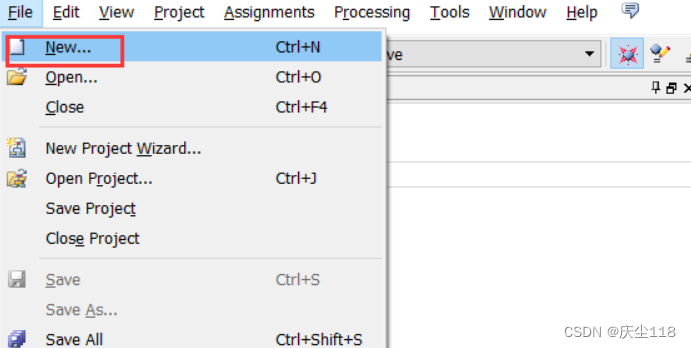

选择New

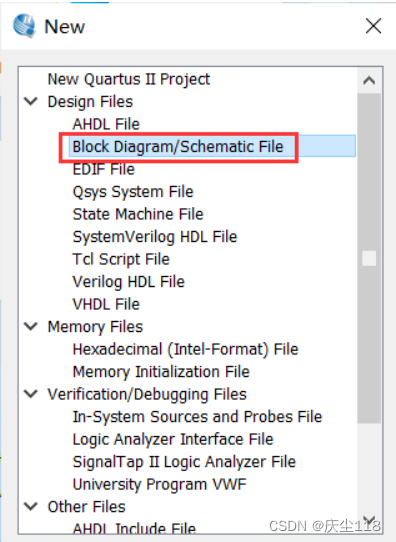

选择Block Diagram/Schematic File

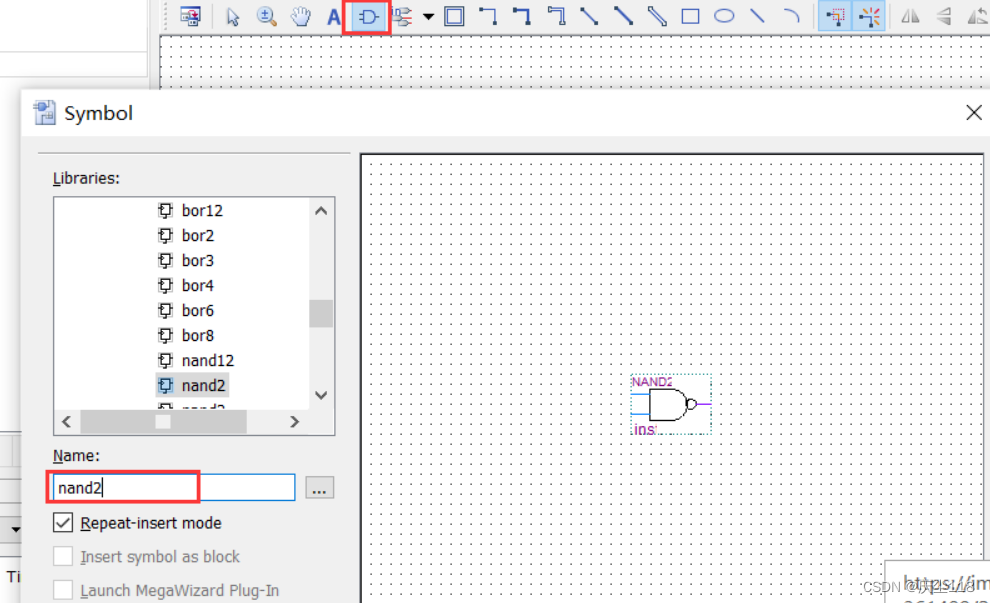

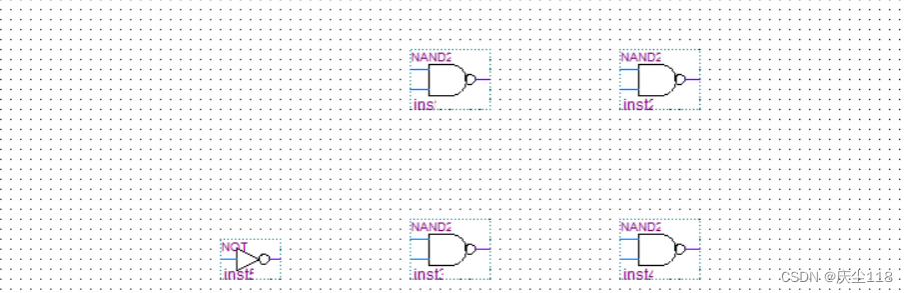

选择nand2,二个输入的与非门,依次添加四个and2和一个非门not

添加完成

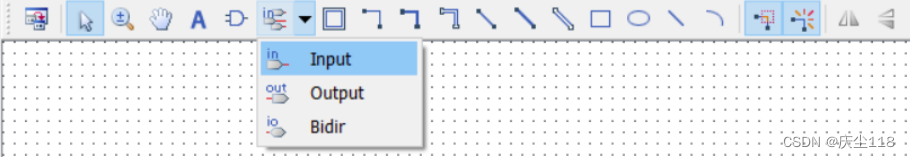

选择连线工具

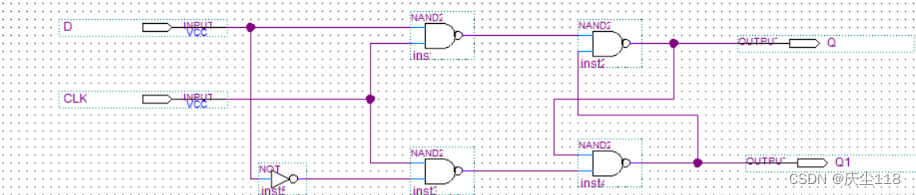

连线效果

(三)编译原理图文件

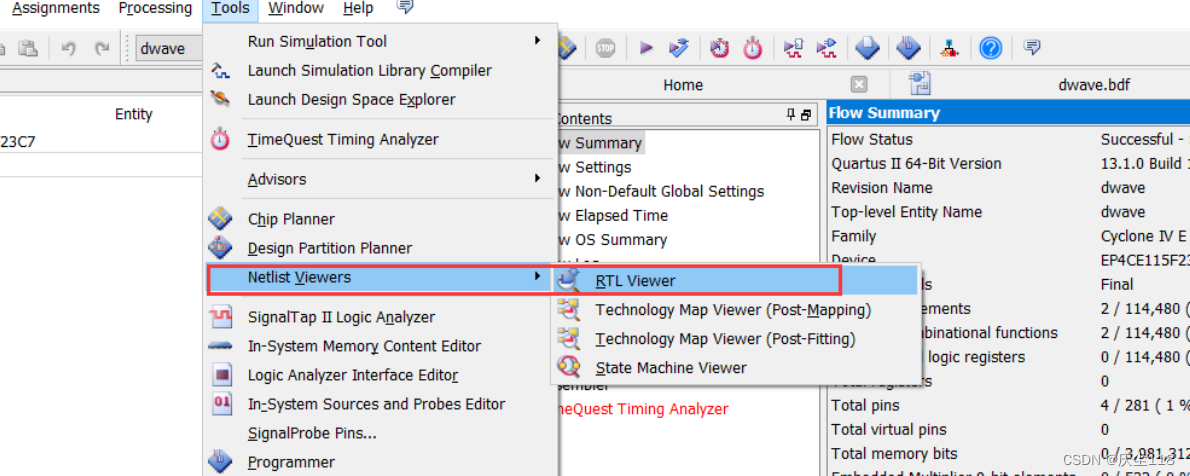

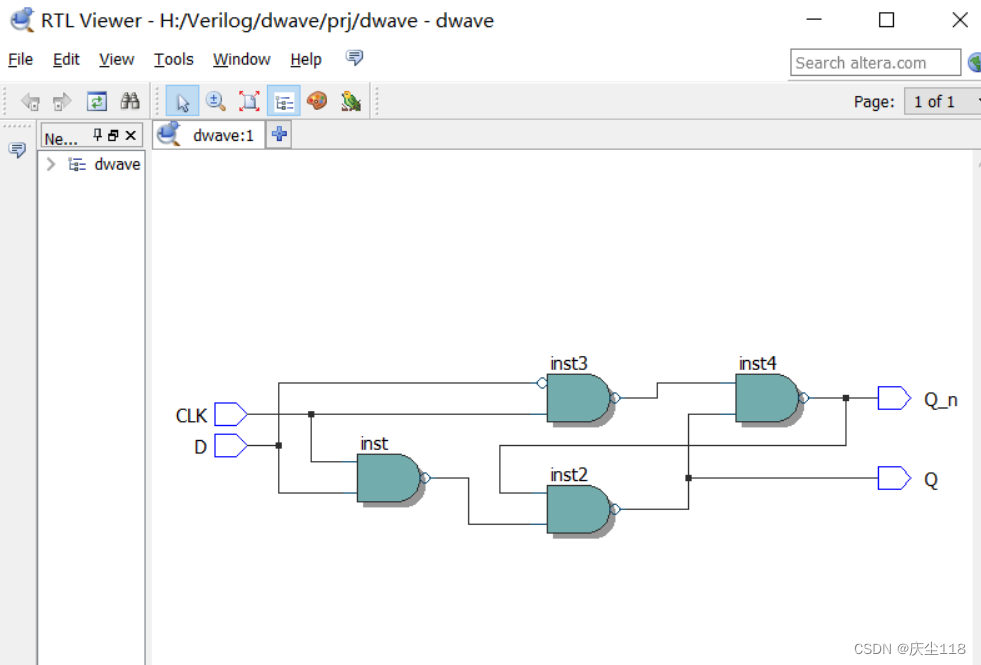

启动分析与综合(全编译) RTL Viewer,查看硬件电路图

硬件电路图

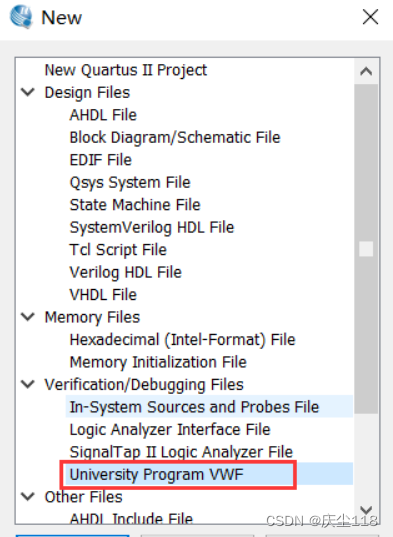

(四)创建vwm格式波形文件

选择VWF

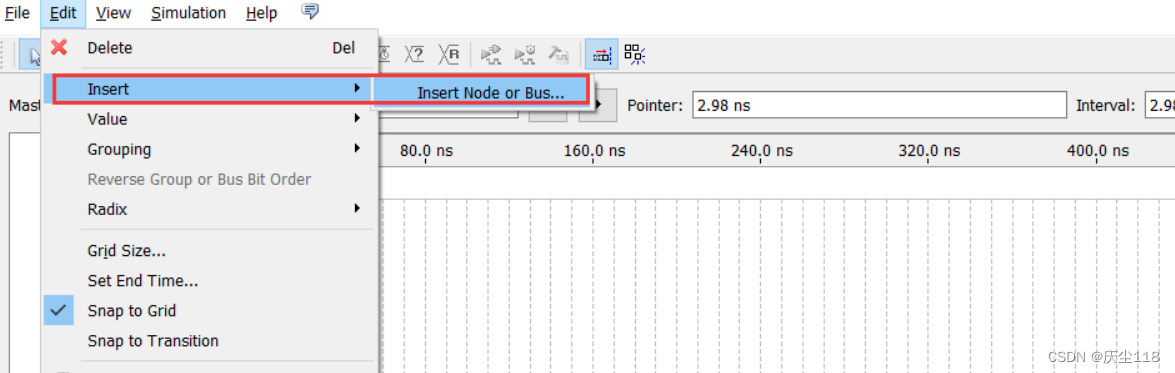

选择Edit->Insert->Insert Node or Bus

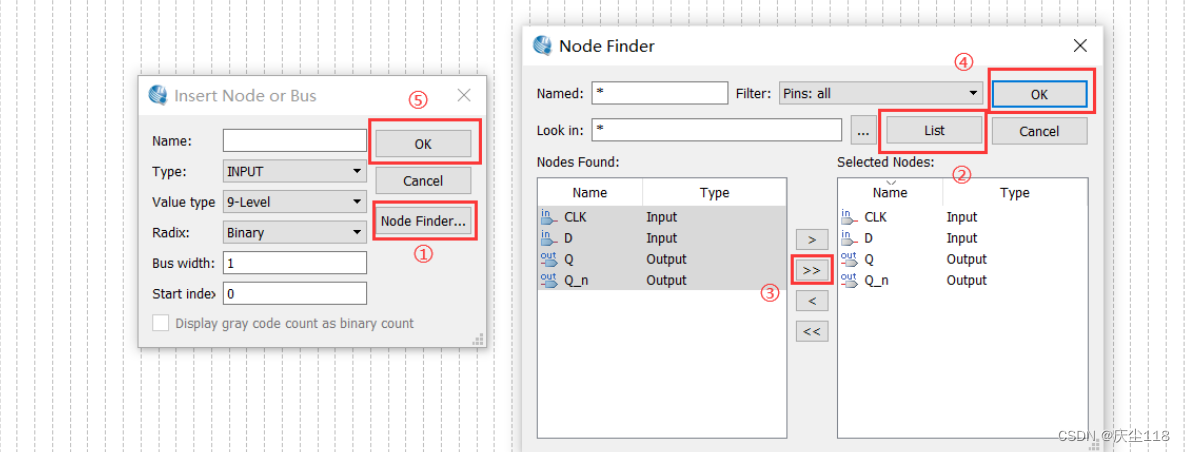

添加Node or Bus

添加效果

编辑输入Clk,产生时钟信号

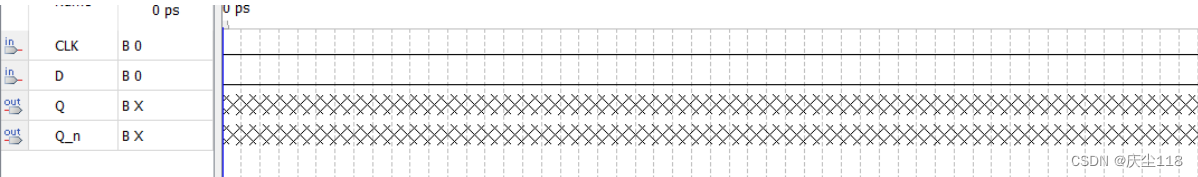

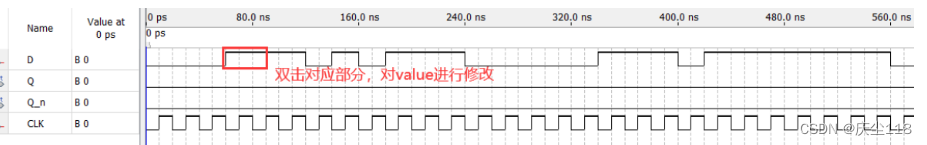

鼠标选择D,Q信号Q_n,,进行编辑

(五)时序波形仿真

功能仿真后的波形,满足D latch的时序(全编译后,也可以运行时序仿真)

点击时序仿真,仿真结果如下

二、Quartus-II用Verilog语言实现D触发器及时序仿真

(一)创建工程

方法同上

(二)编写Verilog文件

创建Verilog文件 点击File->New,选中Verilog

代码如下

//dwave是文件名 module dwave(d,clk,q); input d; input clk; output q; reg q; always @ (posedge clk)//我们用正的时钟沿做它的敏感信号 begin q <= d;//上升沿有效的时候,把d捕获到q end endmodule

保存文件并编译

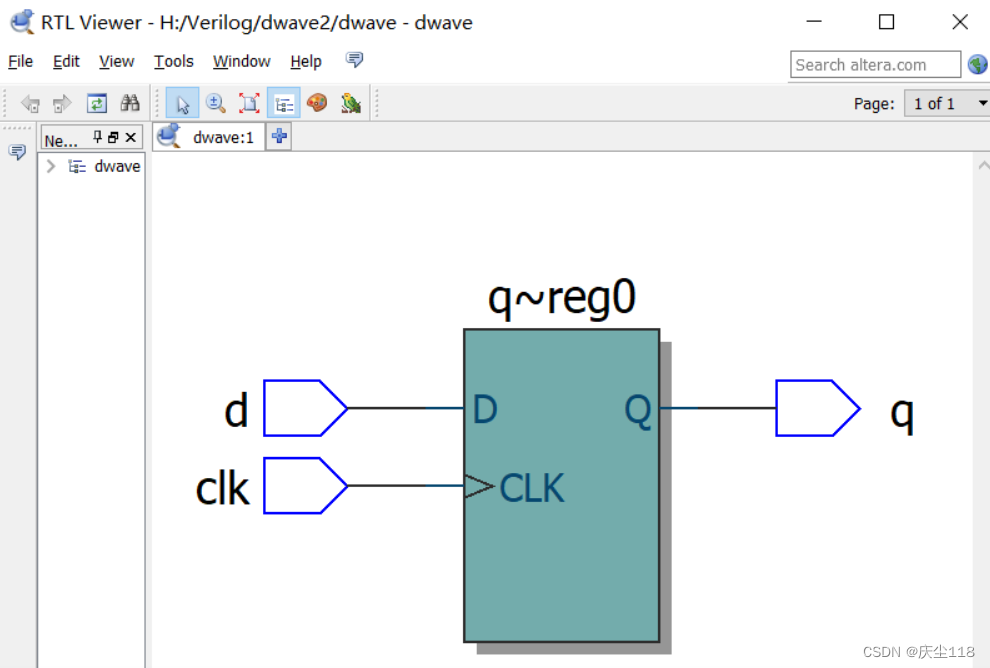

(三)查看生成的电路图

使用rtl viewer查看硬件电路图 硬件电路图

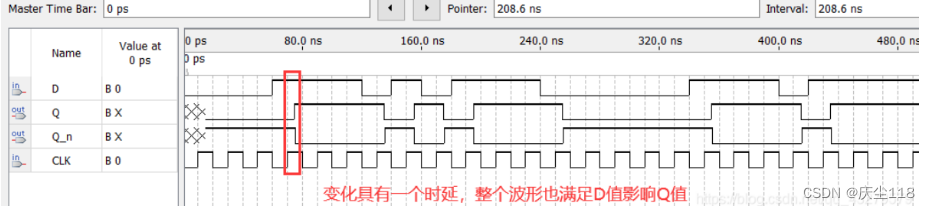

(四)利用Verilog语言编写测试代码实现时序仿真

具体仿真过程,参考链接: Modelsim SE版本的安装及使用方法-CSDN博客 测试代码

//测试代码 `timescale 1ns / 1ns module dwave_tb; reg clk,d; wire q; dwave u1(.d(d),.clk(clk),.q(q)); initial begin clk = 1; d <= 0; forever begin #60 d <= 1;//人为生成毛刺 #22 d <= 0; #2 d <= 1; #2 d <= 0; #16 d <= 0;//维持16ns的低电平,然后让它做周期性的循环 end end always #20 clk <= ~clk;//半周期为20ns,全周期为40ns的一个信号 endmodule

仿真效果

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/正经夜光杯/article/detail/805117

推荐阅读

相关标签