热门标签

热门文章

- 1【Dopi Micropython 视觉AI应用开发教程】【实验4】获取摄像头数据_micropython 网络摄像头

- 2linux安装搜狗输入法后无法输入中文_linux搜狗输入法无法输入中文

- 3MySQL-DATE_FORMAT()函数_mysql日期格式化函数

- 4黑马头条(学习笔记)

- 52024年前端最全js数组去重的10种有效方法 vue 数组去重,阿里前端一面_前端数组去重

- 6GPT实战系列-LangChain的Prompt提示模版构建_gpt prompt模板

- 7Solana之旅3:PoH_solona 共识机制

- 8Java二分查找算法

- 9【AI人工智能】文心智能体 - 你的专属车牌设计师

- 10算法竞赛入门经典(第二版)第三章习题_dna consensus string 卜东波

当前位置: article > 正文

stm32和FPGA的SPI_32与fpga spi通信复位后数据

作者:木道寻08 | 2024-07-30 23:46:46

赞

踩

32与fpga spi通信复位后数据

step1 stm32_3pin_to_fpga_input

fpga_spi_input

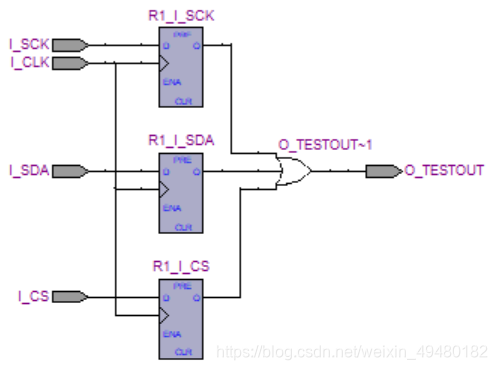

简单用CS ,CLK,SCLK控制SDA输出

输出:assign O_TESTOUT = R1_I_CS | R1_I_SDA| R1_I_SCK;

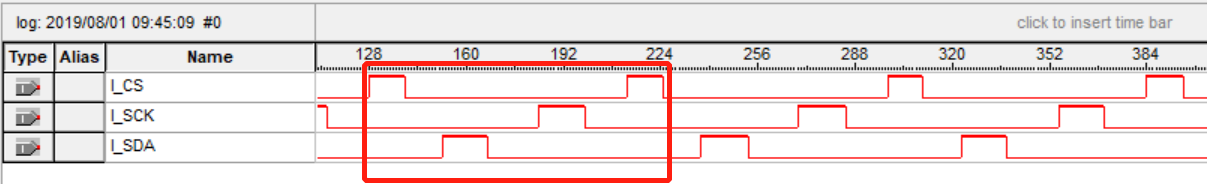

stm32_gpio_wave_3pin

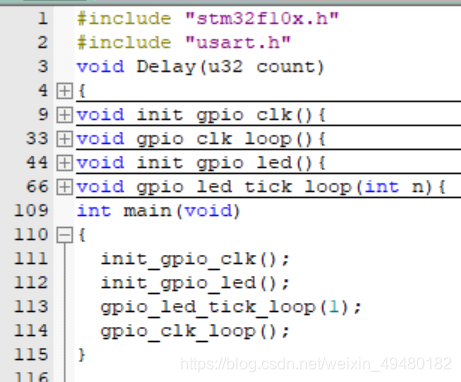

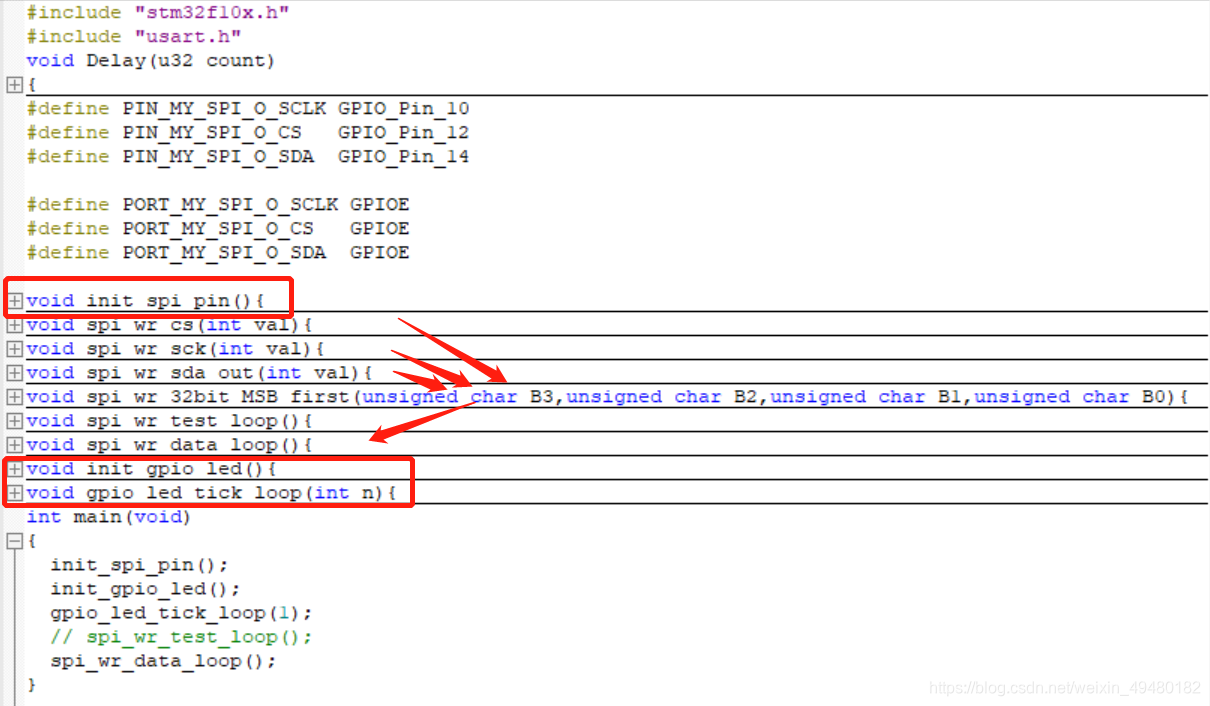

对main函数中使用到的函数进行定义,有初始化时钟、引脚的,对时序设置的,在main函数中只通过引用函数来实现功能

step2 stm32_spi_to_fpga_input

fpga_spi_input

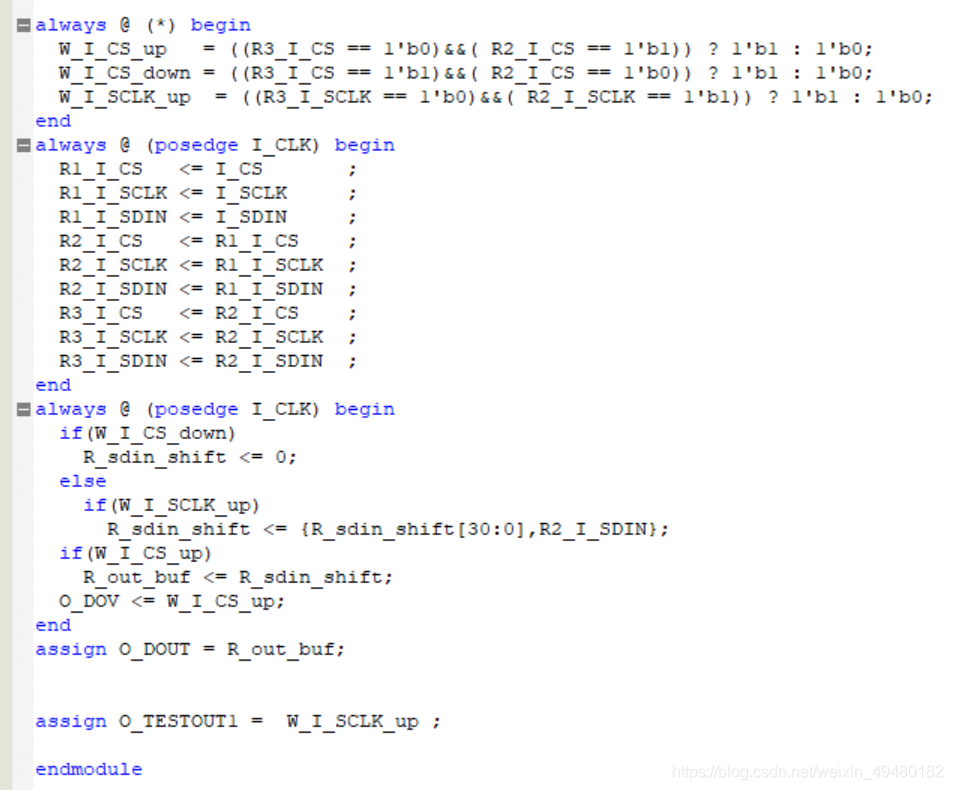

对CS、SCLK的下降沿,上升沿的判断,使用?:来幅值给W_I_CS_UP这几个变量。CS、SCLK用多个D触发器就是为了判断两个时间周期里面是否发生跳变,是什么跳变。同时为了时钟同步,对CLK也做多级D触发器。

在CS的下降沿读入串行的IN,经过SCLK上升沿的移位后在CS的上升沿幅值给buf变量后并行输出,这个程序是32位输出的。

stm32_spi_to_fpga_input

与step1相同的是初始化和LED时序

输出32位数据,要分成4次,每次8位

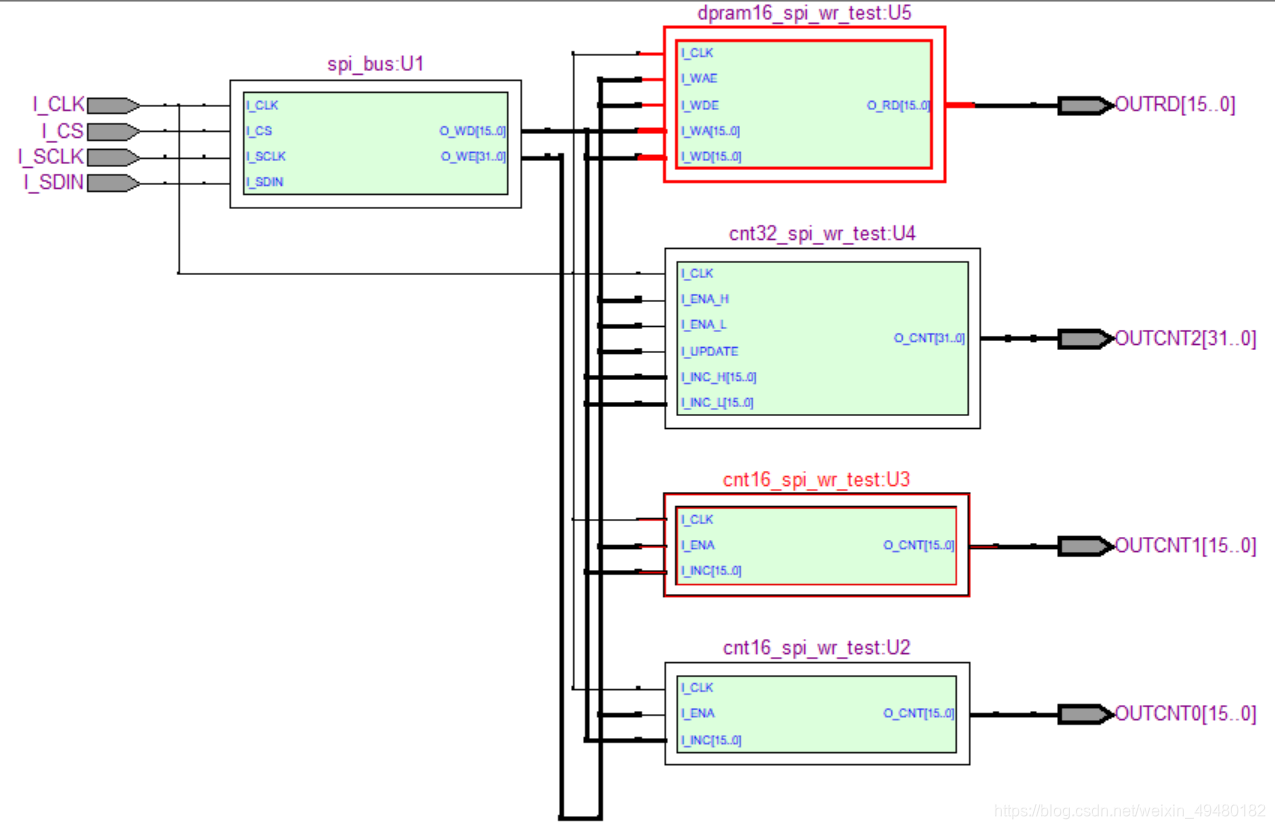

step3 stm32_spi_write_fpga_addr_decode

fpga_spi_input_bus_addr_decode

RTL视图

module spi_bus(// I_CLK , I_CS , I_SCLK , I_SDIN , O_WD , O_WE , O_TESTOUT1); input I_CLK ; input I_CS ; input I_SCLK ; input I_SDIN ; output [16-1:0] O_WD ; output [32-1:0] O_WE ; output O_TESTOUT1; wire[32-1:0] W_U_spi_O_DOUT; wire W_U_spi_O_DOV ; spi_in_to_parallel_data_out U_spi_s2p( .I_CLK (I_CLK ), .I_CS (I_CS ), .I_SCLK (I_SCLK), .I_SDIN (I_SDIN), .O_DOUT (W_U_spi_O_DOUT), .O_DOV (W_U_spi_O_DOV ), .O_TESTOUT1()); wire [16-1:0] W_U_dec_O_DAT; wire [32 -1:0] W_U_dec_O_DOV; addr_decode U_decode( .I_CLK (I_CLK ), .I_ENA (W_U_spi_O_DOV ), // input enable .I_DIN (W_U_spi_O_DOUT[15: 0]), .I_AIN (W_U_spi_O_DOUT[31:16]), .O_DAT (W_U_dec_O_DAT ), .O_DOV (W_U_dec_O_DOV ), .O_TESTOUT1 ()); assign O_WD = W_U_dec_O_DAT; assign O_WE = W_U_dec_O_DOV;

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

stm32_spi_to_fpga_bus_addr_decode

#step4 stm32_spi_read_select_write_fpga_addr_decode

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/木道寻08/article/detail/905874?site

推荐阅读

相关标签