- 1postman接口参数化设置,满满干货指导_postman参数设置

- 2SwiftUI AI教程之 在 Xcode 中为 RealityKit SwiftUI 项目设置 MVVM

- 3Apollo :架构演化_apollo软件架构

- 4Win10设置vs2010总是以管理员身份运行_vs2010以管理员权限调试

- 5Python爬虫第一战 爬取小说_python爬取小说的代码

- 6Ubuntu 22.04下Java环境的搭建(含多版本一键快速切换)_ubuntu java

- 79.5 Python csv 文件的写入操作_python csv写入

- 8使用 HTML、CSS 和 JS 创建在线音乐播放器(含免费完整源码)(1)_html音乐播放器源码

- 9Spring高手之路20——深入理解@EnableAspectJAutoProxy的力量_aop注解生效

- 10PX4从放弃到精通(一):开源飞控PX4简介+系列文章大纲

systemverilog学习 --- modport and assertion(1)_systemverilog modport

赞

踩

modport

在sysemverilog中,modport用来确定在接口中信号的方向。在interface中,使用关键字modport来声明。

- 确定端口的方向,并对其访问进行限制

- 声明为input的信号不准许驱动drive和赋值assign

- interface可以由任意数量的modport,interface中的wire可以加入到不同的modport中

- modport可以有input,inout, output和ref来修饰方向

interface my_intf;

logic a;

logic b;

//modport declaration

modport driver(input a, output b);

modport monitor(input a, input b);

endinterface

- 1

- 2

- 3

- 4

- 5

- 6

- 7

上例中,模块连接时,输入输出是互相的,一个模块的输入可能是另一个模块的输出。

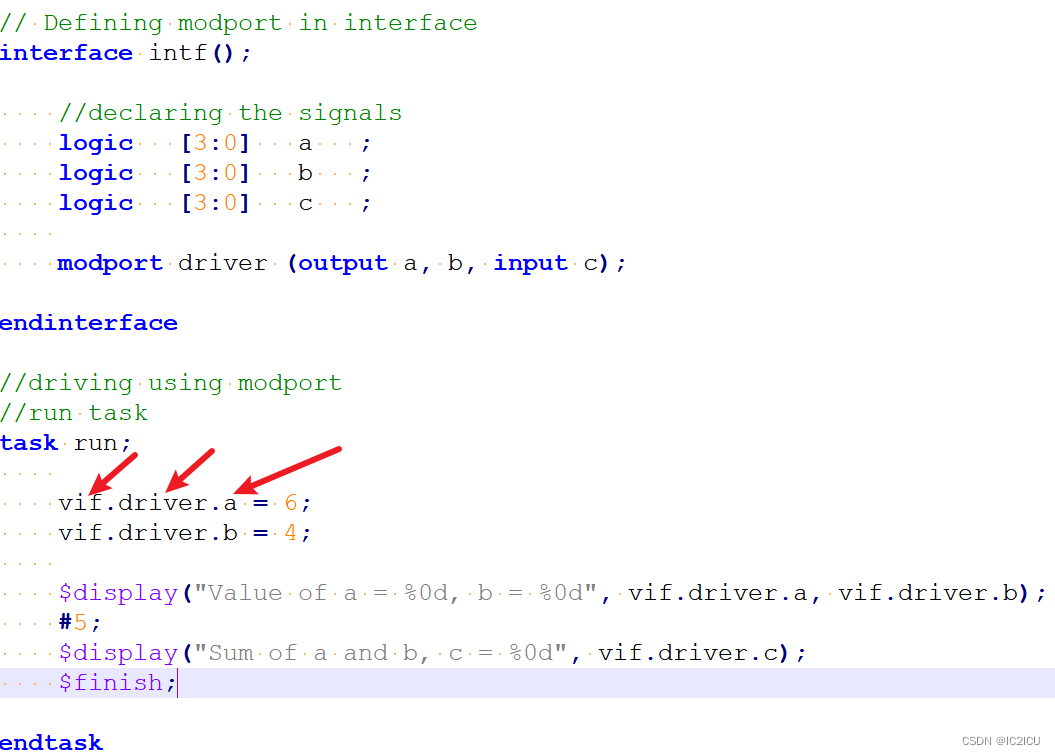

如果要访问modport的信号,形式如下,层次结构一般通过.逐层访问。下面的例子,对于driver而言,驱动a和b,然后dut返回c。

clocking

clocking块指的是一组信号的时序和同步关系。clocking块:

- 为DUT和testbench提供同步化的参考。

- 这组信号将会被testbench所采样和驱动。

- 相对于clock event的时序,testbench将会使用来驱动和采样信号。

- clocking块可以在interface,module和program块中进行声明。

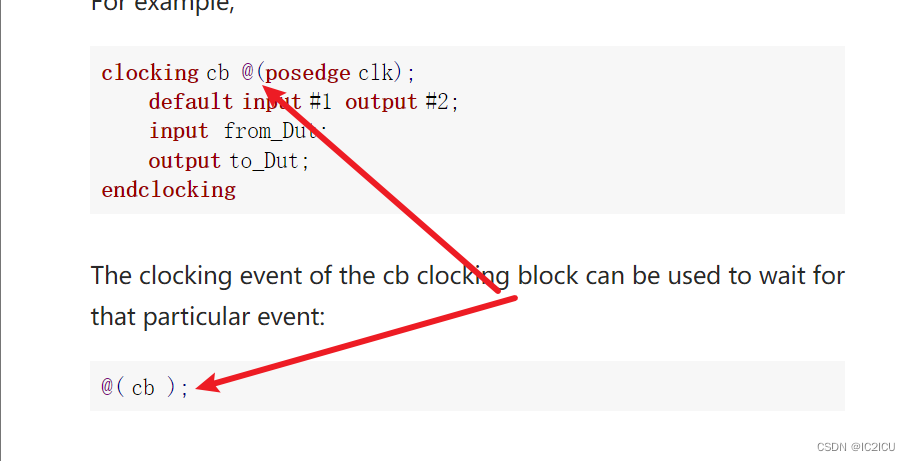

clocking cb @(posedge clk);

default input #1 output #2;

input from_Dut;

output to_Dut;

- 1

- 2

- 3

- 4

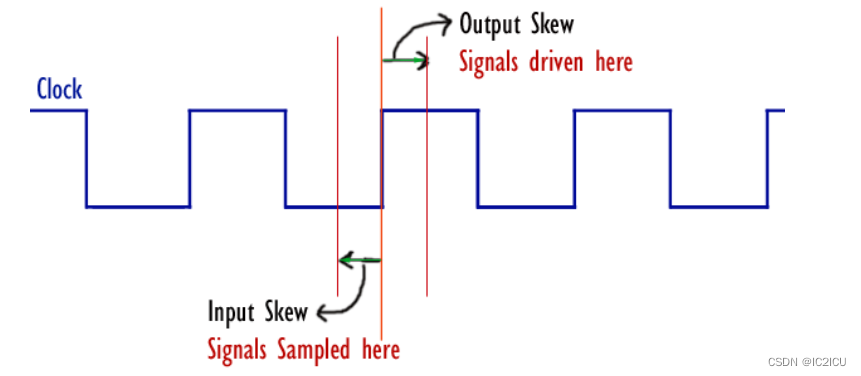

@(posedge clk)是clocking event,用来同步clocking块。from_Dut和to_Dut就是clocking signal。而时序时间是我们指定的延时,就是这里#1,#2.对于输入输出的理解如下图所示:

即输入信号在时钟上升沿(这里的event)提前一点时间到来,之后要在时钟上升沿后保持一段时间,可以认为这模拟了信号的建立和保持时间。需要注意的是,延时值是一个常量表达式,并且可以用参数表示,如果没有指定时间单位,则使用当前的时间单位(与tb中`timescale有关)。

我们可以通过clocking块的名字来直接访问clocking event,不用考虑实际的clocking event。下图中的@(cb)直接等价于@(posedge clk)。

有时,延时可能以时钟的周期为单位,不是以延时的时间为单位,此时我们便可以使用##操作符,表示延时以周期或者clocking event为单位。

## 8; // wait 8 clock cycles

## (a + 1); // wait a+1 clock cycles

- 1

- 2

assertion 介绍

assertion最初用来验证设计的行为。是在仿真中嵌入或者黏附于设计的检查,即在设计中加入的检查。一旦特定的条件或者事件序列出现时,就会产生警告或者错误信息。

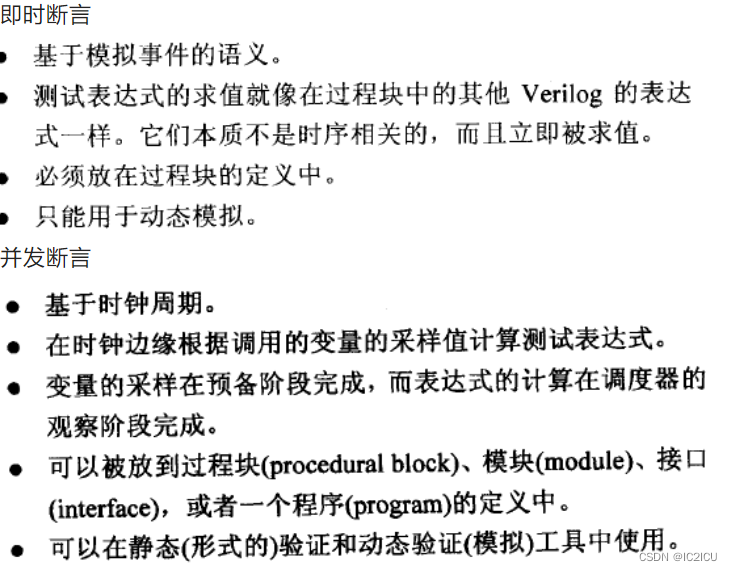

使用断言,我们可以检查特定条件下或者事件序列的发生,并提供功能覆盖率。断言可以分为immerdiata assertion和concurrent assertion。前者检查当前仿真时刻的条件,后者检查在多个周期内的事件序列。

immediate assertion

即时断言,和if-else类似,需要在过程块中定义。实例如下:

label:assert (expression) action_block;

- 1

其中label是可以选择的,用于给断言语句取个名字。assert是关键词。expression被评价(执行完之后),会立即执行action_block。action_block指明了断言是成功了还是失败了,应该怎么做。

pass_statement;else fail_statement;

- 1

action_block由两部分组成,当expression为真时,执行pass_statement,反之执行fail_statement语句。而且pass_statament和fail_statement都是可以选择的。

既然是断言,那么一些事情必然满足,断言失败可能会带来严重的后果。在默认情况下,断言失败的后果是一个error。当然也可以通过不同的系统函数来指出后果的严重等级。

- $fatal:是一个run-time fatal。

- $error:是一个run-time error.

- $ warning:是一个run-time running。

- $info:表示这次断言失败没有任何严重的后果。

但是如果断言语句没有给出else的分支,那么工具将会默认调用 $error函数。

下面是一些断言的例子:

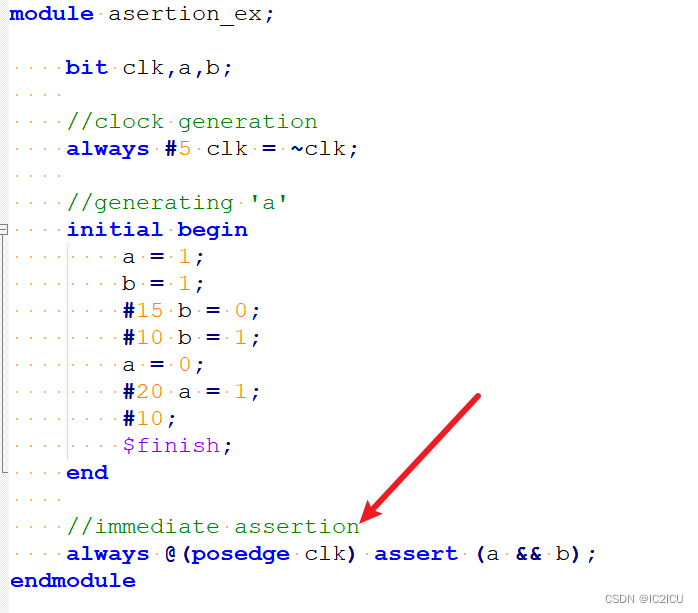

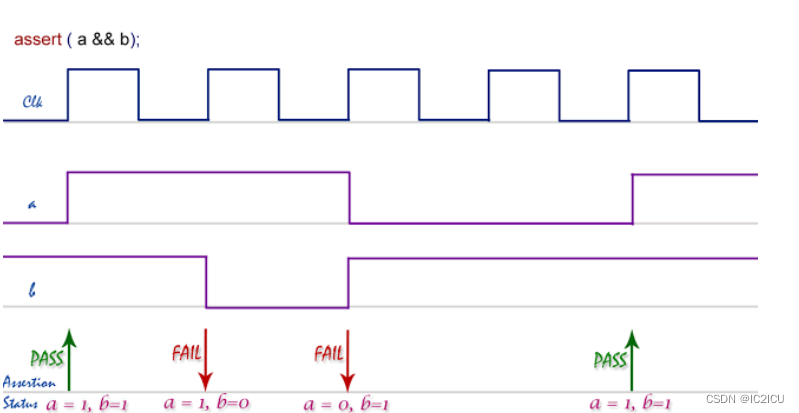

来看一个实例:

断言是在always语句块中,并且pass_statement和fail_statement都没有给出,在每个时钟的上升沿都会检查a和b是不是同时为1。如果不满足则会导致断言失败(默认调用 $error函数 )。

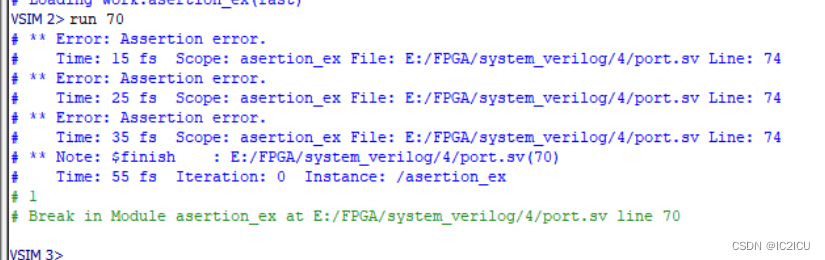

执行结果如下:

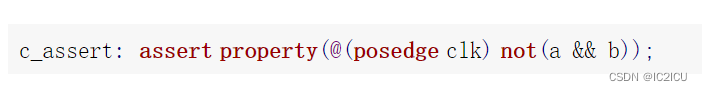

concurrent assertion

并发断言用来处理分布在多个时钟周期的事件序列,处理时序和信号之间的配合,可以放在module,interface和program中。

可以看出多了个property的关键字。