- 1配置jupyter连接服务器_jupyter 连接服务器

- 2大数据分析技术之MapReduce实践:词频统计(九)_通过编写mapreduce词频统计程序心得体会

- 3Android 原生定位开发(解决个别手机定位失败问题)

- 4Python-split()和split(‘ ‘)的区别_split()和split(' ')的区别

- 5以太坊DAPP[3]-×××-react特性与×××合约实例

- 6泰坦尼克号—数据分析(单因素、多因素分析)_泰坦尼克号数据分析

- 7perl 循环截取字符串_perl语言 split 循环

- 8Windows11环境下使用docker配置kafka的学习记录_windows docker kafka

- 9Transformer得到的图像attention map可视化,同时叠加到原图

- 10NLP 的数据预处理步骤,一文掌握_文本分类任务中的数据预处理部分

【ZYNQ-7000】从简易流水灯看FPGA开发的一般流程_zynq7000 verilog教程

赞

踩

【前言】

前不久刚刚放寒假,被万恶的期末考试折磨的半死。为了奖励自己,买了新玩具----ZYNQ7010开发板。不得不说,板子小巧精致,布线很符合我的审美,哈哈哈。写篇文章复习一下基于vivado的FPGA的一般开发流程吧。

【开发环境】

- Vivado 2019.1

- ZYNQXC7Z010

【开发流程】

1.新建工程

打开Vivado,Create Project

进入新建工程向导后next,编辑工程名称和工程目录

注意这里的工程保存的目录越短越好,因为Vivado不支持长目录

选择RTL设计,意味着逻辑、布线、IP核等等sources都由自己添加。

当然如果有现成的设计文件也可以选择其他。

添加设计文件,这里我们选择在工程新建后添加,所以这里直接跳过。

添加约束也是如此,新建工程之后再添加

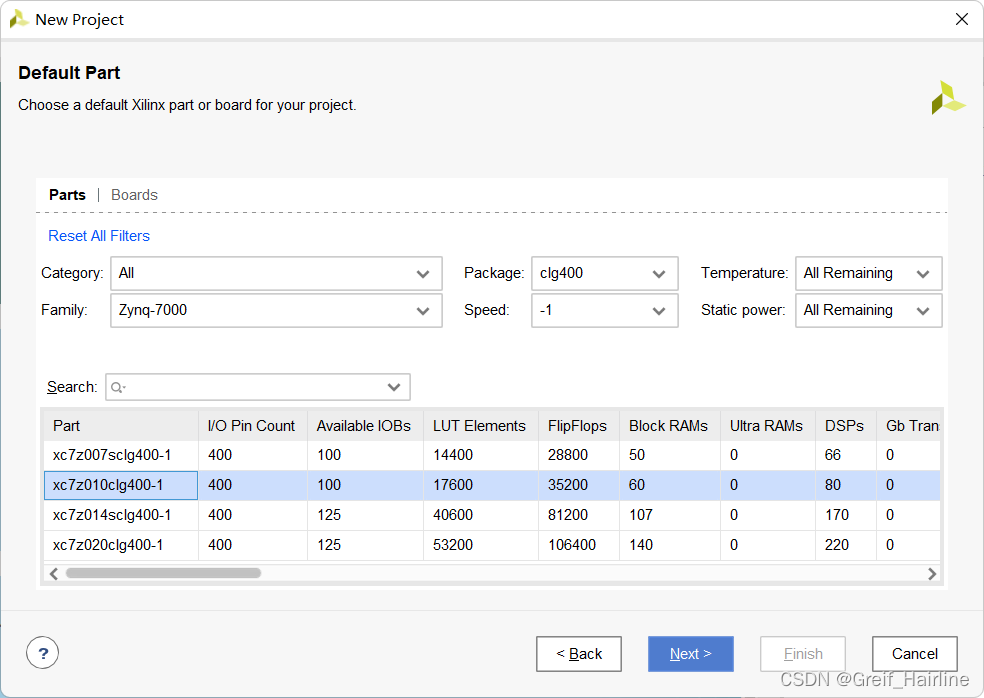

选择芯片型号,也是新建工程最重要的一步。有很多人性化的筛选操作,可以提高选择效率。

以我的开发板为例:

家族一栏选择Zynq-7000,速度等级-1,封装格式clg400

检查Summary,完成新建工程。

2.添加verilog设计文件

新建工程完的界面是这个样子的

点击Add Source添加设计文件,选择Add or create design sources

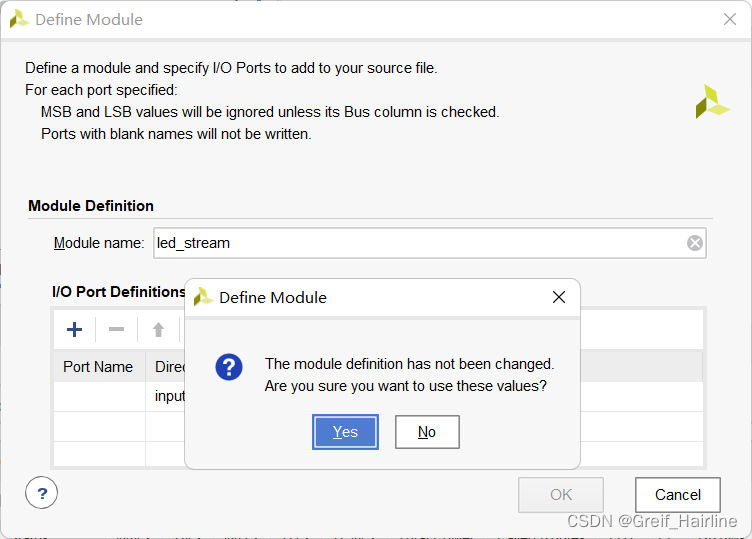

这里选择Create File,命名verilog文件名,注意以.v结尾。

Module的名字默认和.v保持一致,选择yes。

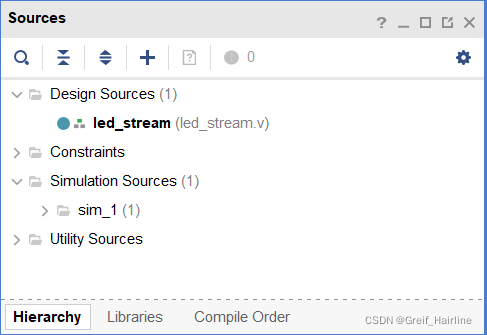

这时,我们新建的led_stream.v出现在Design Sources下,双击进行代码编写。

我们只需要在现成的模板上进行verilog代码编写即可。

这里直接贴代码:

module led_stream( output reg [3:0] led, input clk, input rst_n ); reg [25:0] cnt; reg [1:0] led_on_num; parameter CLOCK_FREQ = 50000000; parameter MAX_CNT = CLOCK_FREQ/2 - 1; always@(posedge clk or negedge rst_n) begin if(!rst_n) begin cnt <= 31'd0; led_on_num <= 2'd0; end else begin cnt <= cnt + 1'b1; if(cnt == MAX_CNT) begin cnt <= 26'd0; led_on_num <= led_on_num + 1'b1; end end end always@(led_on_num) begin case(led_on_num) 0:led <= 4'b0001; 1:led <= 4'b0010; 2:led <= 4'b0100; 3:led <= 4'b1000; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

3.综合Synthesis

点击Run Synthesis,选择动用的线程个数(根据电脑配置来,一般选最大,我这里是12),右上角显示综合的进度。

综合完成后,弹出对话框:

因为我们接下来要进行管脚约束,所以这里直接cancel。

4.管脚约束

点击Open Elaborate Design,选择ok。

Package界面十分有用,告诉我们不同bank的划分和IO分布。

下面进行最重要的管脚约束:

可以看到一共有6个管脚需要我们进行约束

这里我们主要进行引脚约束和电平标准约束

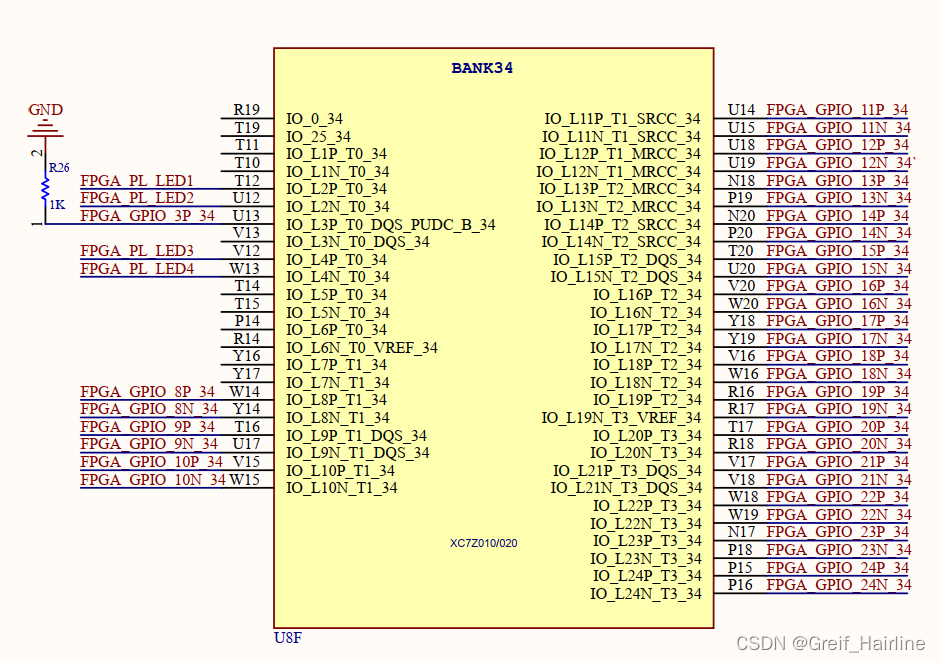

对于四个PL端的LED来说,首先根据硬件原理图找到对应bank的供电电平,即为这几个IO的标准电平。

可以看到四个LED都在bank34上面

找到bank34发现其为3.3v供电,所以四个led的电平标准都为LVCMOS33

同理进行复位和时钟引脚约束。

完成引脚约束如下图:

保存引脚约束XDC文件:

5.实现并生成比特流

这个过程需要一定时间,取绝于工程的逻辑复杂程度和电脑配置。

比特流生成后,弹出对话框,我们直接进行板级下载:

6.下载比特流文件

点击Open target,Auto Connect。

我们选择PL部分xc7z010

开发板观察到流水灯效果:

【结语】

实际的开发流程远不止如此,比如说时序约束、时序仿真、逻辑仿真、板级调试等等,这里只是列举最重要的几个步骤。