- 1C和C++相互调用 error LNK2001: unresolved external symbol_c++unresolved什么意思

- 2利用低代码从0到1开发一款小程序_小程序低代码

- 3Claude 2 解读 ChatGPT 4 的技术秘密:细节:参数数量、架构、基础设施、训练数据集、成本_gpt-4的层数和训练参数

- 4使用org.apache.commons.io.FileUtils,IOUtils;工具类操作文件

- 5shell命令-find常用命令_shell find -exec

- 6Gradle 安装和配置教程_gradle-8.3-bin.zip放哪个位置

- 7《最长的一帧》理解01_场景渲染

- 8负载均衡_用户将请求发送给负载均衡

- 9Apriori算法中使用Hash树进行支持度计数_hash树在apriori算法中的作用

- 10glance服务器上传的镜像支持,openstack-理解glance组件和镜像服务

vivado 仿真_QuestaSim/Modelsim用脚本自动化仿真Quartus II IP Core

赞

踩

一个编辑器,一个仿真debug工具,一杯茶水,一下午。正是,久坐不觉茶水凉,起身方知尿意浓。

新建一个工程文件夹,起个自己喜欢的名字。

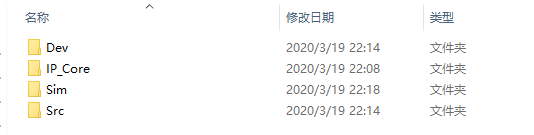

然后在里面再新建四个文件夹。

Dev 中放Quartus工程文件,

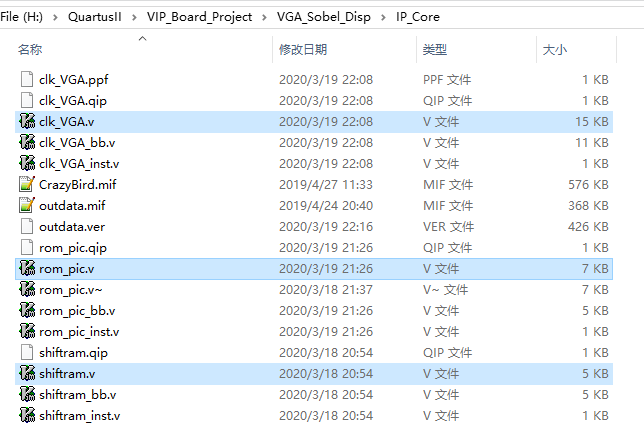

IP_Core中放在使用过程中调用的IP Core,

Sim中放Questasim/Modelsim工程和脚本、库文件、TB文件等。

Src中放.v文件

如果有文档再加个Doc,有芯片手册或资料再加个Datasheet。合理处理工程文件管理,别把所有的东西都放成一堆子。

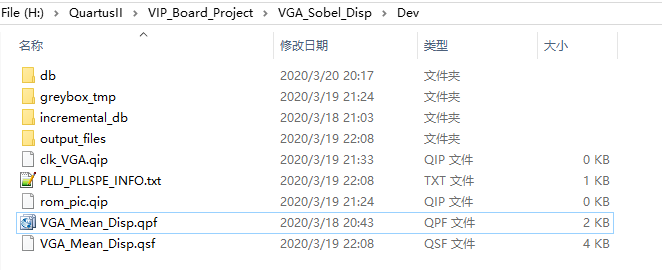

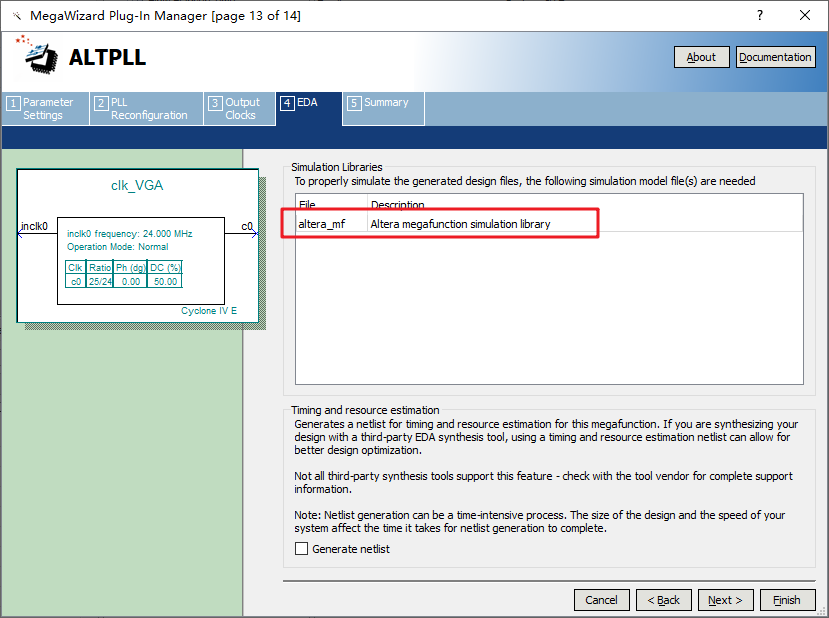

新建一个Quartus II 工程到Dev目录下。添加写好的代码和生成的需要用到的IP,我这里用到了pll、shift_ram、rom三个IP。一般IP用到的库文件会在IP生成的界面内。

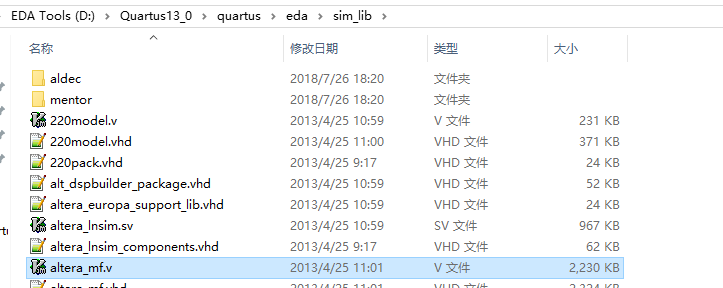

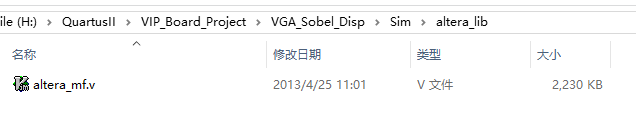

库文件在Quartus的安装目录下。

新建一个Questasim/Modelsim工程到Sim目录下。里面放下do脚本。和testbench文件。

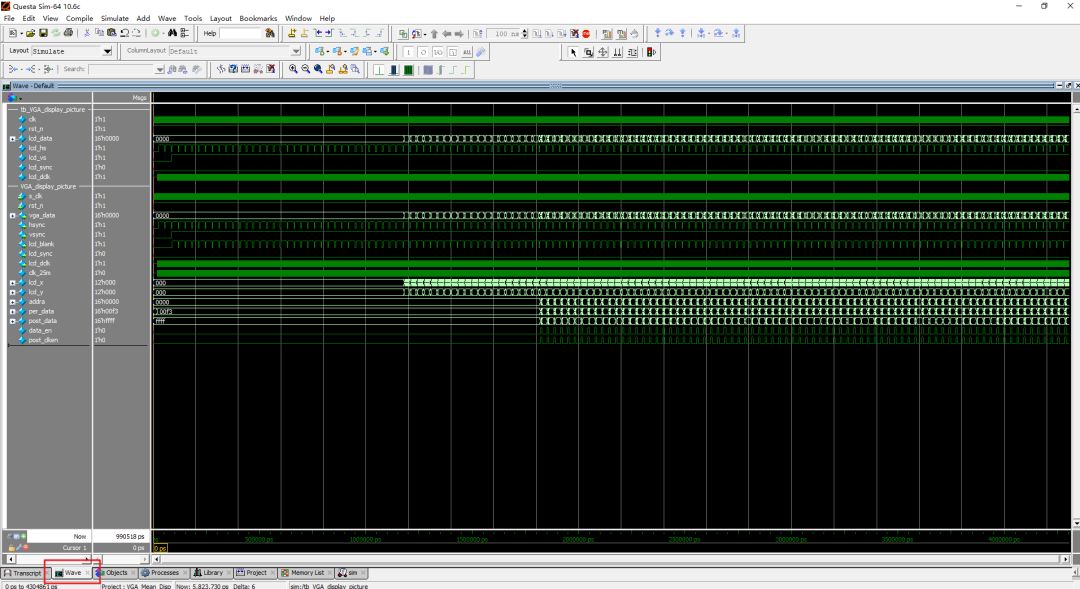

#退出当前仿真#quit -simvlib work#编译修改后的文件vlog "../Sim/altera_lib/*.v"vlog "../Src/*.v"vlog "../Sim/*.v"#开始仿真vsim -voptargs=+acc work.tb_VGA_display_picture#添加指定信号#添加顶层所有的信号# Set the window types# 打开波形窗口view waveview structure# 打开信号窗口view signals# 添加波形模板add wave -divider {tb_VGA_display_picture}add wave tb_VGA_display_picture/*add wave -divider {VGA_display_picture}add wave tb_VGA_display_picture/uut_VGA_display_picture/*# 按照上面的添加方式可以添加更多模块的波形.main clear#运行xxmsrun 10us

修改脚本中对应的工程名。

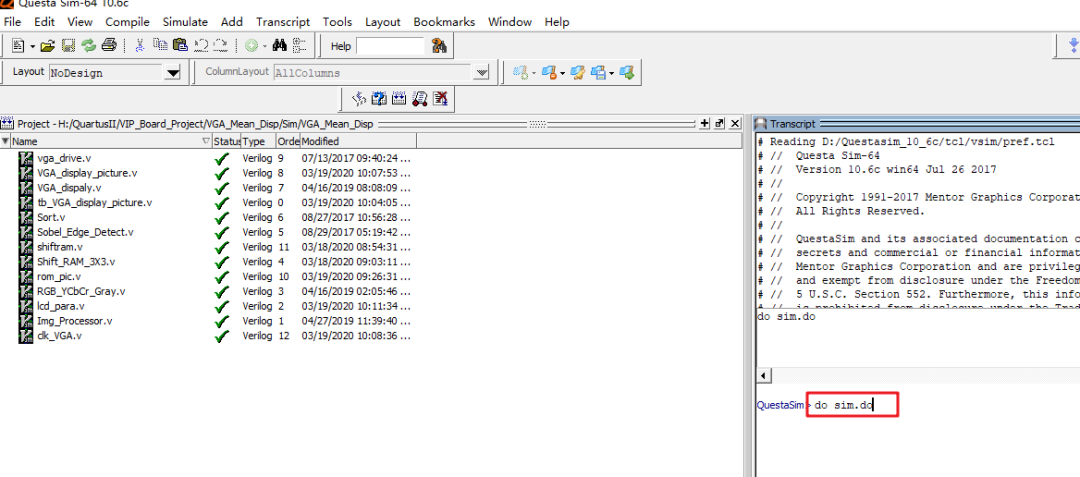

把写好的.v添加到Questasim/Modelsim工程中,IP文件需要添加对应的.v文件,仿真用到的库文件放到Sim文件夹下的altera_lib中。

用Questasim/Modelsim打开工程,打开Sim文件夹下的 .mpf文件打开工程

把所有代码都添加进来后,需要注意的是添加IP的.v文件,compile all一下,这里compile是编译一下IP的文件。然后在transcript里输入 do sim.do,点击回车,完成。

把所有代码都添加进来后,需要注意的是添加IP的.v文件,compile all一下,这里compile是编译一下IP的文件。然后在transcript里输入 do sim.do,点击回车,完成。

一次配置好后,修改RTL后,重新跑仿真,拢共需要几步?

一次配置好后,修改RTL后,重新跑仿真,拢共需要几步?

do sim.do最后

别再用鼠标点点点了,没有试过这样仿真的同学,这里提供一个工程例子方便测试。关注 硅农 微信订阅号,后台回复 脚本仿真 。 Modelsim中使用TCL脚本编写do文件实现自动化仿真 Vivado&ISE&Quartus II调用Modelsim级联仿真Vivado级联Modelsim仿真Re-launch问题