- 1深度学习中2D检测

- 2腾讯新预训练模型LP-BERT

- 3机器学习实验三:logistic回归_logistic 回归实验

- 4人工智能与数据分析:新时代的趋势和机会_数据分析和人工智能

- 5C# 集合(二) —— List/Queue类

- 6Java开发工具:IDEA 2023.3(Win&Mac)中文激活版_mac idea 激活

- 7pytest(12): 三种参数化方案_pytest 参数化

- 8matlab绘图和基础信号分析,电子科技大学信号处理实验1 - 信号的基本表示及时域分析...

- 9yolov5v7v8目标检测增加计数功能--免费源码_yolov8怎么计数一张图片中检测框

- 10UE4-UMG_ue4 umg

Quartus数字频率计verilog代码altera开发板_fpga频率计设计verilog

赞

踩

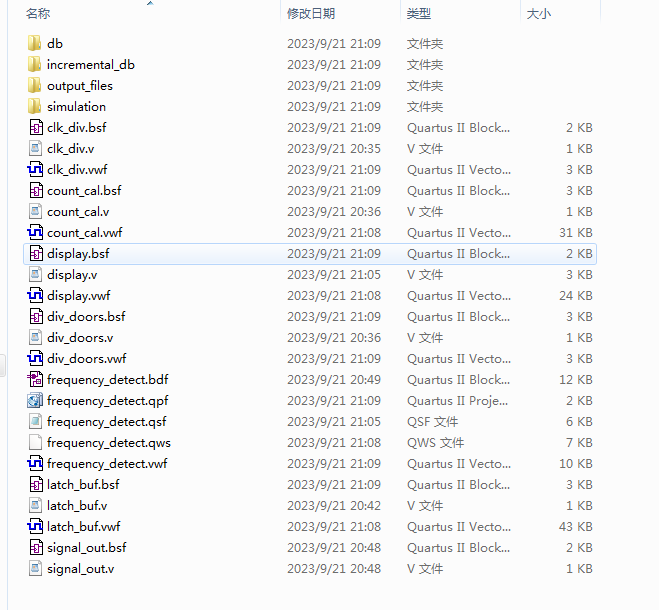

名称:Quartus数字频率计verilog代码altera开发板(文末获取)

软件:Quartus

语言:Verilog

代码功能:

1、设计一个能测量并显示信号频率的频率计。2、用数码管显示测量的频率。

3测频范围:1Hz-100MHz。误差《0.01%

4.输入信号类型:方波。

5.输入信号幅度 LVTTL电平。

6.采用等精度法在 Quartus平台下完成测频电路的设计仿真和测试。*8测量并显示信号的占空比,误差《1%

米9测量两路同频率方波输入信号的时间间隔,误差《1%

米*方波输入信号的频率为1HZ~1OMHZ

FPGA代码Verilog/VHDL代码资源下载:www.hdlcode.com

本代码已在altera开发板验证,altera开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

2. 程序文件

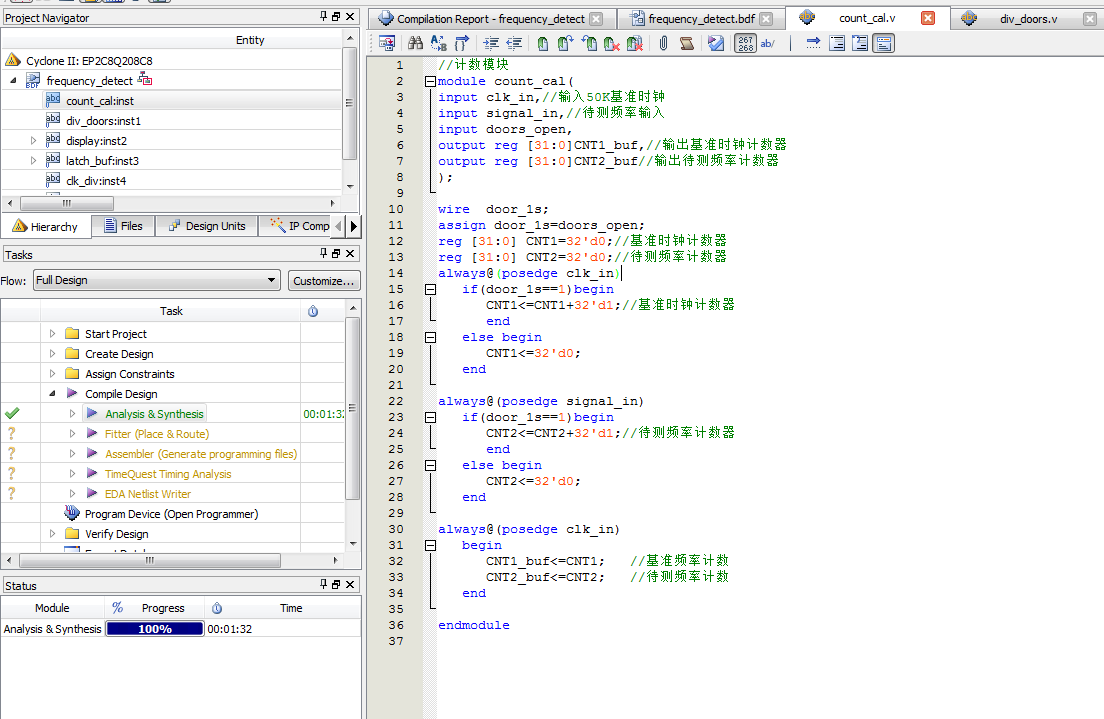

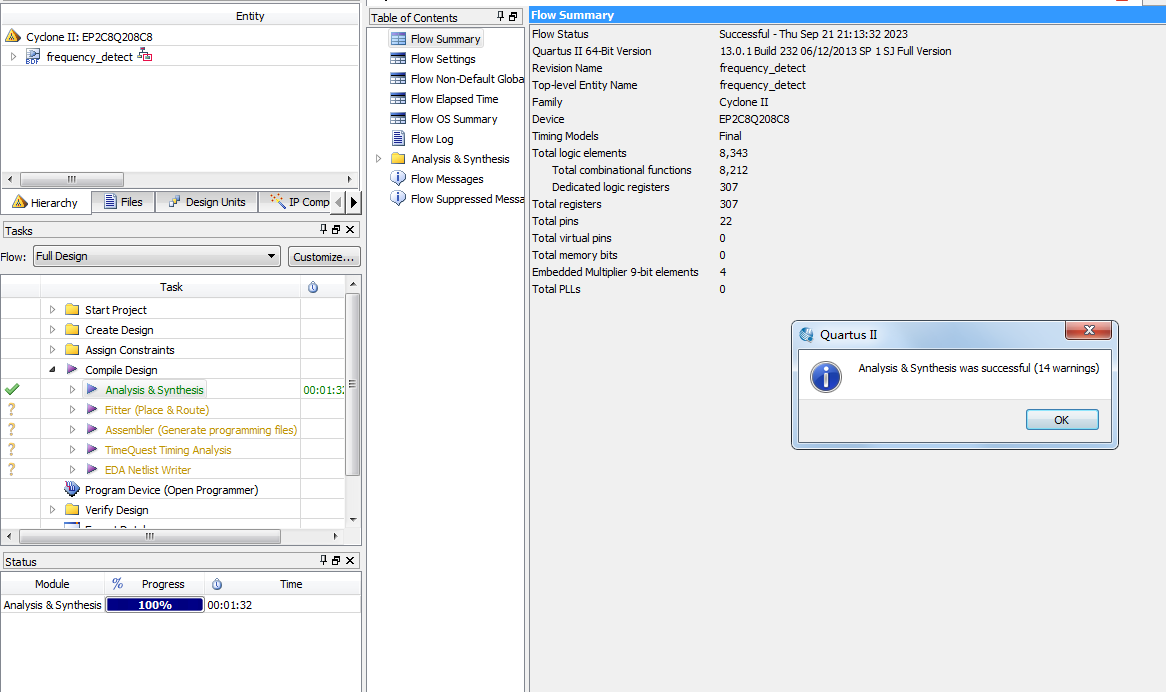

3. 程序编译

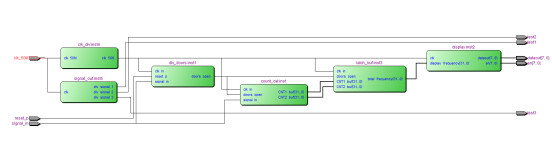

4. RTL图

管脚分配

5. 仿真图

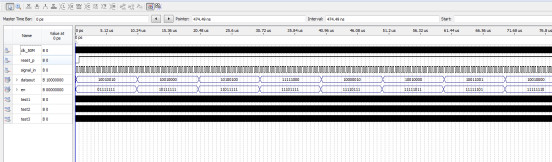

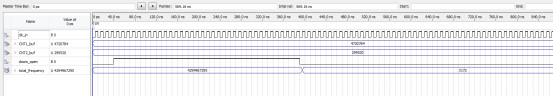

整体仿真图

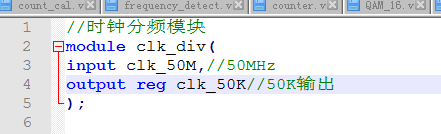

5.1 分频模块

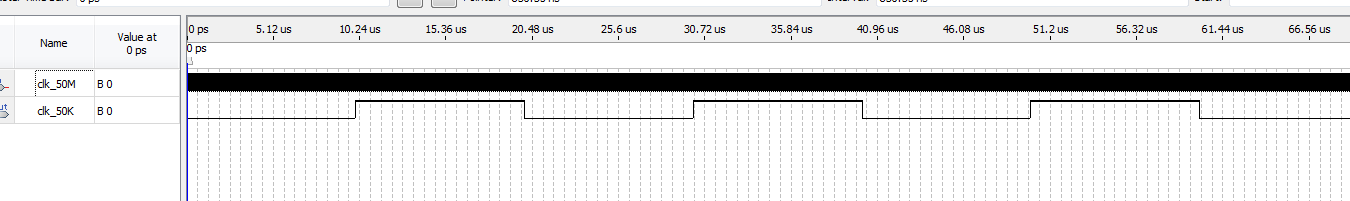

5.2 闸门信号产生模块

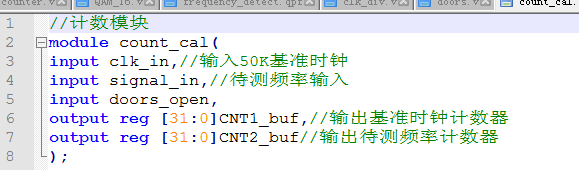

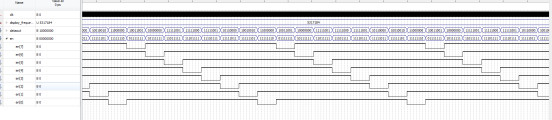

5.3 计数模块

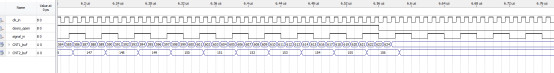

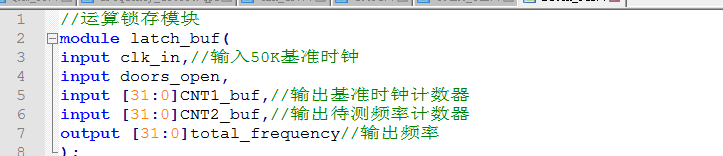

5.4 运算锁存模块

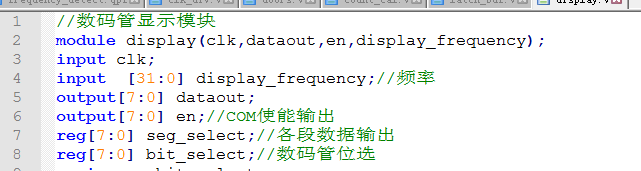

5.5 数码管显示模块

部分代码展示:

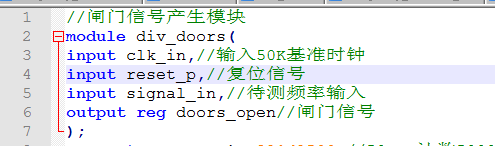

//计数模块

module count_cal(

input clk_in,//输入50K基准时钟

input signal_in,//待测频率输入

input doors_open,

output reg [31:0]CNT1_buf,//输出基准时钟计数器

output reg [31:0]CNT2_buf//输出待测频率计数器

);

wire door_1s;

assign door_1s=doors_open;

reg [31:0] CNT1=32'd0;//基准时钟计数器

reg [31:0] CNT2=32'd0;//待测频率计数器

always@(posedge clk_in)

if(door_1s==1)begin

CNT1<=CNT1+32'd1;//基准时钟计数器

end

else begin

CNT1<=32'd0;

end

always@(posedge signal_in)

if(door_1s==1)begin

CNT2<=CNT2+32'd1;//待测频率计数器

end

else begin

CNT2<=32'd0;

end

always@(posedge clk_in)

begin

CNT1_buf<=CNT1;//基准频率计数

CNT2_buf<=CNT2;//待测频率计数

end

endmodule

完整代码

扫描文章末尾的公众号二维码