热门标签

热门文章

- 1基于FPGA的音频信号的FIR滤波(Matlab+Modelsim验证)

- 2Git 基本操作命令汇总_git基本操作命令

- 3SSH远程终端神器,你在用哪一款_ssh工具

- 4Python史上最全知识重点(超详细版)进阶篇_python 进阶 笔记

- 5Flutter 开发3:创建第一个Flutter应用_android studio安装flutter

- 6ARM处理器——I.MX6ULL学习总结_i.mx6ull有srio吗

- 7《强化学习周刊》第8期:强化学习应用之自然语言处理_far-ass: fact-aware reinforced abstractive sentenc

- 8spring使用@value注解读取properties文件失败或者@value值为注解值_读取properties配置文件失败

- 915年研发经验博士手把手教学:从零开始搭建智能客服_ai智能客服设计思路

- 10FPGA学习笔记——以太网_phy与fpga连接

当前位置: article > 正文

基于FPGA的数字下变频(DDC)设计Verilog代码VIVADO仿真_fpga ddc

作者:小舞很执着 | 2024-08-16 20:15:02

赞

踩

fpga ddc

名称:基于FPGA的数字下变频(DDC)设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

数字下变频(DDC)系统在数字域里对输入信号进行下变频处理,可以降低数字信号的 速率,减小数字信号处理硬件的实现难度,是软件无线电接收机中关键的一部分,高性能的数字下变频器能够保证数字信号处理系统的稳定性,本设计在 xilinx vivado中对数字下变频的各个模块进行设计,包括DDS本振部分,混频部分,抽样部分,最后对设计的数字下变频系统进行仿真并分析其性能,

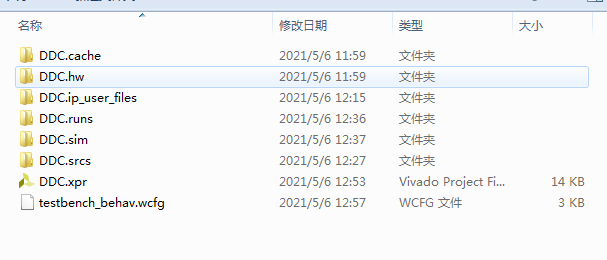

1. 工程文件

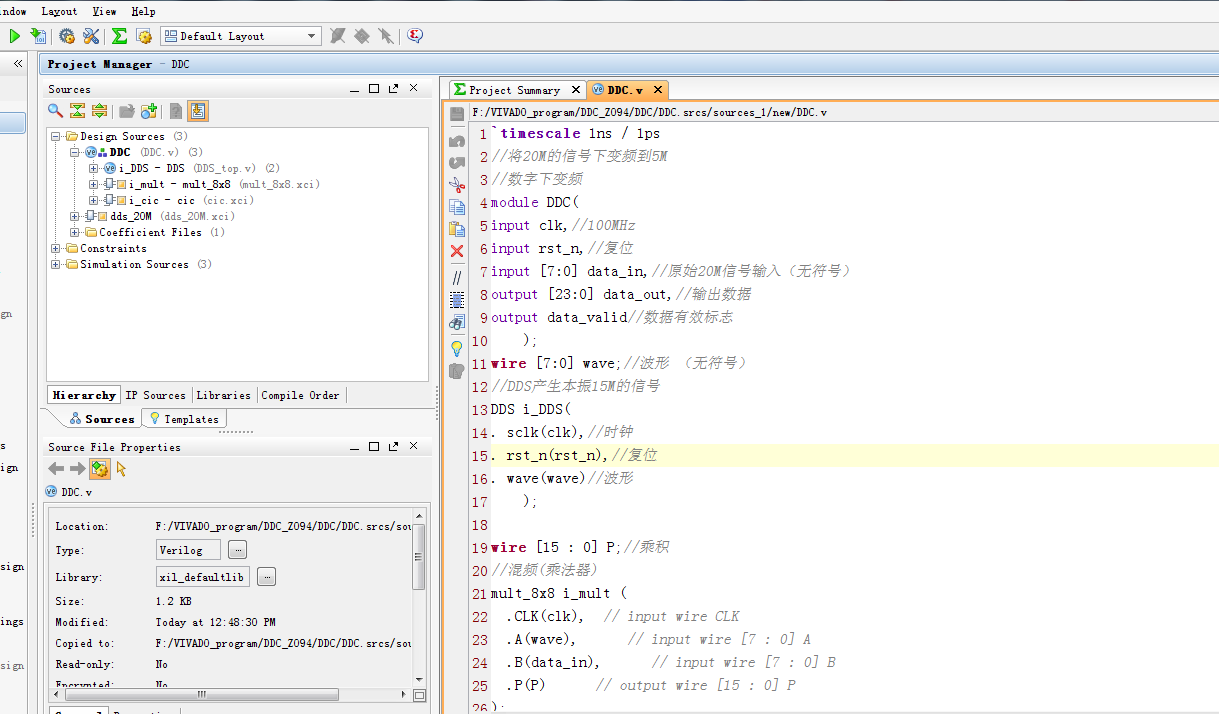

2. 程序文件

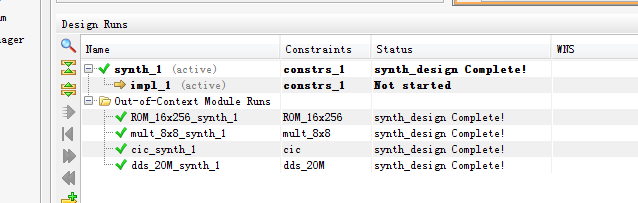

3. 程序编译

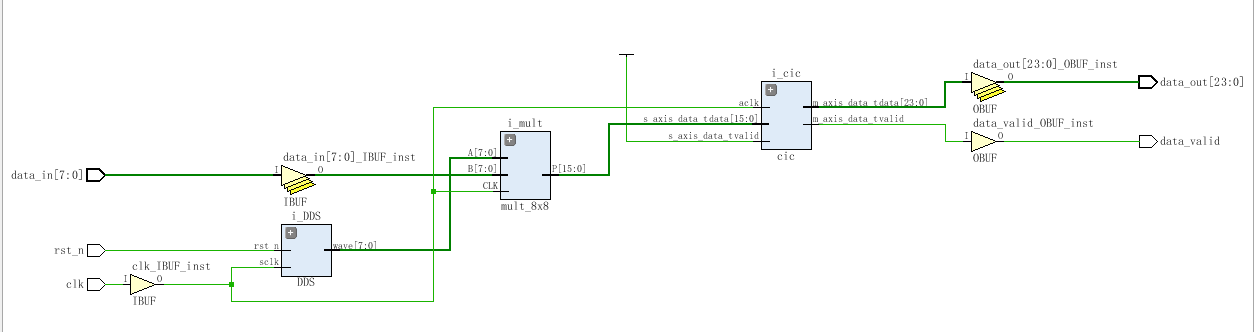

4. RTL图

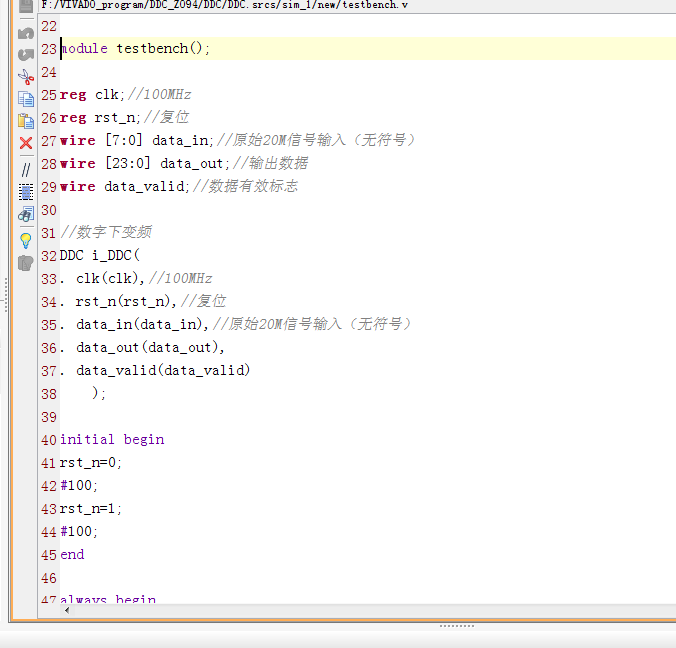

5. Testbench

6. 仿真图

部分代码展示:

`timescale 1ns / 1ps //将20M的信号下变频到5M //数字下变频 module DDC( input clk,//100MHz input rst_n,//复位 input [7:0] data_in,//原始20M信号输入(无符号) output [23:0] data_out,//输出数据 output data_valid//数据有效标志 ); wire [7:0] wave;//波形 (无符号) //DDS产生本振15M的信号 DDS i_DDS( . sclk(clk),//时钟 . rst_n(rst_n),//复位 . wave(wave)//波形 ); wire [15 : 0] P;//乘积 //混频(乘法器) mult_8x8 i_mult ( .CLK(clk), // input wire CLK .A(wave), // input wire [7 : 0] A .B(data_in), // input wire [7 : 0] B .P(P) // output wire [15 : 0] P ); wire [23 : 0] m_axis_data_tdata; wire m_axis_data_tvalid; //滤波抽样cic抽样滤波器 cic i_cic ( .aclk(clk), // input wire aclk .s_axis_data_tdata(P), // input wire [15 : 0] s_axis_data_tdata .s_axis_data_tvalid(1'b1), // input wire s_axis_data_tvalid .s_axis_data_tready(), // output wire s_axis_data_tready .m_axis_data_tdata(m_axis_data_tdata), // output wire [23 : 0] m_axis_data_tdata .m_axis_data_tvalid(m_axis_data_tvalid) // output wire m_axis_data_tvalid ); assign data_out=m_axis_data_tdata; assign data_valid=m_axis_data_tvalid; endmodule

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小舞很执着/article/detail/989663

推荐阅读

相关标签