热门标签

热门文章

- 1Git使用之(pathspec master did not match any file(s) known to git)_error: pathspec 'master' did not match any file(s)

- 22024年值得收藏的几款开源主机安全系统hids_开源hids

- 3C++ STL汇总_c++stl大全

- 4翻译们又要失业?Facebook最新无监督机器翻译成果,BLEU提升10个点!

- 5如何快速搭建自己的阿里云服务器(宝塔)并且部署springboot+vue项目(全网最全)_宝塔部署springboot项目

- 6Jupyter Notebook 常用快捷键和魔法命令

- 7selenium 浏览器驱动_selenium ubuntu浏览器驱动

- 8基于粒子群优化GRU神经网络的多输入回归分析,基于粒子群优化GRU网络多输入回归分析,基于粒子群优化GRU神经网络

- 9Android 开发面试题集合整理(内含答案),安卓资深架构师分享学习经验及总结_android面试

- 10qt自行编译第三方库_qt 编译库

当前位置: article > 正文

2021-03-25System Verilog 常见问题_system verilog sqrt函数

作者:小舞很执着 | 2024-08-06 17:54:58

赞

踩

system verilog sqrt函数

文章目录

- System Verilog 常见问题

- 1 什么是callback?

- 2 什么是factory pattern?

- 3 解释数据类型logic、reg和wire之间的区别

- 4 clocking block的用处

- 5 使用system verilog 避免testbench与dut之间竞争冒险的方法

- 6 system verilog中有哪些覆盖率类型

- 7 virtualinterfaces的需求是什么

- 8 解释abstract classes 和 virtual methods

- 9 用来建立scoreboard的数据结构是什么

- 10 与队列(queue)相比,链表(linked-line)的优点是什么?

- 11 random 和 urandom的区别

- 12 预定义的随机方法(predefined)

- 13 package 的用途是什么

- 14 $cast的用途是什么

- 15 如何在派生类中调用父类中定义的任务

- 16 rand 和randc有什么区别

- 17 什么是$root

- 18 什么是双向约束

- 19 在constraint之前使用“solve”是什么意思

- 20 不使用randmoize方法或者rand,生成随机循环数

- 21 解释pass by ref 和pass by vlue

- 22 什么是静态变量

- 23 bit[7:0] sig_1 和 byte sig_2有什么区别

- 24 program 和module有什么区别

- 25 如何在program中实现always语句

- 26 modport的用途是什么

- 27 写一个时钟发生器而不使用always语句块

- 28 什么是前向引用(foreardreferencing),如何避免

- 29 什么是循环依赖(circuit dependency),如何避免

- 30 交叉覆盖率

- 31 如何在fork/join中kill掉一个进程

- 32 什么是立即断言和并发断言

- 33 如何随机化动态数对象

- 34 什么是randsequence,它的用途是什么

- 35 什么是bin(仓)

- 36 哪种最适合用来建模事务,stract还是class

- 37 SV是否比verilog更random stable

- 38 如何在不干扰随机数生成器状态的情况下控制约束

- 39 SV中alias有什么用

- 40 为什么需要Transaction 内部实现copy()方法,而不是直接将一个对象赋值给另外一个对象

- 41 在SV中实现stract和union有什么不同

- 42 什么是this

- 43 什么是tagged union

- 44 什么是“范围分辨率运算符”(scope resolution )

- 45 bit和logic的区别

- 46 $rose 和posedge 的区别

- 47 什么是覆盖率驱动的验证

- 48 什么是分层的验证平台

- 49 验证环境的simulation phase是什么

- 50 如何根据随机索引从queue中选择元素

- 51 什么数据结构用于在scoreboard中存储数据

- 52 什么是流操作符 ,用途是什么

- 53 什么是void function

- 54 如何确保传递的ref函数参数不被改变

- 55 initial语句块与final语句块有什么区别

- 56 如何检查句柄是否有对象

- 57 旗语(semaphores)的作用是什么

- 58 always_ff、always_comb、always_latch的用途是什么

- 59 什么是static function 和automatic function

- 60 在SV中怎么给数组赋值

- 61 SV中有哪些数组类型;

- 62 为什么要使用断言

- 63 功能覆盖率与代码覆盖率的大小怎么反应项目进度

- 64 如何在SV中指定与tiemscale无关的delay

- 65 super关键字的意义是什么

- 66 什么是静态变量

- 67 什么是public声明

- 68 local 声明

- 69 protected声明

- 70 如何在clocking block声明异步信号

- 71 介绍SV中的fork-join

- 72 什么是chandle

- 73 在SV中为function 和 task添加了哪些功能

- 74 什么是SV中的DPI

- 75 什么是封装

- 76 如何计算mailbox中的元素数量

- 77 什么是covergroup

- 78 什么是super class,abstract class 和concrete class

- 79 什么是verfication plan ,包含什么

- 80 关联数组与动态数组的区别

- 81 如何检视随机化是否成功

- 82 SV中的property是什么

- 83 什么是断言严重性系统任务,如果不指定这些任务会怎么样

- 84 在哪个事件调度区域中评估并发断言

- 85 并发断言的组成是什么

- 86 连续操作运算符

- 87 goto复制运算符

- 88 交叠运算符与非交叠运算符

- 89 interface的优点是

- 90 automatic 变量在进程中的用处是什么

- 91 unpacked array 与packed array之间的差异

- 92 如果设计工程师和验证工程师在Testbench和DUT中犯同样的错误怎么办?如何能够发现错误?

- 93 什么时候使用关联数组(Associate array)

- 94 什么是变量的Scope和lifetime

System Verilog 常见问题

1 什么是callback?

“callback(回调)”机制是一种在不更改实际代码的条件下更改验证组件行为的机制。

class abc_transactor; virtual taskpre_send(); endtask virtual taskpost_send(); endtask task xyz(); this.pre_send(); this.post_send(); endtask : xyz endclass :abc_transactor class my_abc_transactor extend abc_transactor; virtual taskpre_send(); ... //This function is implemented here endtask virtual taskpost_send(); ... //This function is implemented here endtask endclass :my_abc_transactor

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 在上面的例子中,基类abc_transactor有三个task,其中2个被声明为virtual,并且没有实现(这种task叫做回调task),另一个已实现,且调用了两个未实现的task;在基类abc_transacor的子类实现了基类未实现的task。

- 利用这种机制可以将可执行task注入到已实现的task中。

2 什么是factory pattern?

factory pattern (工厂模式),旨在解决对象的创建问题。

3 解释数据类型logic、reg和wire之间的区别

- wire:用于连接不同的元件,不储存值,被连续辅助assign和端口port驱动;

- reg:并不意味实际的寄存器,用来存储数据,可以被综合成触发器,锁存器或组合电路;

-

- logic:不能被多驱动(inout),但可以替换reg或wire;

4 clocking block的用处

- interface指定了testbench和DUT通信的信号,但没有指定任何时序规则和同步要求;

- clocking block制定了时序规则和同步要求,以确保testbench在正确的时间与DUT交互,避免竞争冒险问题;

5 使用system verilog 避免testbench与dut之间竞争冒险的方法

- module的initial语句块调度在Active region;

- program中的initial语句块调度则在reactive region;

- 在program中使用非阻塞赋值驱动设计型号,在re-NBA区域对其进行更新;

6 system verilog中有哪些覆盖率类型

- 代码覆盖率:

line coverage

path coverage

FSM coverage

toggle coverage

condition coverage - 功能覆盖率:

验证人员根据RTL代码设计意图进行定义; - 断言覆盖率:

衡量在测试过程中断言的触发情况

7 virtualinterfaces的需求是什么

- 无法在sv中的non-module实体内部实例化interface,但是需要在验证环境中的class中驱动interface;

- virtual interface 是一种数据类型(可以在class中实例化),它保存着对实际接口的句柄(着意味着class可以通过virtual interface 驱动interface);

- virtual interface提供了一个将验证平台抽象模型与构成设计的实际信号分开的机制;

- virtual interface的一大优点是,类可以在运行时(run time)动态连接到不同的物理接口。

8 解释abstract classes 和 virtual methods

- virtual class将类抽象化并提供了子类扩展的原型;

- virtual methods 为程序提供了原型;

- 如果virtual class 具有virtual methods,则必须重写所有virtual methods才能实例化子类;

9 用来建立scoreboard的数据结构是什么

== Queue(队列)==

10 与队列(queue)相比,链表(linked-line)的优点是什么?

- 队列有固定的顺序,无法插入数据;

- 链表可以轻松将数据插入位置;

-队列与链表的动图演示

11 random 和 urandom的区别

- $random系统函数每次调用会返回一个32位带符号的随机数;

- $urandom系统函数每次调用会返回一个32位无符号的随机数;

12 预定义的随机方法(predefined)

- randomize;

- pre_randomize;

- post_randomize

13 package 的用途是什么

- packages 可以包含module/class/function/task/constraints/covergroup等声明;

- 在使用时需要使用范围解析运算符(::)或inport来访问packages中的内容;

package ABC;

typedef enum {RED, GREEN,YELLOW} Color;

void function do_nothing()

endfunction

endpackage : ABC

import ABC::Color;

import ABC::*; // Import everything inside the package

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

14 $cast的用途是什么

通过$cast可以将值赋给数据类型不同的变量,特别是将基类的句柄赋值给扩展类的句柄;

static casting

i = int'(10.0-0.1); // static cast convert real to integer

- 1

== dynamic casting==

function int $cast( singular dest_var, singular source_exp );

task $cast( singular dest_var, singular source_exp );

- 1

- 2

15 如何在派生类中调用父类中定义的任务

- super.task();

16 rand 和randc有什么区别

- rand:随机所有复合数据类型的值,每个值的概率相同;有重复的可能;有放回抽签;

- randc:随机所有复合数据类型的值,每个值的概率不同;无重复的可能;无放回抽签

17 什么是$root

top-level scope,用于引用任意层次中例化的模块

$root.A; // top level instance A

$root.A.B.C; // item C within instance B within top level instance A

- 1

- 2

18 什么是双向约束

- bi-directional constraints

- 默认情况下,SV中的约束是双向的,约束求解器不遵循约束指定的顺序,会同时约束所有的变量;

19 在constraint之前使用“solve”是什么意思

- 使用solve可以对约束指定顺序;

20 不使用randmoize方法或者rand,生成随机循环数

int UniqVal[10];

foreach(UniqVal[i]) UniqVal[i]= i;

UniqVal.shuffle(); //打乱排序

- 1

- 2

- 3

21 解释pass by ref 和pass by vlue

- pass by value :参数传递,每个子例程保留该参数的本地副本,子例程中值的改变,不影响原来的值;

- pass by ref:引用传递,就像传递变量的指针一样,可以避免大量的数据复制,子例程中值的改变,会影响原来的值;

- 可以使用const ref 避免后续的赋值;

参数传递与引用传递的动图演示

22 什么是静态变量

- 静态变量由关键字static定义;

- 静态变量只初始化赋值一次;

23 bit[7:0] sig_1 和 byte sig_2有什么区别

- byte有符号;

- bit 无符号;

24 program 和module有什么区别

- program是SV种新添加的,目的是:

1. 分离testbench 和DUT ;

2. 确保testbench 和DUT没有竞争冒险;

3. 提供了执行testbench的入口点;

4. 指定了在reactive region的调度; - 区别

1. program不能包含always 语句,使用foever替换,而module可以使用always语句;

2. program不能包含UDP,modules或其他program实例,module可以;

3. program 在 re_active region执行,module在active region执行;

4. program 可以调用其他modules或program的task和function;module不能调用program中的task和function;

25 如何在program中实现always语句

使用forever语句以及fork join_any语句;

always @(posedge clk or negedge reset) begin if(!reset) begin data <= '0; end else begin data <= data_next; end end // Using forever : slightly complex but doable forever begin fork begin @ (negedge reset); data <= '0; end begin @ (posedge clk); if(!reset) data <= '0; else data <=data_next; end join_any disable fork end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

26 modport的用途是什么

modports是interface的一部分,用于指定不同模块接口所连接信号的方向;

interface my_intf;

wire x, y, z;

modport master (input x, y, output z);

modport slave (output x, y, input z);

endinterface

- 1

- 2

- 3

- 4

- 5

27 写一个时钟发生器而不使用always语句块

initial begin

clk= 0;

forever#(cycle/2) clk <= ~ clk;

end

- 1

- 2

- 3

- 4

28 什么是前向引用(foreardreferencing),如何避免

- 有时需要在类声明之前声明另一个类,以供使用;

- 使用typedef class <类名>;

typedef class C2;

class C1;

C2 C;

endclass

class C2;

C1 C;

endclass

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

29 什么是循环依赖(circuit dependency),如何避免

- 过渡指定约束求解器可能会导致循环依赖,对此没有解决方案,约束求解器会发出错误/警告。

int x,y,z;

constraint XYZ{

solve x before y;

solve y before z;

solve z before x;

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

30 交叉覆盖率

- 在多个cover point 上同时统计接收到的信息

covergroup cg;

cover_point_y : coverpoint y ;

cover_point_z : coverpoint z ;

cross_yz : cross cover_point_y,cover_point_z ;

endgroup

- 1

- 2

- 3

- 4

- 5

31 如何在fork/join中kill掉一个进程

disable fork;

32 什么是立即断言和并发断言

- 立即断言:当使用if或者==assert()==执行语句时,立即断言检查表达式是否为真;

- 并发断言:使用property,持续检查仿真过程的信号值;

interface arb_if(input bit clk);

logic [1:0] grant, request;

logic rst;

property request_2state;

@(posedge clk) disable iff (rst)

$isunknown(request) == 0; //Make sure no Z or X found

endproperty

assert_request_2state: assert property(request_2state);

endinterface

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

33 如何随机化动态数对象

- 定义变量为rand类型

- 添加约束

class ABC;

rand bit [7:0] data [];

constraint cc {

data.size inside{[1:10]}; // Constraining size

data[0] > 5; //Constraining individual entry

foreach(data[i]) // All elements

if(i > 0)

data[i]> data[i-1];

}

endclass

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

34 什么是randsequence,它的用途是什么

- randsequence:是由一个或多个式子组成,每个式子包含名称和列表。

- 列表进一步分为terminals 和non-termailals,termails是不可分割的项,non-termainals可以分解为termainals,列表以“|”分割。

randsequence( main )

main : first second done ;

first : add | dec ;

second : pop | push ;

done : { $display(“done”); };

add : { $display(“add”); } ;

dec : { $display(“dec”); } ;

pop : { $display(“pop”); } ;

push : { $display(“push”); };

endsequence

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

35 什么是bin(仓)

- bin使用名称(name)和计数(count)记录一组值(value)或者序列(transitions)的次数

- 如果bin指定一组值,则每次覆盖点与该组中的一个值匹配时,相应的计数就会增加;

- 如果bin指定序列,则每次覆盖点与序列匹配时,相应的计数就会增加;

program main; bit [0:2] y; bit [0:2] values[$]= '{3,5,6}; covergroup cg; cover_point_y : coverpoint y { option.auto_bin_max= 4 ; } endgroup cg cg_inst = new(); initial foreach(values[i]) begin y = values[i]; cg_inst.sample(); //gather coverage end endprogram

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

36 哪种最适合用来建模事务,stract还是class

- transaction为uvm中的sequence item 概念,通常需要约束随机数据,因此class更合适;

- stract仅对数据类型进行重组,而不对方法进行重组;

37 SV是否比verilog更random stable

- sv可以使用受约束的随机测试(CRT),输入有意义的激励;

38 如何在不干扰随机数生成器状态的情况下控制约束

constraint_mode();

39 SV中alias有什么用

- verilog 中 assign是单向赋值,RHS影响LHS,LHS不会影响RHS;

- SV 中 alias是双向赋值,RHS和LHS互相影响;

40 为什么需要Transaction 内部实现copy()方法,而不是直接将一个对象赋值给另外一个对象

- 对象之间的赋值,只会使其指向同一片空间,不会复制transaction。

41 在SV中实现stract和union有什么不同

- stract

initial begin typedef struct { int a; byte b; shortint c; int d; } my_struct_s; my_struct_s st = '{ 32'haaaa_aaaad, 8'hbb, 16'hcccc, 32'hdddd_dddd }; $display("str = %x %x %x %x ",st.a, st.b, st.c, st.d); end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- union

成员均引用同一内存位置,无需为每种类型创建单独的对象;

typedef union {int i; real f; } num_u;

num_u un;

un.f = 0.0; // setvalue in floating point format

- 1

- 2

- 3

42 什么是this

- 当我们使用变量名时,SV将在当前作用域中查找它,然后在父作用域中查找,直到找到该变量,this起指定作用域的作用。

class Scoping;

string oname;

function new(string oname);

this.oname = oname; // classoname = local oname

endfunction

endclass

- 1

- 2

- 3

- 4

- 5

- 6

43 什么是tagged union

- tagged union是一个带标记的隐式成员,,表示最后一个存储或者写入的union成员的名称。

- 如果从非最后写入标记的union成员中读取信息,将显示错误;

union tagged {

inti;

realr;

} data;

data data_un;

data_un = tagged i 5; //store the5 in data.i, and set it as the implicit tag.

d_out = data_un.i; //read value

d_out = data_un.r;//ERROR:memeber doesnt match the union's implicit tag

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

44 什么是“范围分辨率运算符”(scope resolution )

- extern 关键字运行在类外定义方法。

class XYZ;

extern void task SayHello();

endclass

void task XYZ :: SayHello();

$Message("Hello !!!\n");

endtask

- 1

- 2

- 3

- 4

- 5

- 6

- 7

45 bit和logic的区别

bit :2值逻辑,默认为0;

logic:4值逻辑,默认为1;

46 $rose 和posedge 的区别

- $rose返回一个布尔值;

- posedge 返回一个时间;

47 什么是覆盖率驱动的验证

- 覆盖率驱动是一种以结果为导向的功能验证方法;

- 根据测试的反馈开发随机测试,当覆盖率逐渐接近极限时,更改测试找到新方法来覆盖设计的未覆盖空间;

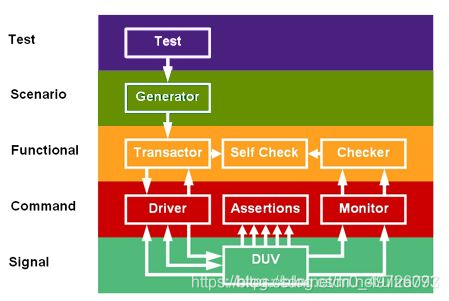

48 什么是分层的验证平台

49 验证环境的simulation phase是什么

- build_phase

- 生成配置:随机化DUT和周围环境的配置;

- 构建环境:根据配置规划和连接(connect phase) 测试平台;

- run_phase:

- 开始测试,等待完成;

- wrap_up phase:

- 报告验证结果

50 如何根据随机索引从queue中选择元素

int q[$] = {1,2,3,4};

int index[4], out;

foreach(index[i])

index[i] = i;

index.shuffle(); //orindex[i] = $urandom_range (1,4);

foreach(q[i])

out = q[index[i]];

- 1

- 2

- 3

- 4

- 5

- 6

- 7

51 什么数据结构用于在scoreboard中存储数据

mailbox 或者 queue

52 什么是流操作符 ,用途是什么

<< 和 >>

==<< ==:从右向左打包数据;

== >> ==:从左向右打包数据;

53 什么是void function

- 没有返回值的函数

54 如何确保传递的ref函数参数不被改变

- const ref

55 initial语句块与final语句块有什么区别

- initial语句块在仿真开始执行,final语句块在仿真结束执行;

- final语句块不能含有delay、wait、non-blocking具有时序的语句;

56 如何检查句柄是否有对象

-检查该对象是否已初始化,在SV中,所有未初始化的对象句柄都具有null值

- assert(obj == null);

57 旗语(semaphores)的作用是什么

58 always_ff、always_comb、always_latch的用途是什么

- always_ff:专门用于建模触发器;

always_ff @(posedge clk iff rst == 0 or posedge rst)

begin : ADDER

if (rst) begin

sum <= 0;

parity <= 0;

end

else begin

sum <= b + a;

parity <= ^(b + a);

end

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- always_comb:专门用于建模组合逻辑;

always_comb

begin

sum = b + a;

parity = ^sum;

end

- 1

- 2

- 3

- 4

- 5

- always_latch:专门用于建模锁存器;

always_latch

begin : ADDER

if (enable) begin

sum <= b + a;

parity <= ^(b + a);

end

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

59 什么是static function 和automatic function

- static 和 sutomatic 的区别在于值是否共享同一块空间,默认为静态;

60 在SV中怎么给数组赋值

int [1:2]a[1:3] = '{'{0,1,2},'{3{4}}};

- 1

61 SV中有哪些数组类型;

- packed数组;数组维度在数组名称之前;

- unpacked数组;数组维度在数组名称之后;

62 为什么要使用断言

- 检查设计的行为是否正常,用于补充功能覆盖率信息;

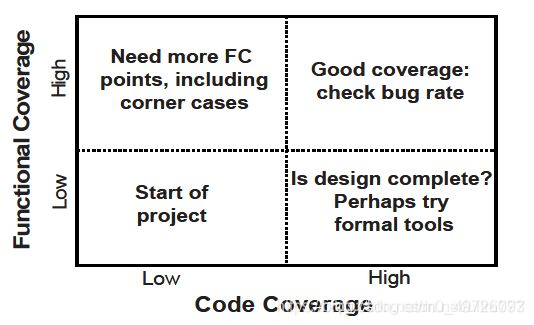

63 功能覆盖率与代码覆盖率的大小怎么反应项目进度

- code(High)、functional(High): 活差不多干完了

- code(High)、functional(Low) :需要运行更多的仿真或改进测试平台

- code(Low)、functional(High):缺少功能覆盖点

- code(Low)、functional(Low) -:需要运行更多的仿真或设计代码未完善

64 如何在SV中指定与tiemscale无关的delay

- #5ns

65 super关键字的意义是什么

- 派生类引用基类的成员

66 什么是静态变量

- 在class内部使用static声明静态变量,其他类可以访问;

67 什么是public声明

- SV的对象可以声明为public或者private;

- public声明可从该对象外部访问;

- 默认情况下是public

68 local 声明

- local声明的数据只能供自身访问;

69 protected声明

- protected 声明允许自身和他的派生类访问。

70 如何在clocking block声明异步信号

interface arb_if(input bit clk); logic [1:0] grant, request; logic rst; clocking cb @(posedge clk); // Declare cb output request; input grant; endclocking modport TEST (clocking cb, output rst);//rst is asynchronous signal modport DUT (input request, rst, outputgrant); endinterface module test(arb_if.TEST arbif); initial begin arbif.cb.request <= 0; @arbif.cb; $display("@%0t: Grant =%b", $time, arbif.cb.grant); end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

71 介绍SV中的fork-join

- fork … join:

父进程将阻塞,直到该语句块中所有进程都完成为止。 - fork … join_any:

父进程将阻塞,直到该语句块中的任何一个进程完成为止。 - fork … join_none:

父进程与该语句块中所有进程同时执行。

72 什么是chandle

- chandle是一种数据类型,用于存储DPI传递的指针。

- chandle的大小取决于机器,初始值为null;

- 用于将参数传递给任务或函数;

73 在SV中为function 和 task添加了哪些功能

- 不需要 begin end 搭配;

- function 可以具有void返回类型,task具有return;

74 什么是SV中的DPI

- DPI(direct programing interface)直接编程接口

- 用于调试C,C++,System C;

75 什么是封装

- 将数据和方法进行绑定;

76 如何计算mailbox中的元素数量

- 对mailbox的句柄使用.num函数

mailbox mbx;

mbx = new(); // Allocate mailbox

mbx.put (data); //Put data object in mailbox

mbx.get (data); // Data updated with new data from FIFO

count = mbx.num(); // To count number of elements is mailbox

- 1

- 2

- 3

- 4

- 5

77 什么是covergroup

捕获来自随机激励刺激,封装覆盖率要求

enum { red, green, blue } color;

bit [3:0] pixel;

covergroupg1 @ (posedgeclk);

coverpoint color;

coverpoint pixel;

AxC: cross color, pixel;

endgroup

- 1

- 2

- 3

- 4

- 5

- 6

- 7

78 什么是super class,abstract class 和concrete class

- Super class(父类)是子类可以共享其方法的类(base class/parent class)。

- Abstract class(抽象类)是可以扩展但不能直接实例化的类。使用virtual关键字定义的。

- Abstract class的扩展类是concrete class(具体类)。

79 什么是verfication plan ,包含什么

- 为DUT创建真实的环境以检查行为;

- 验证计划与硬件规范紧密相关,包含需要验证哪些功能的描述;

- 验证计划包含:

被测DUT的规范,功能,接口等信息;

验证功能点;

验证资源、工具、人员、时间等;

验证方法、策略;

覆盖率的要求;

验证用例,直接测试案例与随机测试案例

80 关联数组与动态数组的区别

- 关联数组:具有字符串索引功能,在编译时分配内存;

- 动态数组:在运行时分配内存,构造函数用于初始化数组的大小;

81 如何检视随机化是否成功

if (!obj.randomize())

begin

$display("Error in randomization");

$finish;

end

- 1

- 2

- 3

- 4

- 5

或者

assert (!obj.randomize())

- 1

82 SV中的property是什么

- 用来表示一系列复杂的序列

property name_of_property;

< test expression > or

< complex sequenceexpressions >

endproperty;

assert_name_of_property: assert property (name_of_property);

- 1

- 2

- 3

- 4

- 5

- 6

83 什么是断言严重性系统任务,如果不指定这些任务会怎么样

- 断言严重性系统任务指断言失败打印信息的严重级别,默认情况下指定为$error;

- 一般有

$fatal;

$error;

$warning ;

$info;

84 在哪个事件调度区域中评估并发断言

- 并发断言使用的变量埃pre-poned区域采样;

- 在observe区域中评估断言;

85 并发断言的组成是什么

- sequence

- property

- assert property

86 连续操作运算符

- [* ]

87 goto复制运算符

x [->4:7]

88 交叠运算符与非交叠运算符

- 交叠 :|=>

- 非交叠: |->

89 interface的优点是

- 接口是设计重用的理想选择;

- 党信号连接数量很大时,它jianshao信号错误连接的可能性;

- 易于在设计中添加信号;

90 automatic 变量在进程中的用处是什么

- 在program有循环时使用automatic来保存变量

program automatic test;

task wait for mem(input [31:01 addr, expect data,

output success);

while (bus. addr!== addr)

@(bus . addr);

success = (bus. data== expect data);

endtask

...

endprogram

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

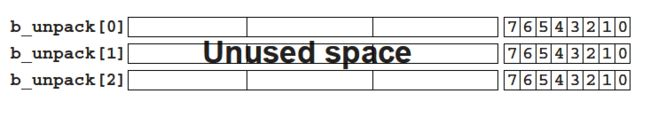

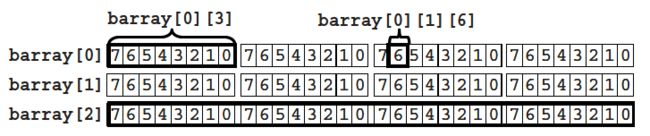

91 unpacked array 与packed array之间的差异

- unpacked array

bit [7:0]b_unpack[3]; // Unpacked

- 1

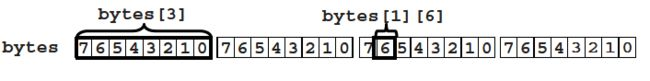

- packed array

bit [3:0] [7:0]bytes; // 4 bytes packed into 32-bits

bytes =32'hCafe Dada;

- 1

- 2

- 混合packed array和unpacked array:

bit [3:0] [7:0] barray[31]; // Packed: 3x32-bit

bit [31:0] Iw =32'h0123 4567; // Word

barray[01 = lw;

barray[0][31 =8'h01;

barray[0] [1][61 =1'h1;

- 1

- 2

- 3

- 4

- 5

92 如果设计工程师和验证工程师在Testbench和DUT中犯同样的错误怎么办?如何能够发现错误?

- 代码审查(code reviews)和协议检查器(protocol checkers)

- 在多个层次,由不同的人员进行验证(模块级和系统级)

- 客户发现(worst case)

93 什么时候使用关联数组(Associate array)

- 当集合的大小未知或数据空间稀疏时,关联数组是更好的选择。

- 关联数组在使用前不会分配任何存储,并且索引不限于整数表达式.

94 什么是变量的Scope和lifetime

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小舞很执着/article/detail/938590

推荐阅读

相关标签