热门标签

当前位置: article > 正文

基于FPGA的简易计算器设计Verilog代码Quartus仿真

作者:在线问答5 | 2024-06-27 23:55:39

赞

踩

基于fpga的简易计算器设计

名称:基于FPGA的简易计算器设计Verilog代码Quartus仿真(文末获取)

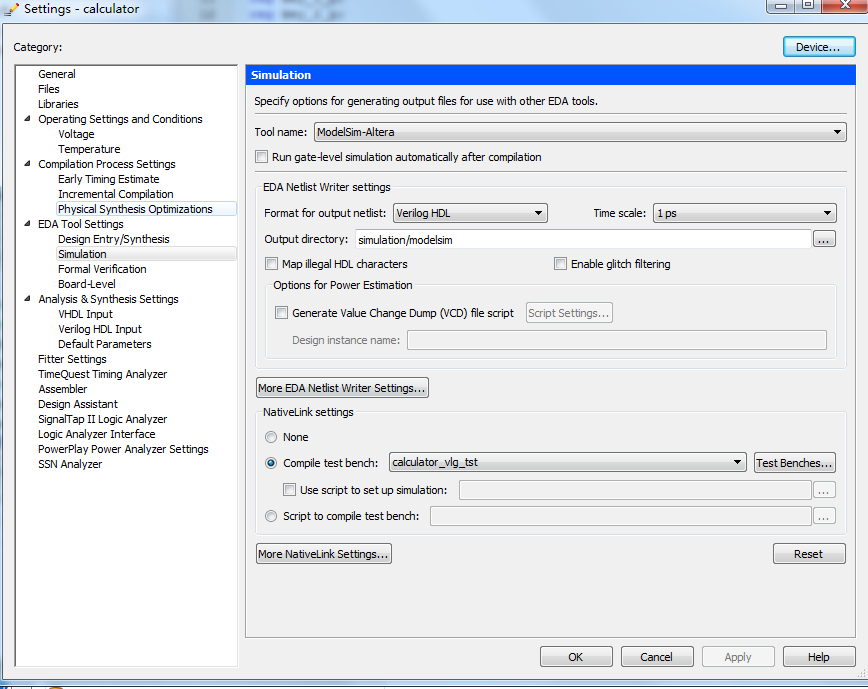

软件:Quartus

语言:Verilog

代码功能:

设计一个基于FPGA的简易计算器。

设计要求:

1.系统主要外设:矩阵键盘(4×4)、数码管6个、系统时钟(50MHz);

2.系统主要功能:可以实现十位以内的加、减、乘、除运算;用户通过矩阵键盘进行输入,并用数码管来显示当前的输入数值和最终的计算结果。

*备注:矩阵键盘大小为4×4,可以自行设计每个按键的功能

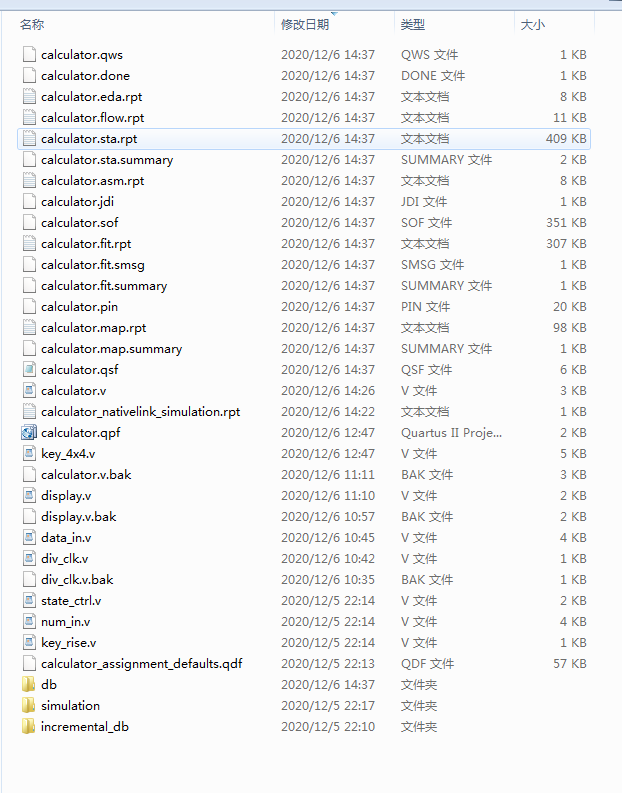

1. 工程文件

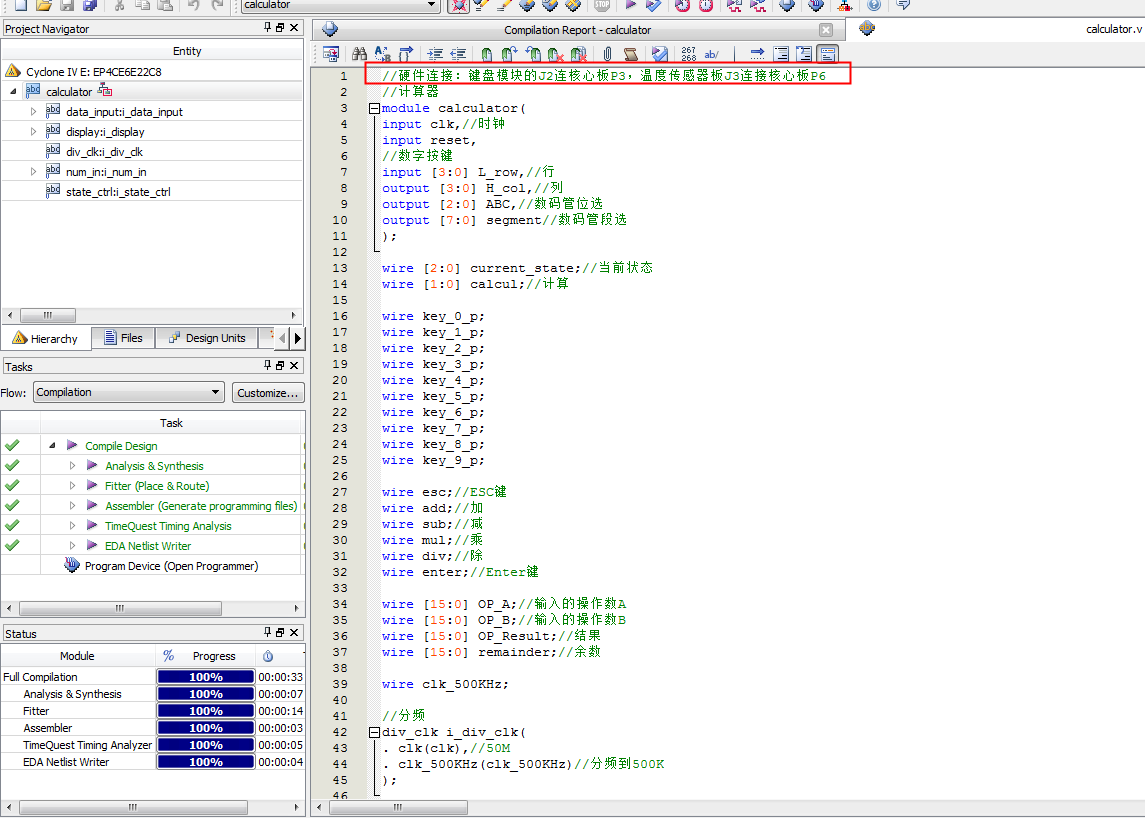

2. 程序文件

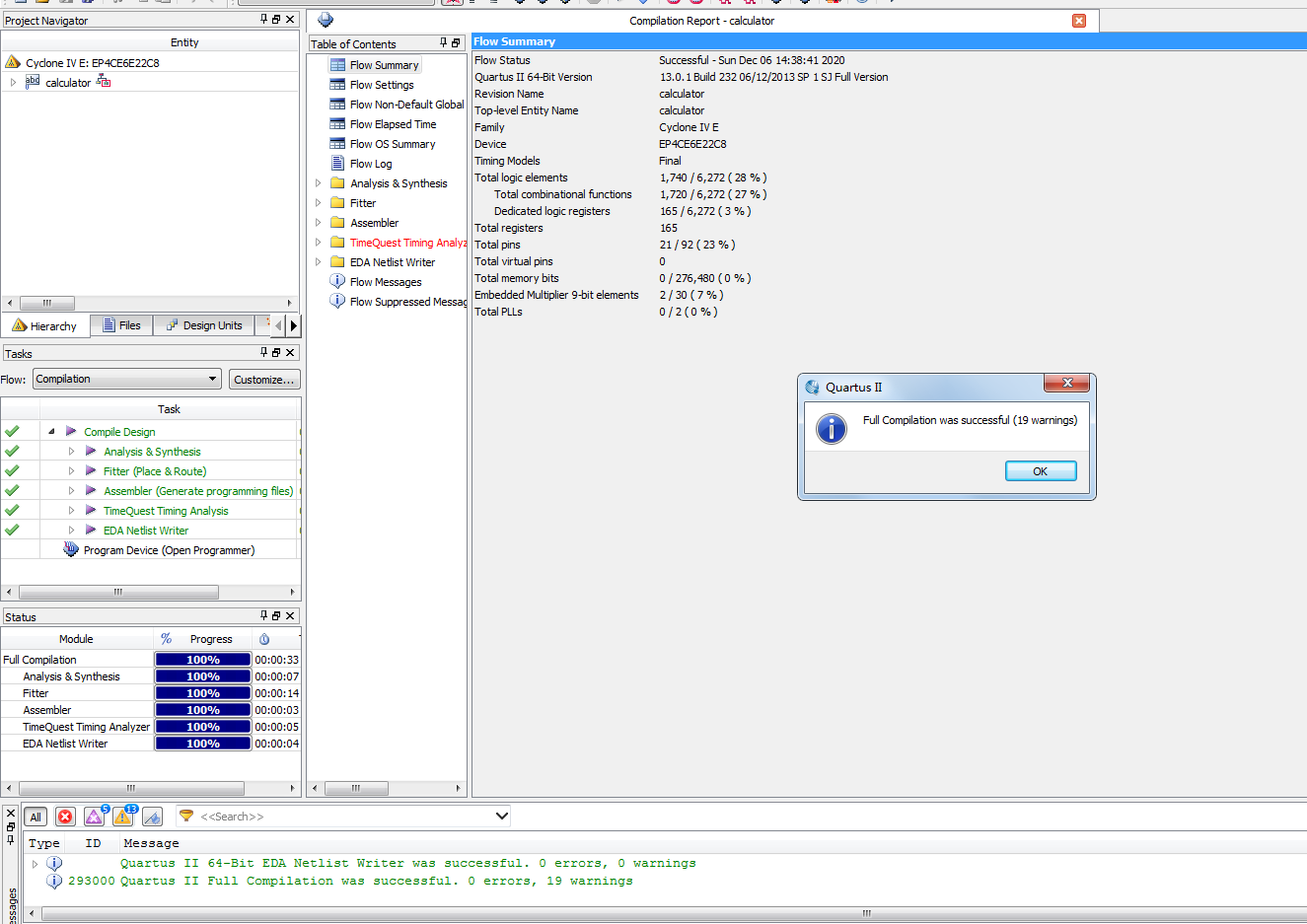

3. 程序编译

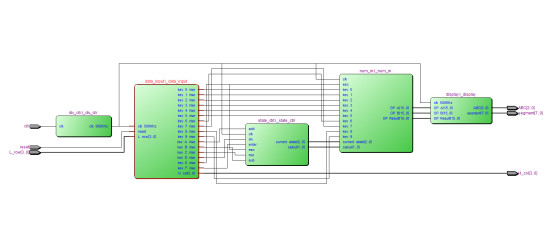

4. RTL图

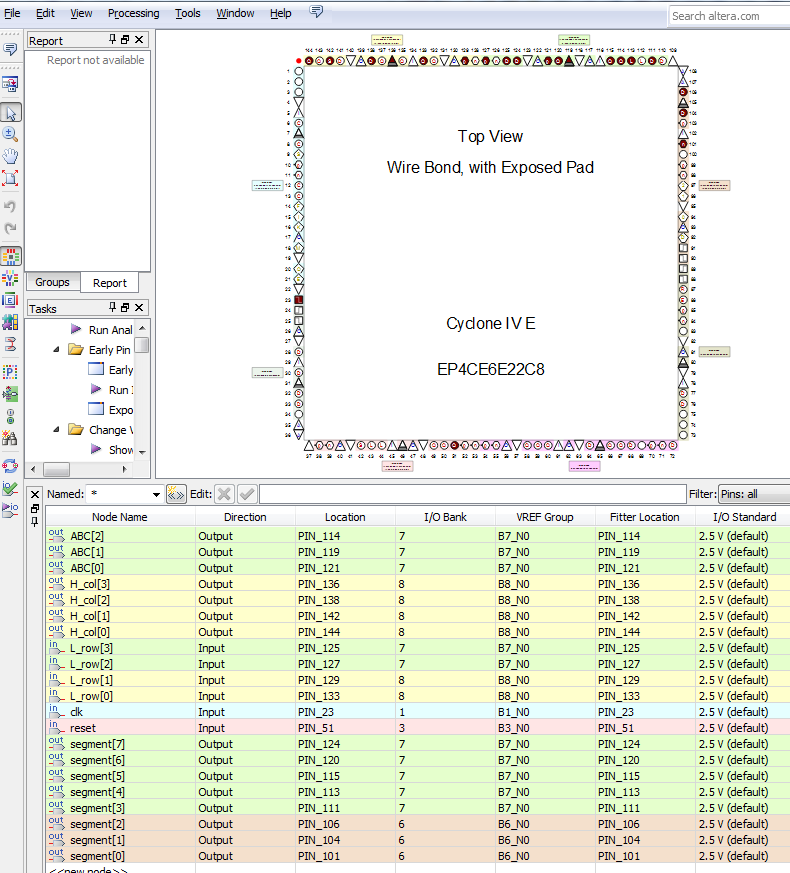

5. 管脚分配

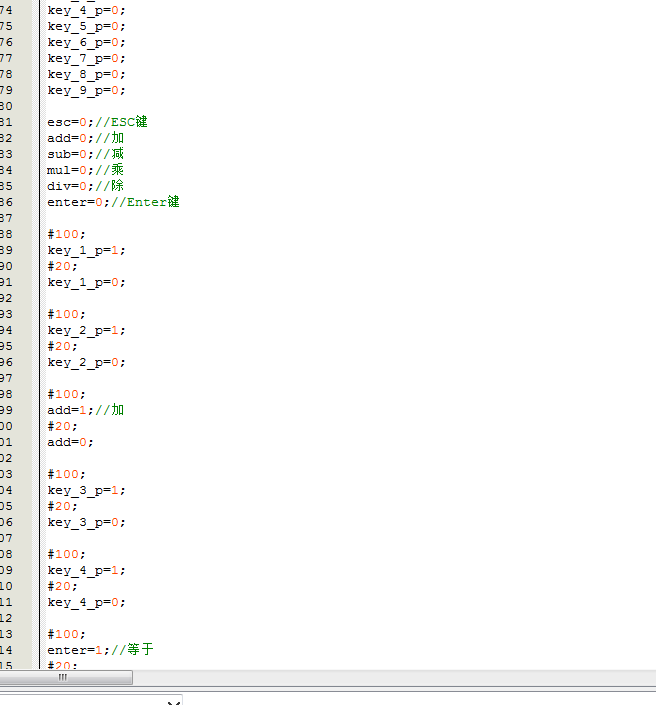

6. Testbench

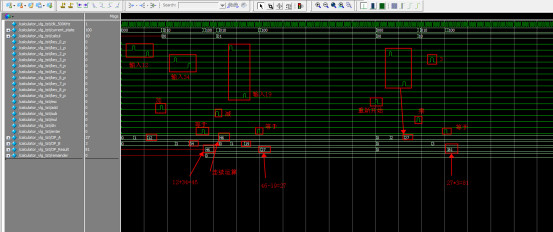

7. 仿真图

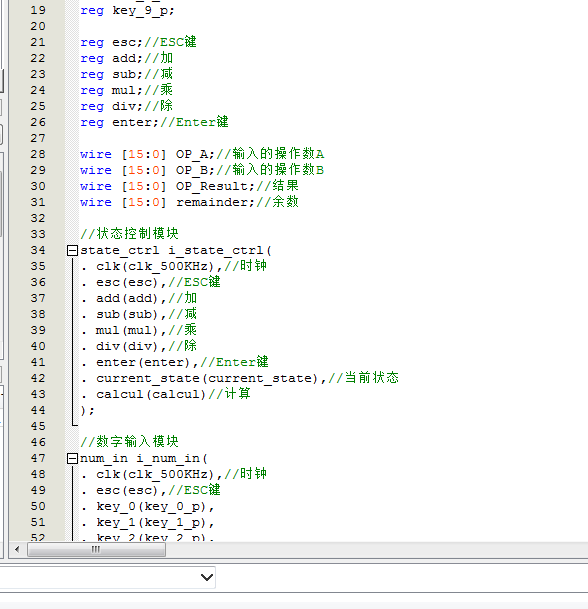

部分代码展示:

//计算器 module calculator( input clk,//时钟 input reset, //数字按键 input [3:0] L_row,//行 output [3:0] H_col,//列 output [2:0] ABC,//数码管位选 output [7:0] segment//数码管段选 ); wire [2:0] current_state;//当前状态 wire [1:0] calcul;//计算 wire key_0_p; wire key_1_p; wire key_2_p; wire key_3_p; wire key_4_p; wire key_5_p; wire key_6_p; wire key_7_p; wire key_8_p; wire key_9_p; wire esc;//ESC键 wire add;//加 wire sub;//减 wire mul;//乘 wire div;//除 wire enter;//Enter键 wire [15:0] OP_A;//输入的操作数A wire [15:0] OP_B;//输入的操作数B wire [15:0] OP_Result;//结果 wire [15:0] remainder;//余数 wire clk_500KHz; //分频 div_clk i_div_clk( . clk(clk),//50M . clk_500KHz(clk_500KHz)//分频到500K ); //输入模块 data_input i_data_input( . clk_500KHz(clk_500KHz),//500KHZ . reset(reset), . L_row(L_row),//行 . H_col(H_col),//列 . key_0_rise(key_0_p), . key_1_rise(key_1_p), . key_2_rise(key_2_p), . key_3_rise(key_3_p), . key_4_rise(key_4_p), . key_5_rise(key_5_p), . key_6_rise(key_6_p), . key_7_rise(key_7_p), . key_8_rise(key_8_p), . key_9_rise(key_9_p), . key_A_rise(add), . key_B_rise(sub), . key_C_rise(mul), . key_D_rise(div), . key_E_rise(esc), . key_F_rise(enter) ); //状态控制模块 state_ctrl i_state_ctrl( . clk(clk_500KHz),//时钟 . esc(esc),//ESC键 . add(add),//加 . sub(sub),//减 . mul(mul),//乘 . div(div),//除 . enter(enter),//Enter键 . current_state(current_state),//当前状态 . calcul(calcul)//计算 );

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/在线问答5/article/detail/764273

推荐阅读

相关标签