- 1微信小程序隐私指引完整填写范本_开发者收集你的地址,用于

- 2elasticsearch配置用户密码_es设置用户名密码

- 3github上传超过100M的大文件_github上传大于100m

- 4MYSQL 字符串操作

- 5STM32F103步进电机驱动简单控制_stm32f103控制步进电机

- 6数字IC后端真的不如前端设计和验证吗?_ptpx和redhawk

- 7Git分支——多人协作开发

- 8SpringSecurity入门、注解、配置_使用spring security启动类注解

- 9程序员常用的画图软件/可视化和小技巧_navicat生成类图

- 10自学HarmonyOS应用开发(63)- 对象关系映射数据库升级_鸿蒙开发 数据库升级

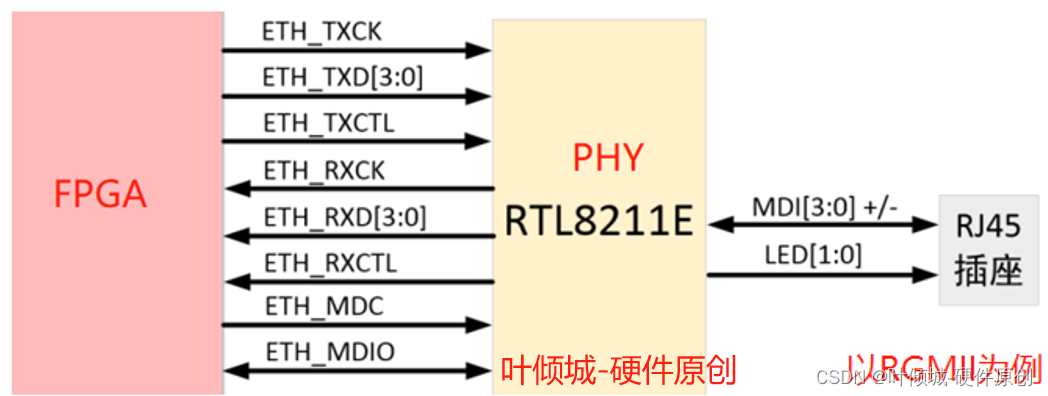

50-RGMII&SGMII&QGMII电路设计_sgmii和rgmii

赞

踩

视频链接

RGMII&SGMII&QGMII电路设计01_哔哩哔哩_bilibili

RGMII & SGMII & QSGMII电路设计

1、以太网简介(参考第2课:千兆以太网电路设计)

1.1、以太网的概述

从硬件的角度来说,以太网接口电路主要由MAC(Media Access Control:媒体访问控制)控制器和物理层接口 PHY(Physical Layer,PHY)两大部分构成。

1.2、以太网接口介绍

以太网的通信离不开物理层PHY芯片的支持,以太网MAC和PHY之间有一个接口,常用的接口有MII、RMII、GMII、RGMII等。

| 简述 | 管脚 | 速率计算 | |

| MII | MII(Medium Independent Interface,媒体独立接口):MII支持10Mbps和100Mbps的操作,数据位宽为4位,在100Mbps传输速率下,时钟频率为25Mhz。 MII接口一共有16根线。 | ||

| RMII | 在MII基础上精简的100Mbps/10Mbps接口;通过提升Clock 频率保持与MII一样的速率。 数据位宽为2位,在100Mbps传输速率下,时钟频率为 50Mhz。 | ||

| GMII | 在MII接口基础上提升了数据位宽和Clock频率,成为1000Mbps接口 GMII(Gigabit MII):GMII接口向下兼容 MII接口,支持10Mbps、100Mbps和 1000Mbps的操作,数据位宽为8位,在1000Mbps传输速率下,时钟频率为125Mhz。 | ||

| RGMII | RGMII(Reduced GMII):RGMII是GMII的简化版,数据位宽为4位,在1000Mbps传输速率下,时钟频率为125Mhz,在时钟的上下沿同时采样数据。在100Mbps和10Mbps通信速率下,为单个时钟沿采样。 | ||

| SGMII | SGMII--Serial Gigabit Media Independent Interface 串行GMII,为了达到1000Mbps,时钟频率提升 |

1.3、RGMII接口---MAC侧与PHY侧接口连接

| I/O | Pin | 描述 |

| RX | RX_D[3:0] | 接收数据 |

| RX_CLK | 接收参考时钟 | |

| RX_CTL | 接收控制信号给MAC | |

| TX | TX_D[3:0] | 发送数据 |

| TX_CLK | 发送参考时钟 | |

| TX_CTL | 从MAC发送控制信号 | |

| 其他 | ETH_RESET_N | 芯片复位信号 |

| CRS:Carrier Sense COL:Collision Detectd | 载波侦测信号 冲突检测信号 CRS和COL这两个引脚一般用在半双工的模式,一般用不着) | |

| ETH_MDC(Management Data Clock) | 数据管理时钟 | |

| ETH_MDIO(Management Data I/O) | 数据输入/输出管理 |

2、支持两个QSGMII(5Gbps 高速串行接口)(裕太微电子多口PHY)

裕太微电子推出两款自主研发的国产以太网PHY芯片

裕太微自主研发的国产四通道千兆以太网收发器

芯片YT8614H和八通道千兆以太网收发器芯片YT8618H 正式发布。

| 特点 | 性能 |

| 高度稳定 | |

| 功能丰富 | |

| 功耗更低 | |

| 成本结构更良好 |

3、千兆网之RGMII & SGMII区别 (★)

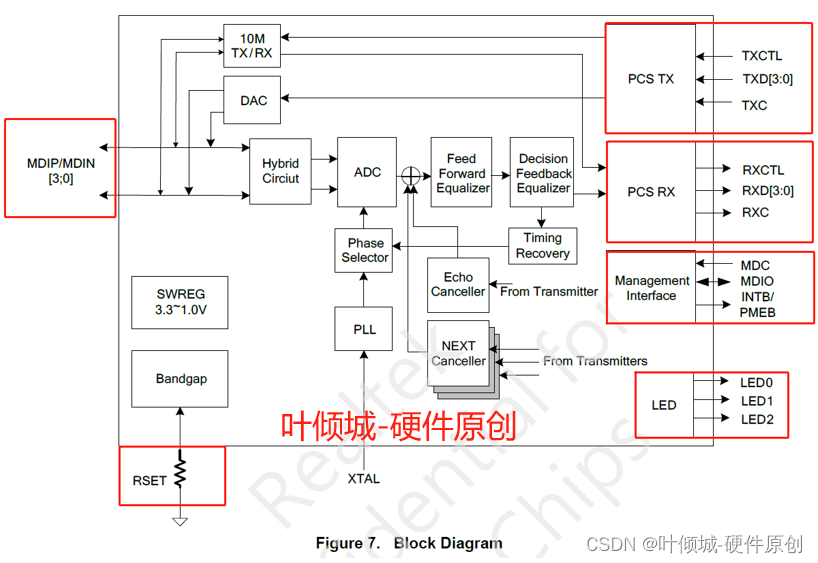

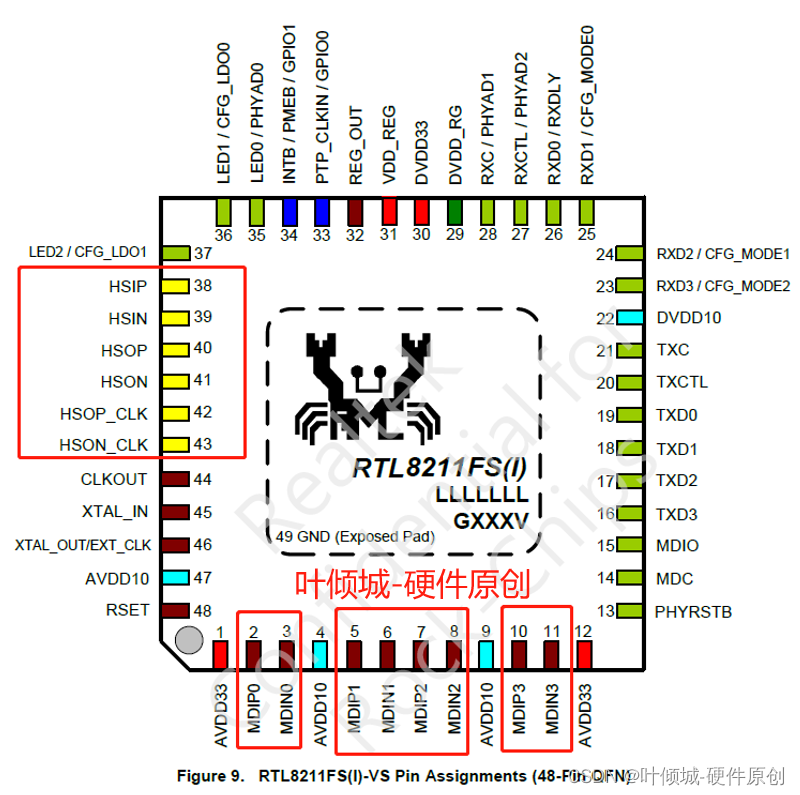

4、SGMII(以瑞昱RTL8211为例)

4.1、结构框图

4.2、信号定义

4.2.1、Power supply (★)

4.2.2、Transceiver Interface

4.2.3、clock

4.2.4、RGMII (12根线 ★)

4.2.5、Serdes(★)

4.2.6、reset

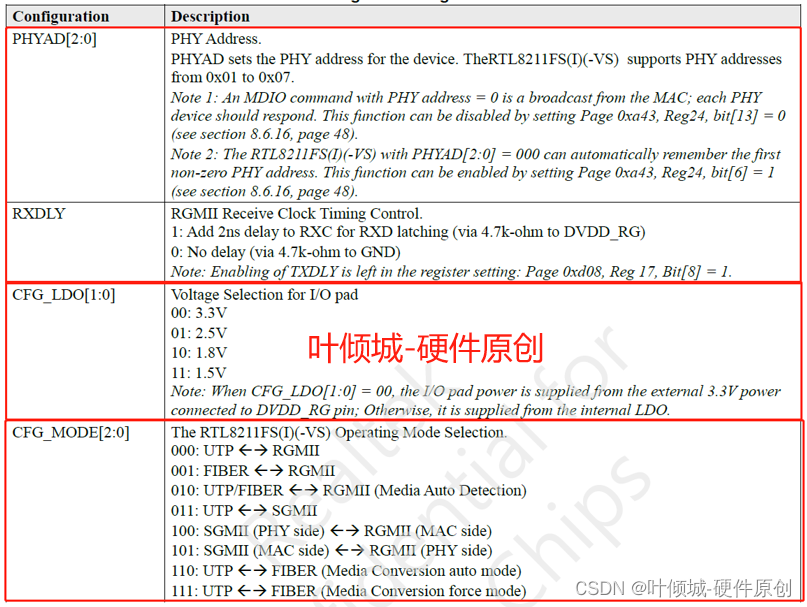

4.2.7、mode selection (hardware configuration ★)注意复用

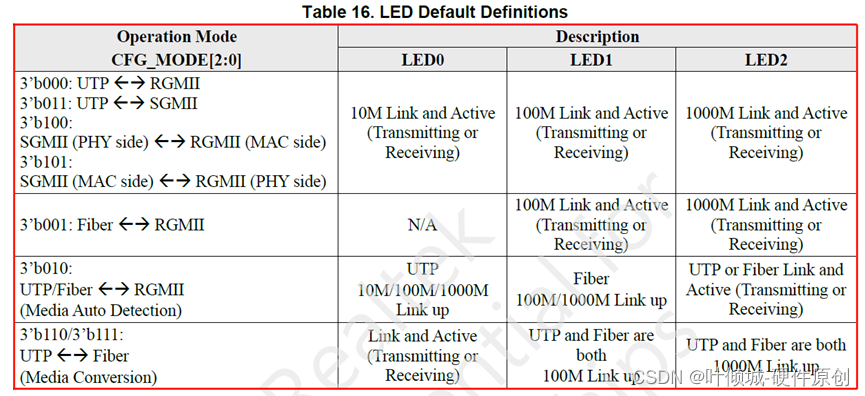

4.2.8、LED default settings(复用CFG_LDO管脚★)

4.2.9、regulator and reference

| Pin | type | description |

| RSET | O | Reference(external resistor reference) |

| REG_OUT | O | Switching regulator 1.0V output. Connect to a 2.2μH inductor |

4.2.10、management and PTP application interface

4.3、电路设计注意项(以瑞昱RTL8211为例)(★)

4.3.1、注意RGMII和SGMII电路设计的区别

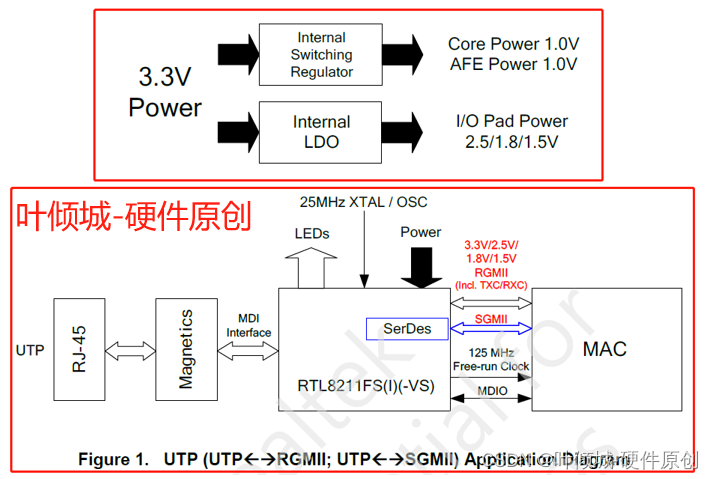

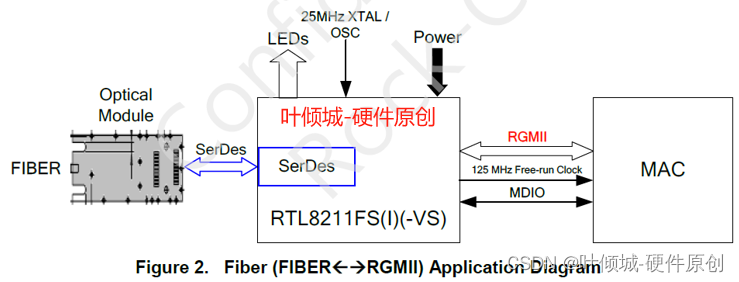

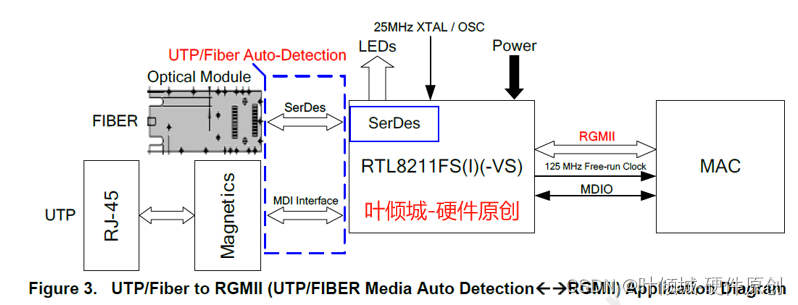

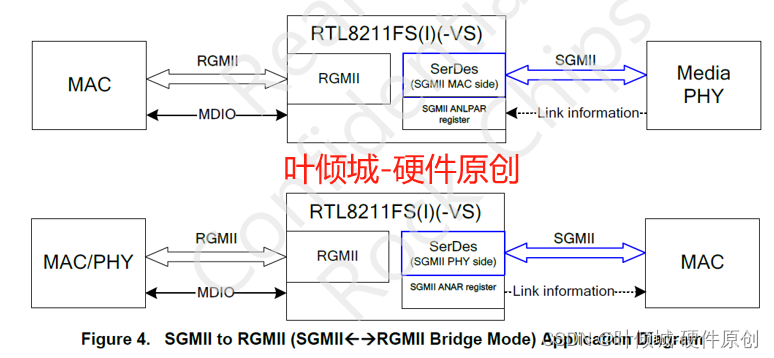

4.3.2、system applications

1、UTP Applications diagram

2、fiber Application diagram

3、UTP/fiber to RGMII Application diagram

4、SGMII to RGMII Application diagram

4.3.3、配置

4.3.4、LED配置