热门标签

热门文章

- 1FPGA:三大协议(UART、IIC、SPI)之SPI_uart spi iic verilog

- 2SpringCloud--Eureka集群

- 3如何在本地搭建和部署一个私有AI 大模型?_私有部署ai

- 4Postman Tests:简介与示例_postman没有tests

- 5Redis基本类型之Hash类型_redis hash类型

- 6ModuleNotFoundError: No module named 'sklearn.feature_extraction'; 'sklearn' is not a package_sklearn is not a package

- 7根据阿里文档编写【springAI+通义千问】出现的 “Can not find api-key” 异常_can not find api-key.

- 8源码解读 - 微软GraphRAG框架

- 9微软Edge浏览器介绍_edge浏览器简介

- 10如何安全的进行数据获取!!

当前位置: article > 正文

基础电路设计之——奇数分频器 Verilog实现_verilog分频电路不使用下降沿

作者:你好赵伟 | 2024-07-24 01:51:06

赞

踩

verilog分频电路不使用下降沿

若要实现分N频占空比非50%的奇数分频器,只需要计数到(N-1)/2时取反输出,计数到N-1时再次取反输出即可。

若要实现占空比为50%的奇数分频器,核心问题是如何处理半个周期,考虑到一个周期内clk的上升沿和下降沿正好相差半个周期,所以分别利用上升沿和下降沿得到两个占空比非50%的奇数分频器,这两个奇数分频器的上升沿、下降沿都相差半个周期,因此再将这两个占空比非50%的奇数分频器相或,就能实现占空比为50%的奇数分频器

占空比非50%奇数分频器Verilog代码

- //5分频、占空比3:2的奇数分频器

- module Riven(

- clk,

- rst,

- clko

- );

- input clk;

- input rst;

- parameter N = 5;

- output reg clko = 0;

- reg [3:0] cnt = 0;

- always @(posedge clk or negedge rst) begin

- if(!rst) begin

- //cnt <= 0;

- clko <= 0;

- end

- else if(cnt == (N-1)/2) begin

- clko <= ~clko;

- cnt <= cnt + 1;

- end

- else if(cnt == N-1) begin

- cnt <= 0;

- clko <= ~clko;

- end

- else begin

- cnt <= cnt + 1;

- end

- end

- endmodule

Modelsim输入代码,只写了关键的一部分。

- initial

- begin

- clk = 0;

- forever

- #25clk = ~clk;

- $display("Running testbench");

- end

-

- initial

- begin

- rst = 0;

- #1000;

- rst = 1;

- #1000;

- rst = 0;

- #1000;

- rst = 1;

- #1000;

- $stop;

- end

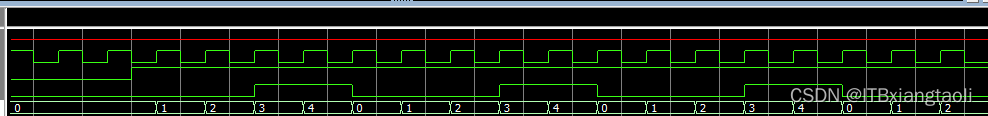

Modelsim仿真结果

占空比50%的技术分频器Verilog代码

- //5分频、占空比50%的奇数分频器

- module Fiora(

- clk,

- rst,

- clko1,

- clko2,

- clko

- );

- input clk;

- input rst;

- parameter N = 5;

- output reg clko1 = 0;

- output reg clko2 = 0;

- output reg clko = 0;

- reg [3:0] cnt1 = 0;

- reg [3:0] cnt2 = 0;

- always @(posedge clk or negedge rst) begin

- if(!rst) begin

- cnt1 <= 0;

- clko1 <= 0;

- end

- else if(cnt1 == (N-1)/2) begin

- clko1 <= 1;

- cnt1 <= cnt1 + 1;

- end

- else if(cnt1 == N-1) begin

- cnt1 <= 0;

- clko1 <= 0;

- end

- else begin

- cnt1 <= cnt1 + 1;

- end

- end

- always @(negedge clk or negedge rst) begin

- if(!rst) begin

- cnt2 <= 0;

- clko2 <= 0;

- end

- else if(cnt2 == (N-1)/2) begin

- clko2 <= 1;

- cnt2 <= cnt2 + 1;

- end

- else if(cnt2 == N-1) begin

- cnt2 <= 0;

- clko2 <= 0;

- end

- else begin

- cnt2 <= cnt2 + 1;

- end

- end

- always@(*)begin clko = clko1|clko2;end

- endmodule

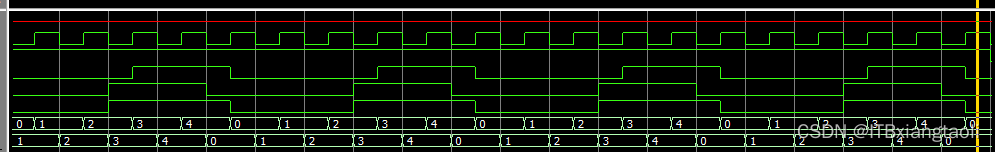

Modelsim仿真结果

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/872391

推荐阅读

相关标签