热门标签

热门文章

- 1关于事件相机的整理与思考

- 2【全开源】排队叫号系统基于FastAdmin+GatewayWorker(源码搭建/上线/运营/售后/维护更新)_开源 排队叫号

- 3springboot的web练手项目,适合新手,以及初级程序员项目实战,也适合老手进行二次开发的众多项目_springboot开发pdm

- 4什么是CDA数据分析师认证考试?

- 5黄仁勋:下一波AI的浪潮是物理AI_黄仁勋 大物理模型

- 6linux usb网卡支持_Linux中的USB标准和支持

- 7Seata(Simple Extensible Autonomous Transaction Architecture):简单可扩展自治事务架构-阿里开源分布式事务框架

- 8Python爬虫图片:从入门到精通

- 9融云 CTO 岑裕:出海技术前沿探索和排「坑」实践

- 10一文搞懂 Transformer(总体架构 & 三种注意力层)_transformer架构_transformer结构

当前位置: article > 正文

m基于FPGA的FIR低通滤波器实现和FPGA频谱分析,包含testbench和滤波器系数MATLAB计算程序_基于fpga的低通滤波器

作者:从前慢现在也慢 | 2024-08-05 15:10:42

赞

踩

基于fpga的低通滤波器

目录

1.算法仿真效果

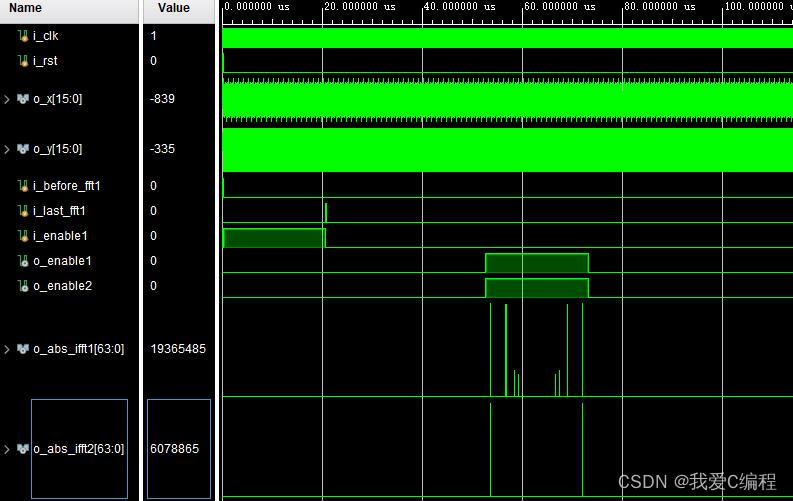

本系统进行了Vivado2019.2平台的开发,Vivado2019.2仿真结果如下:

整体仿真结果如下:

放大看,滤波效果如下:

对应的频谱如下:

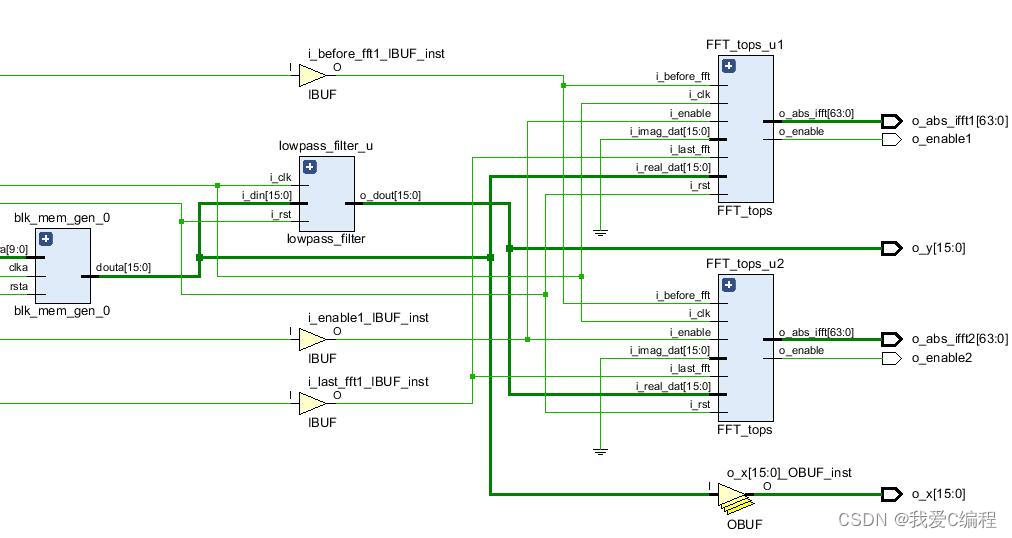

FPGA的RTL结构如下:

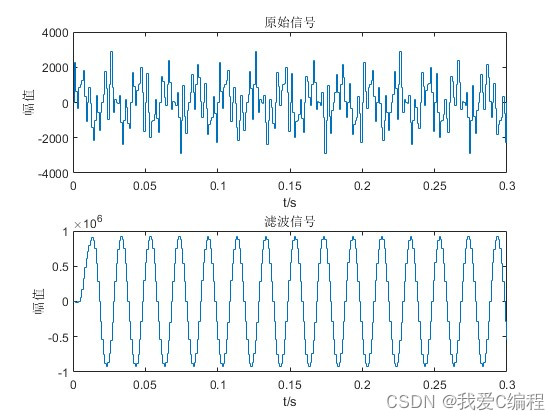

最后用matlab对比仿真,结果如下:

可以看到,FPGA的滤波效果和频谱分析与matlab的结果一致。

2.算法涉及理论知识概要

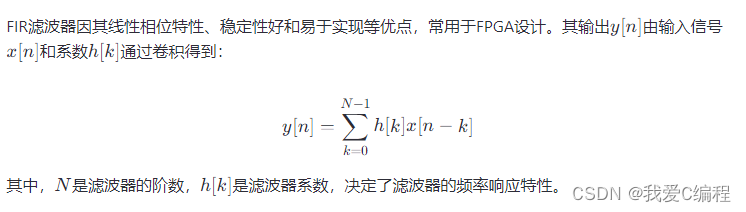

基于FPGA(Field-Programmable Gate Array,现场可编程门阵列)的数字低通滤波器实现和FPGA频谱分析是数字信号处理领域的重要应用,广泛应用于通信、音频处理、图像处理等多个行业。数字低通滤波器旨在允许低频信号通过而衰减高频信号,是信号处理中基础且重要的组件之一。其设计通常基于时域采样定理和滤波器设计理论,常见的实现方法有IIR(无限脉冲响应)滤波器和FIR(有限脉冲响应)滤波器。

在FPGA上实现FIR滤波器,主要通过配置硬件逻辑资源(如查找表LUTs、触发器等)来实现上述卷积运算。具体步骤包括:

- 系数存储:滤波器系数h[k]被存储在FPGA的块RAM中。

- 并行处理:利用FPGA的并行处理能力,将输入信号序列分块处理,每一块与滤波器系数进行并行卷积。

- 流水线设计:为了提高处理速度,设计中通常采用流水线技术,即每个运算步骤在不同的时钟周期完成,从而实现连续数据流处理。

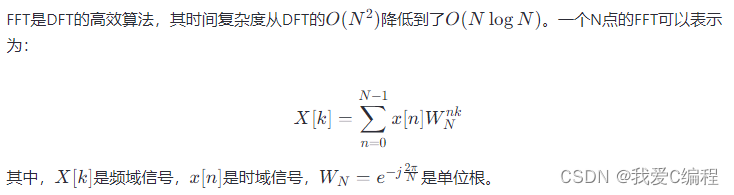

频谱分析是将信号从时域转换到频域,以观察其频率组成的技术。在FPGA上实现频谱分析,最常见的方式是使用离散傅里叶变换(DFT)或其快速版本——快速傅里叶变换(FFT)。

3.Verilog核心程序

- `timescale 1ns / 1ps

- //

- // Company:

- // Engineer:

- //

- // Create Date: 2024/05/27 21:38:45

- // Design Name:

- // Module Name: test

- // Project Name:

- // Target Devices:

- // Tool Versions:

- // Description:

- //

- // Dependencies:

- //

- // Revision:

- // Revision 0.01 - File Created

- // Additional Comments:

- //

- //

-

-

- module test();

-

- reg i_clk;

- reg i_rst;

- wire signed[15:0]o_x;

- wire signed[15:0]o_y;

- reg i_before_fft1;

- reg i_last_fft1;

- reg i_enable1;

- wire o_enable1;

- wire o_enable2;

- wire signed[63:0]o_abs_ifft1;

- wire signed[63:0]o_abs_ifft2;

-

- tops tops_U(

- .i_clk (i_clk),

- .i_rst (i_rst),

- .o_x (o_x),

- .o_y (o_y),

- .i_before_fft1 (i_before_fft1),

- .i_last_fft1 (i_last_fft1),

- .i_enable1 (i_enable1),

- .o_enable1 (o_enable1),

- .o_enable2 (o_enable2),

- .o_abs_ifft1 (o_abs_ifft1),

- .o_abs_ifft2 (o_abs_ifft2)

- );

-

- initial

- begin

- i_clk=1'b1;

- i_rst=1'b1;

- #100

- i_rst = 1'b0;

- end

- always #5 i_clk=~i_clk;

- reg [19:0]cnts2;

- always @(posedge i_clk or posedge i_rst)

- begin

- if(i_rst)

- begin

- cnts2 <= 20'd0;

- i_before_fft1<=1'b0;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

- else begin

- if(cnts2==20'd25000)

- cnts2 <= cnts2;

- else

- cnts2 <= cnts2 + 20'd1;

- if(cnts2==20'd0)

- begin

- i_before_fft1<=1'b1;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

- if(cnts2==20'd1)

- begin

- i_before_fft1<=1'b1;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

- if(cnts2==20'd2)

- begin

- i_before_fft1<=1'b1;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

- if(cnts2==20'd3)

- begin

- i_before_fft1<=1'b1;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

-

- if(cnts2==20'd4)

- begin

- i_before_fft1<=1'b0;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

- if(cnts2>=20'd5 & cnts2<=20'd4+2047)

- begin

- i_before_fft1<=1'b0;

- i_enable1 <=1'b1;

- i_last_fft1 <=1'b0;

- end

-

- if(cnts2==20'd4+2048)

- begin

- i_before_fft1<=1'b0;

- i_enable1 <=1'b1;

- i_last_fft1 <=1'b1;

- end

-

- if(cnts2>20'd4+2048)

- begin

- i_before_fft1<=1'b0;

- i_enable1 <=1'b0;

- i_last_fft1 <=1'b0;

- end

-

-

-

- end

- end

-

-

-

- endmodule

- 00_065m

4.完整算法代码文件

V

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/932924

推荐阅读

相关标签