- 1桥接生物信息学和化学信息学公开的方法数据库

- 2spark的RDD中的action(执行)和transformation(转换)两种操作中常见函数介绍_action transform

- 3内网穿透保姆级教程——内网穿透建立个人网站、远程控制_内网穿透建站

- 4源码开放:基于Pyecharts可视化分析苏州旅游攻略_python画苏州地图

- 5LeetCode比赛(持续更新…)_leetcode周赛几点开始

- 6Git常用命令超级详细_warning: ----------------- security warning ------

- 7力扣每日一题 6/4

- 8【React】React 的StrictMode作用是什么,怎么使用?

- 9Label上增加点击事件及下划线的方法

- 10火车头采集软件如何批量伪原创(火影智能AI文章伪原创)_火车头+ai打造属于你的原创内容

FPGA如何根据原理图进行约束------(基础详细教程)_引脚约束

赞

踩

目录

一、约束时钟引脚(如CLK)

首先我们需要找到晶振,时钟大多数由晶振产生。

打开原理图,晶振一般在原理图中使用大写“X”或“Y”开头。

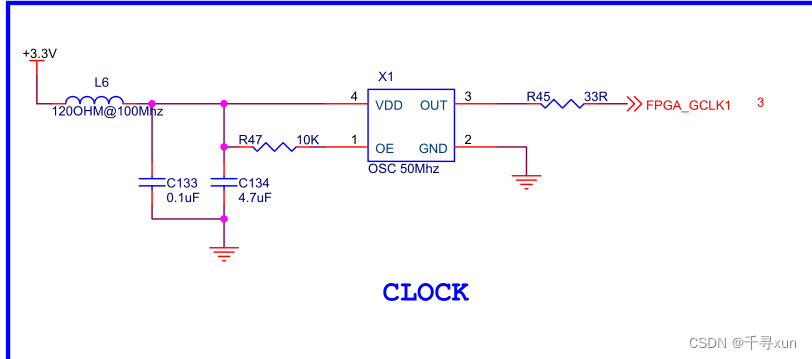

1、单端时钟

下图是一个单端时钟,时钟频率一般会在原理图中标明。(若没有在原理图中标出,可以通过直接观看晶振(板子上的实物)表面,或者使用示波器测量)

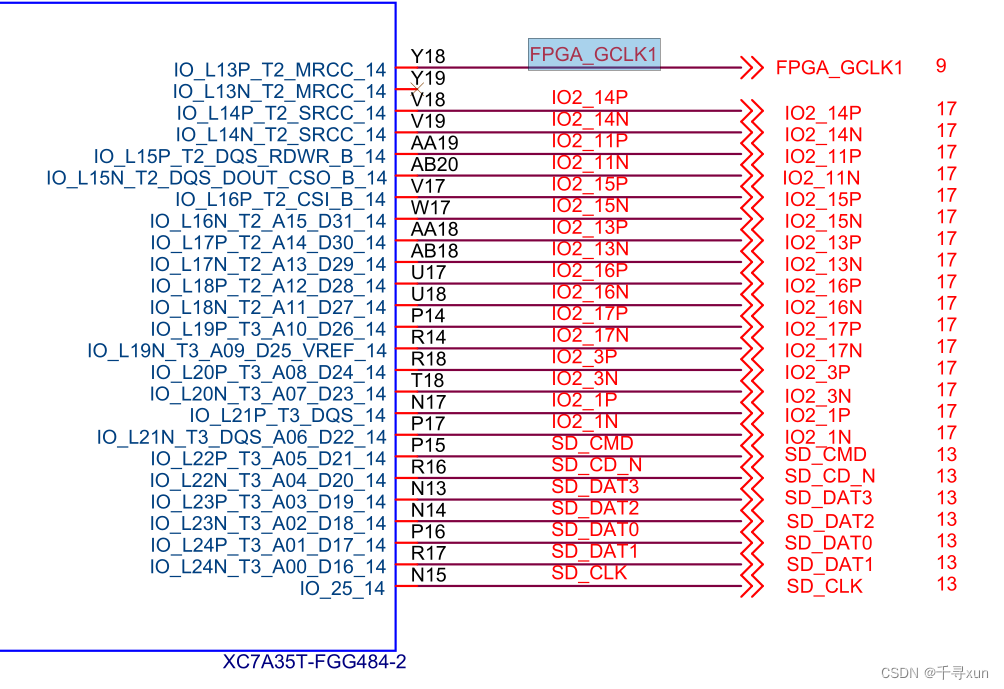

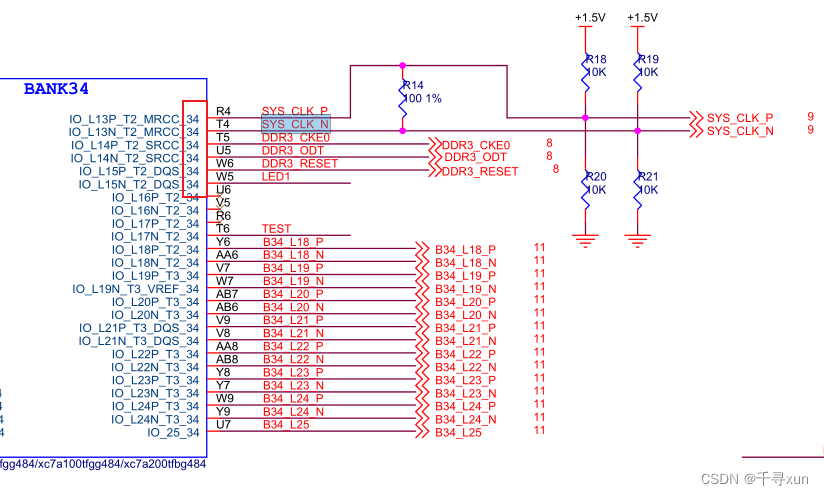

我们通过搜索找到与信号FPGA_GCLK1相连的FPGA引脚。

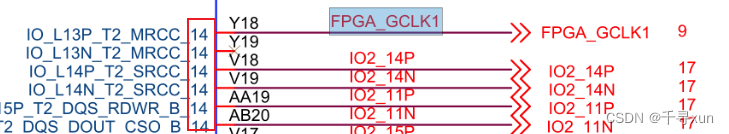

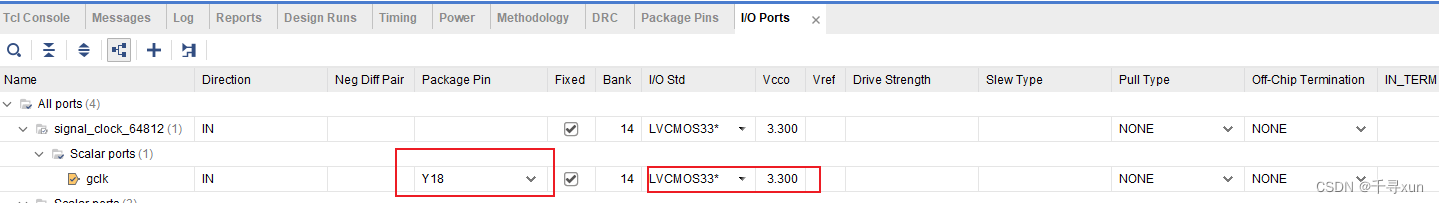

如上图所示,与时钟clk(50MHZ)相连的FPGA引脚是Y18。

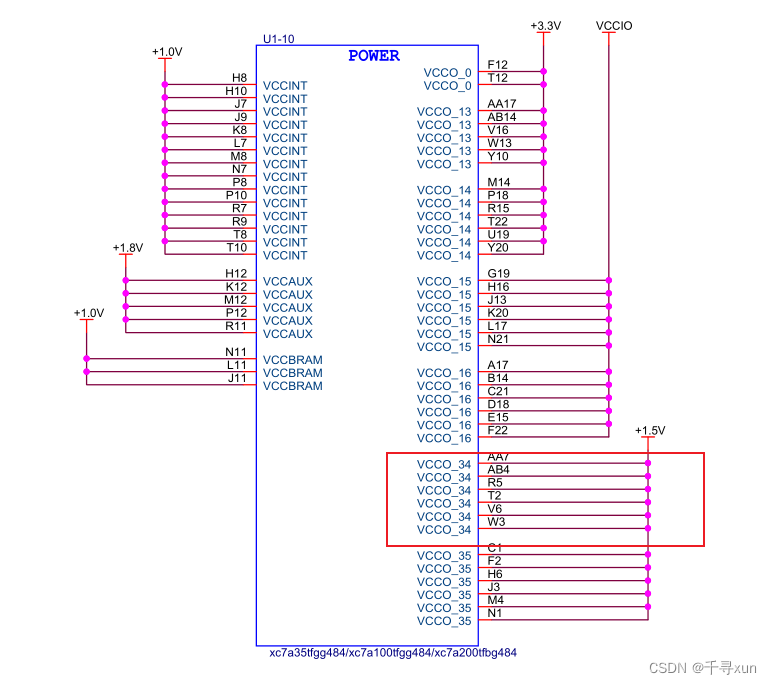

确定引脚后,还需确定引脚所在的BANK电压。

上图中Y18所在Bank是bank14

我们需要在原理图中找到bank14的电压,一般原理图都会将电源引脚和信号引脚分开画,很容易就可以找到bank电压

VCCO_14就是bank14的电压,也就是3.3V,我们就可以在约束文件中写:

- set_property PACKAGE_PIN Y18 [get_ports gclk]

-

- set_property IOSTANDARD LVCMOS33 [get_ports gclk]

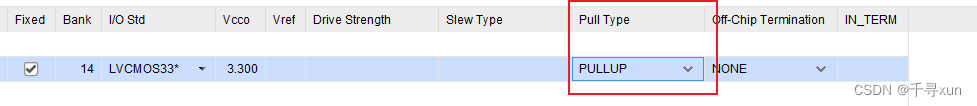

或者在引脚约束界面这样约束:

怎么进行引脚约束可以参考:

vivado进行管脚约束(详细教程)_vivado管脚约束_千寻xun的博客-CSDN博客

2、差分时钟

按照上面的方法找到引脚和bank电压

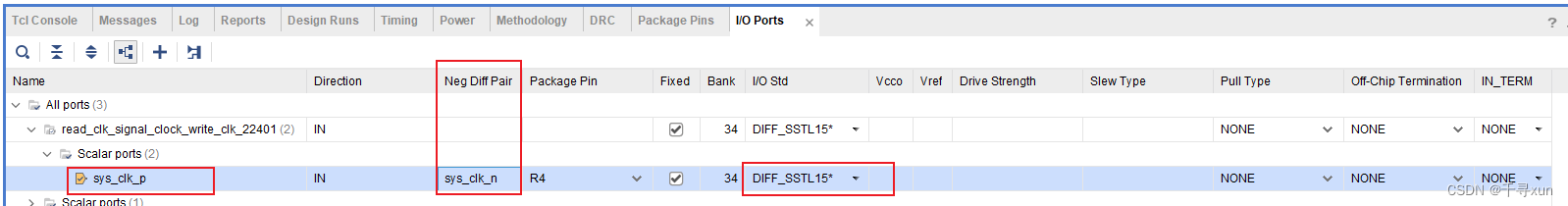

差分信号在约束时只需约束一端即可,一般是P端,也就是正端。电压这里选择差分信号,1.5v。

直接在约束文件里面加:

- set_property PACKAGE_PIN R4 [get_ports sys_clk_p]

- set_property IOSTANDARD DIFF_SSTL15 [get_ports sys_clk_p]

或者图形界面选择:

差分对软件会自动识别,直接绑定在一起,约束时只用约束一个信号。

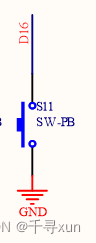

二、约束与按键相连FPGA引脚(如RST)

在原理图中找到需要使用的按键,按键与FPGA相连有几种情况

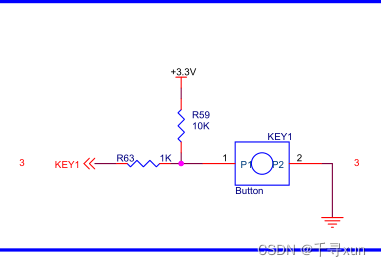

1、有上拉电阻,按下为低电平

对于这种情况,我们在约束时可以按照约束时钟信号方法约束引脚和电压。但是需要注意,按键未按下时为高电平(1),按下按键时为低电平(0)。

2、有下拉电阻,按下高低电平

对于这种情况,我们在约束时可以按照约束时钟信号方法约束引脚和电压。但是需要注意,按键未按下时为低电平(0),按下按键时为高电平(1)。

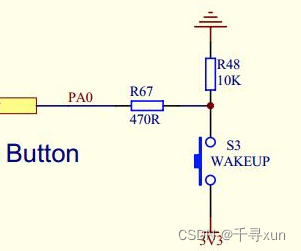

3、无上、下拉电阻,按下为高电平

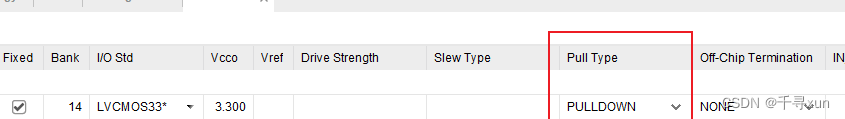

对于这种情况,我们在约束时除了按照约束时钟信号方法约束引脚和电压外,还需在FPGA内部对引脚进行下拉,上图按键按下后为高电平,所以在未按下时应让它为低电平,需要进行下拉(接低电平)。

直接加入语句

set_property PULLDOWN true [get_ports rst]或者界面约束:

在使用时是未按下时为低电平(0),按下按键时为高电平(1)。

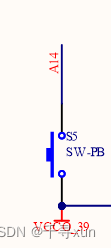

4、无上、下拉电阻,按下为低电平

这种情况与3类似,需要在FPGA内部进行上拉,按键按下后为低电平,所以在未按下时应让它为高电平,需要进行上拉(接高电平)。

直接加入代码:

set_property PULLUP true [get_ports rst]或者在界面约束: