- 1开源测试平台MeterSphere在Windows部署记录_metersphere windows

- 2如何在Python中显示图片?_python在哪里查看画出的图像

- 3android selinux_android denied for name= scontext= tcontext=

- 4如何在 PyCharm 中集成 GitLab?_pycharm gitlab

- 5混沌工程&FMEA——可用性隐患分析治理最佳拍档

- 6Electron的使用技巧_an unhandled rejection has occurred inside forge:

- 7【并发编程篇】读锁readLock()和写锁writeLock()

- 8Python WebUIAPI:打造交互式Web界面的利器_python 美化ui

- 9产品经理有效管理项目进度的5个关键方法

- 10从零搭建完整python自动化测试框架(UI自动化和接口自动化 )——持续更新_自动化框架

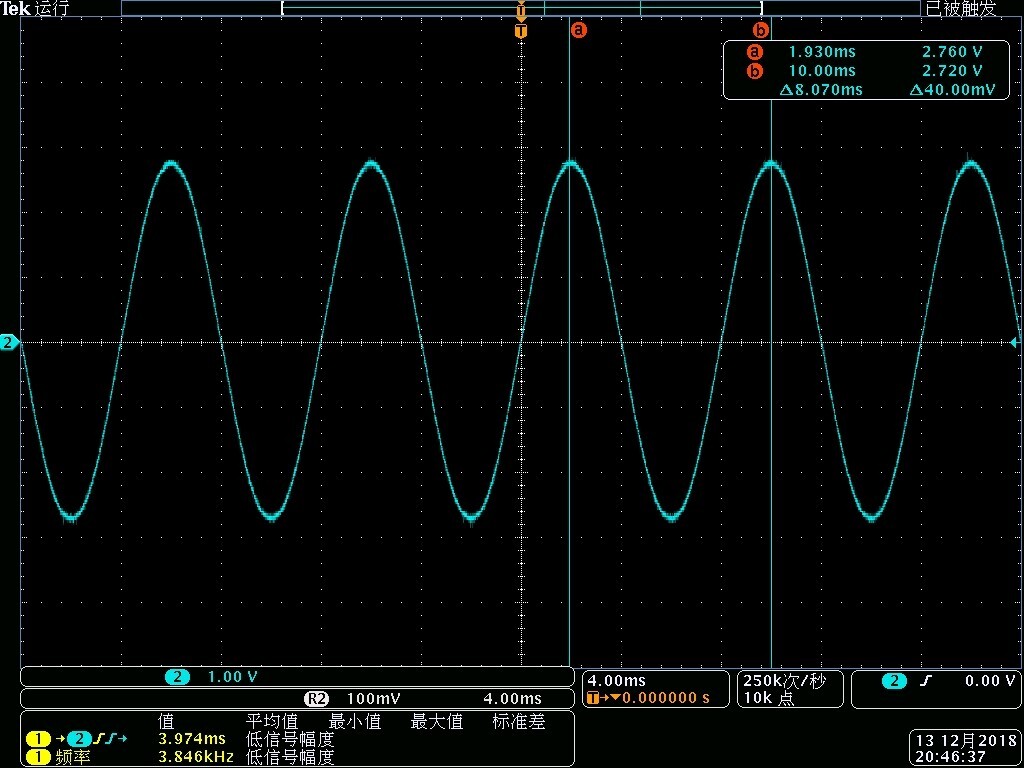

基于DDS技术的FPGA仿真信号发生器:实现多种波形的波形调节与线性组合,DDS信号发生器基于FPGA仿真,Verilog语言实现,可实现正弦波、方波、锯齿波、三角波及其线性组合的波形调节。

赞

踩

DDS信号发生器,FPGA仿真,Verilog语言。

基于DDS技术的信号发生器波形仿真,可以调节幅度和频率,能产生正弦波方波锯齿波三角波以及四种波形的线性组合。

ID:31500612766592727

卡哇伊2号小宝贝

DDS(Direct Digital Synthesis)信号发生器是一种基于数字信号处理技术的波形发生器,通过精确的数字计算和控制,生成高质量的模拟信号。它采用了FPGA(Field-Programmable Gate Array)技术进行波形仿真,通过Verilog语言编程实现。本文将从DDS信号发生器的基本原理、波形生成算法、FPGA仿真实现以及Verilog语言编程等方面展开论述。

DDS信号发生器通过数字信号处理技术将频率和幅度精确地转换为数字信号,然后通过数模转换器将其转换为模拟信号。其基本原理是利用一个N位相位累加器产生一个连续的相位序列,然后将相位序列与一个包含波形信息的查找表进行查表运算,最终生成所需的波形信号。通过改变相位累加器的步进值,可以实现波形信号的频率调节,而改变查找表中的数值,则可以实现波形信号的幅度调节。

DDS信号发生器不仅可以生成简单的正弦波、方波、锯齿波和三角波等基本波形,还可以通过线性组合的方式产生更加复杂的波形。线性组合是指将多个波形信号按照一定的比例进行叠加,从而生成新的波形。例如,可以将正弦波与方波进行线性组合,得到脉冲调制(PWM)波形,用于控制电机的转速;也可以将正弦波与锯齿波进行线性组合,得到频率可调的脉冲信号,用于数字通信系统中的时钟信号。

FPGA技术在DDS信号发生器的波形仿真中发挥了重要作用。FPGA是一种可编程逻辑器件,可以通过程序进行重新配置,实现不同的功能。通过FPGA的并行计算和高速时钟控制,可以实现高精度、高速度的波形生成和仿真。在DDS信号发生器中,FPGA通过精确的时钟控制和数据处理能力,实现了相位累加器的计数和波形查找表的输出,从而生成了高质量的模拟信号。

Verilog语言是一种硬件描述语言,被广泛应用于FPGA的设计和开发中。在DDS信号发生器的仿真实现中,Verilog语言提供了丰富的模块化和层次化设计方法,可以快速实现波形发生器的各种功能模块,如相位累加器、查找表和数模转换器等。Verilog语言的高度可定制性和灵活性,使得DDS信号发生器可以根据不同的需求进行定制化设计,满足各种应用场景的需求。

综上所述,基于DDS技术的信号发生器波形仿真是一种可以实现多种波形的高精度、高速度的波形发生器。它可以通过调节幅度和频率,生成正弦波、方波、锯齿波、三角波以及它们的线性组合。通过FPGA技术实现波形仿真,通过Verilog语言进行编程,可以灵活地实现不同的功能和需求。因此,DDS信号发生器在数字信号处理和通信技术领域有着广泛的应用前景。

相关的代码,程序地址如下:http://imgcs.cn/612766592727.html