热门标签

热门文章

- 1开发人员最常用的 10 大容器安全工具_容器安全测试工具

- 2python视频处理模块_python视频处理库:moviepy

- 3中文大语言模型 Llama-2 7B(或13B) 本地化部署 (国内云服务器、GPU单卡16GB、中文模型、WEB页面TextUI、简单入门)_llama2-13b 部署

- 4java基础(二) 自增自减与贪心规则_自增运算符前缀后缀区别在哪

- 5Transformer模型-decoder解码器,target mask目标掩码的简明介绍_为什么要在encoder前做掩码

- 6targetSdkVersion=29踩坑_targetsdk29存储jni

- 7学习笔记——Github代码仓库管理_github创建学习笔记

- 8android课程设计-单词本(Android期末作业,Android课设,AndroidStudio毕业设计)

- 9yarn保姆级安装和使用_yarn全局安装

- 10linux安装Redis详细教程

当前位置: article > 正文

Vivado+FPGA:如何使用Debug Cores(ILA)在线调试_there are no debug cores

作者:weixin_40725706 | 2024-07-25 09:07:52

赞

踩

there are no debug cores

在Vivado下在线调试是利用ILA进行的,Xilinx官方给出了一个视频,演示了如何使用Vivado的debug cores,下面我根据这个官方视频的截图的来演示一下:

官方的视频使用的软件版本为2012.2,不过在2015.3下也是差不多的。

第一步:标记需要debug的信号

例如:

VHDL:attribute mark_debug of sineSel : signal is "true";

attribute mark_debug of sine : signal is "true";

Verilog: 在需要debug的信号前加上 (* MARKDEBUG = "TRUE" *)

第二步:设置debug

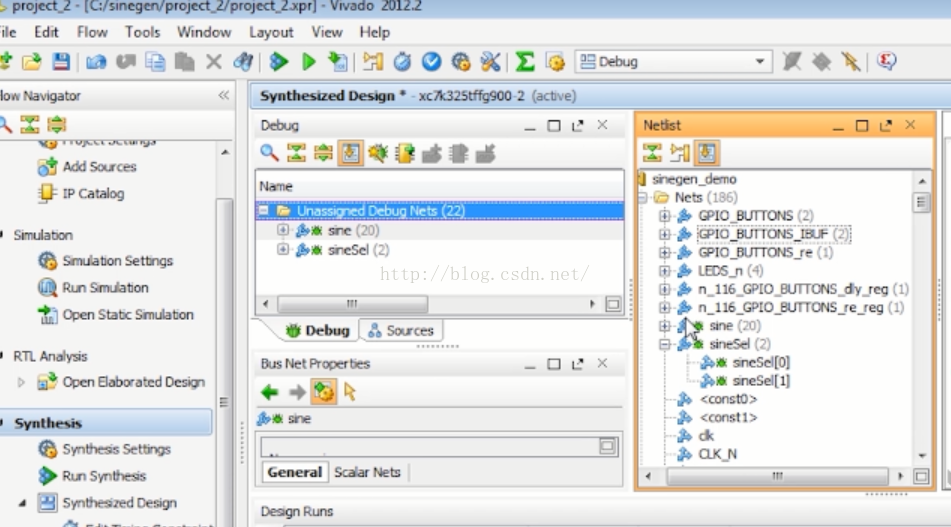

首先打开synthesis design,可以看到之前标记的debug信号,然后点击tools,选择set up debug

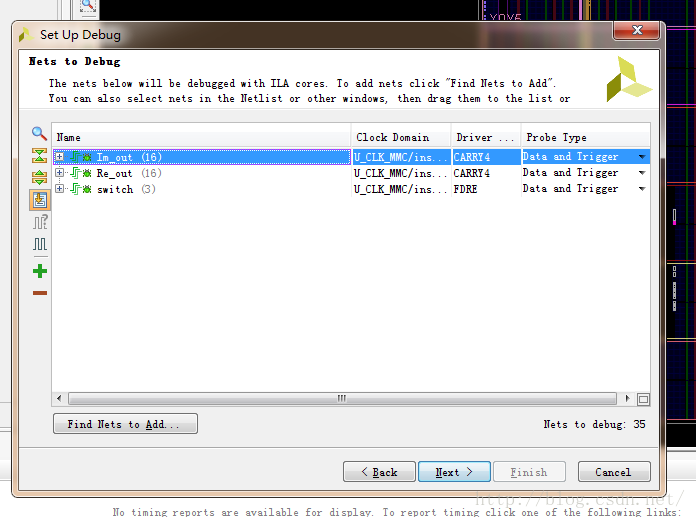

点击find nets to add,可以找到之前标记的信号,把信号添加完毕,检查Clock Domain是否正确,点击下一步。

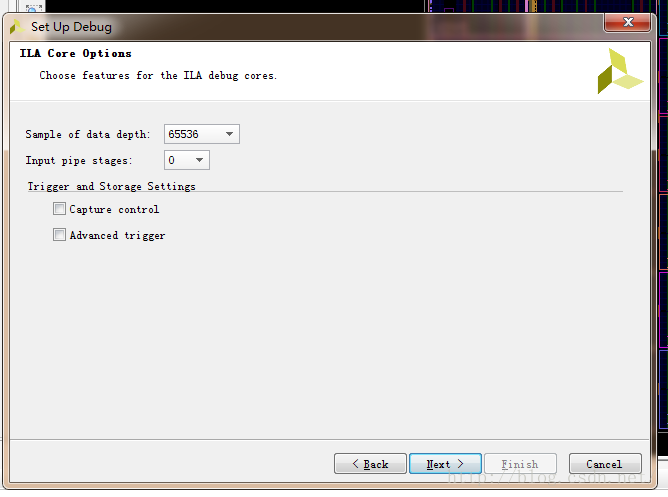

在下图中,将Capture control和Advanced trigger打上勾,这样在后面的调试中可以使用高级的捕获功能,再下一步,这样ILA的设置工作就完成了。

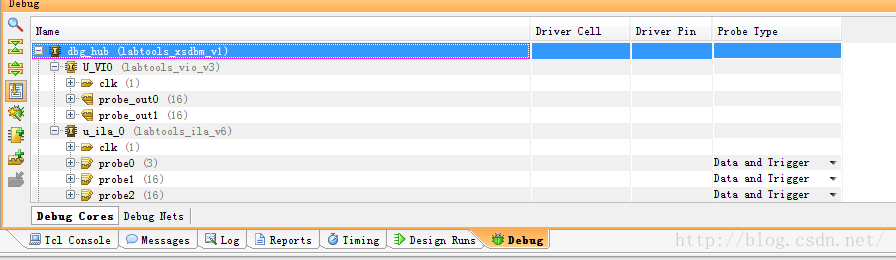

可以在debug视图中看到,Vivado自动帮我们插入了dbg_bug和ila,接下来生成bit文件,写入FPGA中,在Vivado的调试界面上就能进行在线的波形输出了。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/879425

推荐阅读

相关标签