热门标签

热门文章

- 130个Python小游戏,上班摸鱼我能玩一天【内附源码】_python自制小游戏_python小游戏大全

- 2Python图形用户界面(GUI)库tkinter的各种使用方法_python tkinter使用

- 3国庆征文获奖名单公布_csdn幸运奖

- 4conda出现http429报错:CondaHTTPError: HTTP 429 TOO MANY REQUESTS for url <xxx>_conda 429

- 5Django REST framework安全实践:轻松实现认证、权限与限流功能_django 限流开关

- 6详解各种光学仪器成像原理

- 7CondaHTTPError: HTTP None None for url

- 8面试 vivo 大模型算法岗(实习),被疯狂拷打。。。_vivo南京算法岗实习

- 9Python GUI编程—Tkinter的常用控件_tkinter 控件

- 10计算机网络 UDP协议与TCP协议首部_ipv6 udp 伪首部

当前位置: article > 正文

基于fpga_EP4CE6F17C8实现的呼吸灯

作者:weixin_40725706 | 2024-07-05 22:56:18

赞

踩

ep4ce6f17c8

前言

网上找资料时一般出现的是led灯1s从暗到亮,下一个1s从亮到暗,所以在此记录一篇2s的呼吸灯,也为日后自己复习提供一点帮助,结尾有源码。

实验手册(EP4CE6F17C8)

一、实验目的

四个LED灯2s从暗到亮,下一个2s从亮到暗,循环显示。

二、实验原理

理论原理

在fpga中,呼吸灯的实现是通过控制占空比的多少,输出两段,第一段:由暗到亮,占空比由0%到100%逐步递增,第二段:由亮到暗,占空比由100%到0%逐步递减

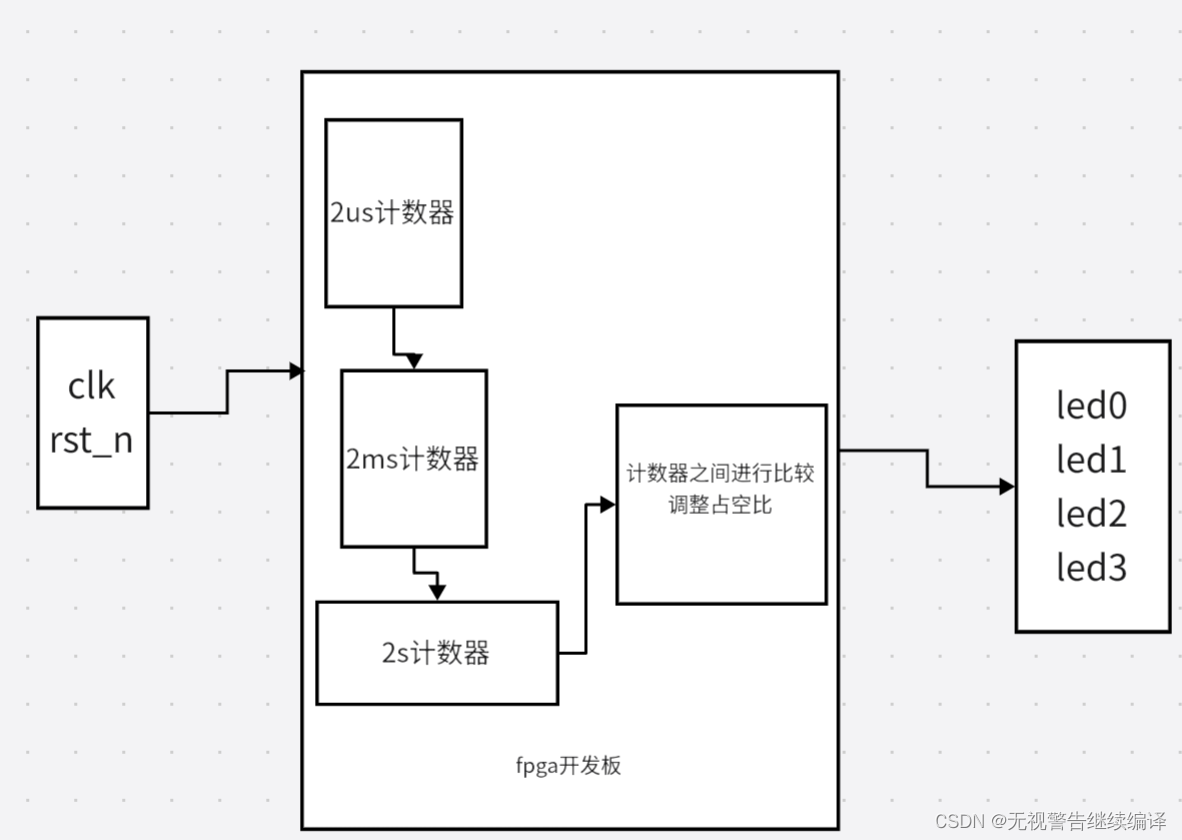

三、系统架构设计

- 呼气和吸气,周期为4秒。考虑呼气的过程,就是让led灯要有亮灭的变化,从暗到亮,再从亮到暗。

- 为了led的亮度变化比较流畅,也就是每隔2ms我们给led灯一个新的亮度,我们将2秒拆分为1000份的2ms,为了实现led灯亮度变化,每一份2ms波形的占空比都不能相同,且必须是连续增加或减小的。

- 2ms的时间内,我们一共有1000个状态,每一个状态就是一个占空比时间为2us。所以我们需要三个计数器。最后利用后面两个计数器cnt_2ms和cnt_2s的大小进行比较,来改变一个时钟周期内的占空比。

四、模块说明

1.模块端口信号列表

| 端口信号 | 信号类别 | 信号名称 | 信号作用 |

|---|---|---|---|

| input | wire | clk | 时钟信号 |

| input | wire | rst_n | 复位信号 |

| output | reg | led | led信号 |

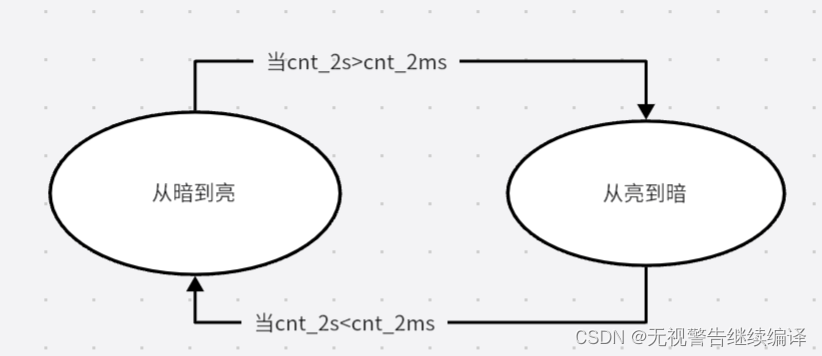

2.状态转移图

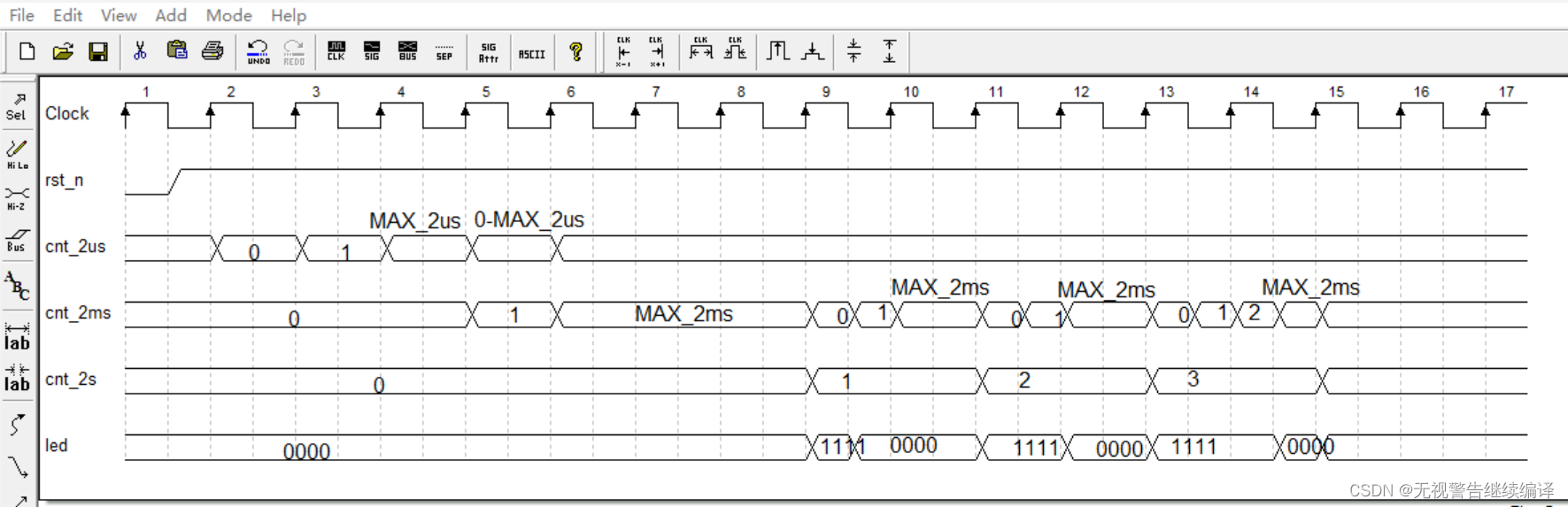

3.时序图

该图是用time gen来画的

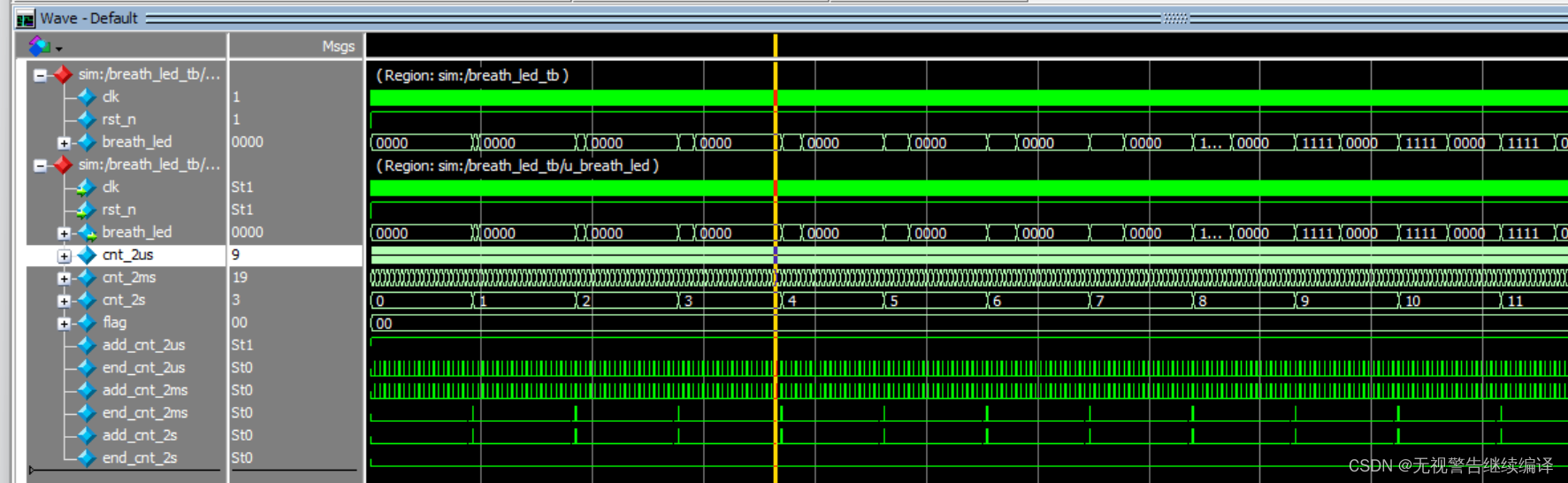

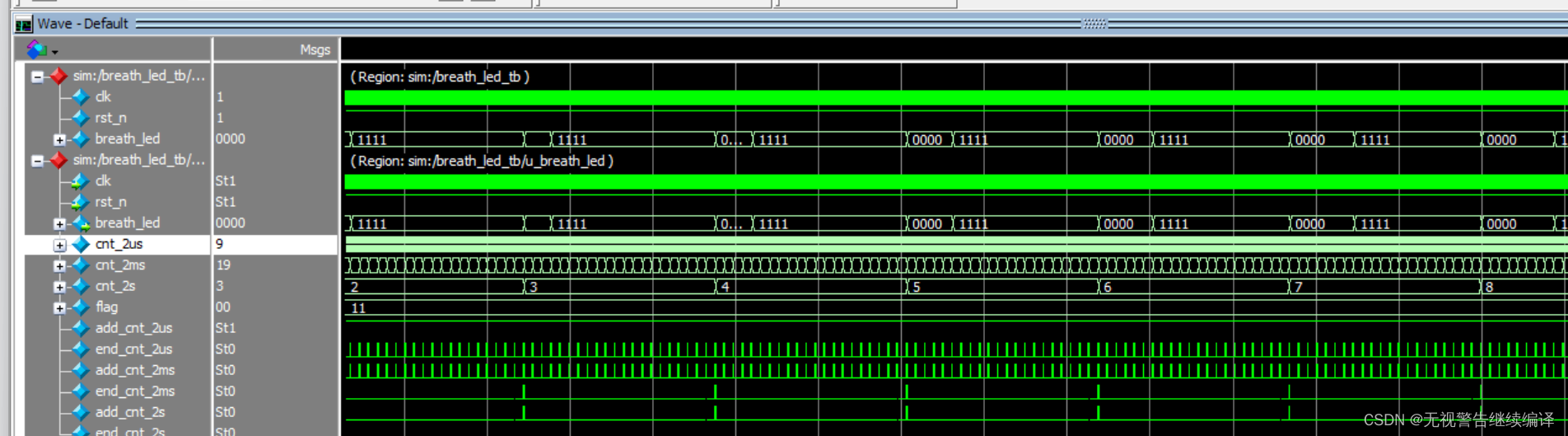

五、仿真波形图

-

这部分是从暗到亮的仿真波形,在breath_led一行我们可以很明显的看到从一开始基本看不见1111,到后面1111的占空比逐步扩大。

-

这部分则是从亮到暗,breath_led一行,0000的占空比逐步扩大

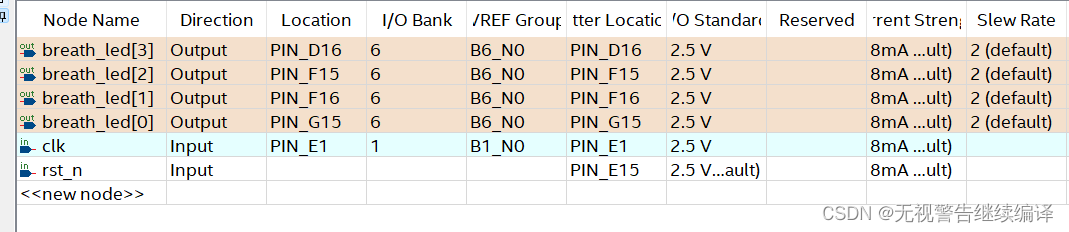

六、引脚分配

七、代码实现

module breath_led ( input clk , input rst_n , output reg [3:0] breath_led ); parameter MAX_2us = 10'd99 ; //2us //之所以2ms和2s都是999,这是因为这两个的开始信号我分别设置为cnt_2us的结束信号、cnt_2ms的结束信号 //记了1000次的us信号就等于2ms,2s也是这个道理 parameter MAX_2ms = 19'd999; //2ms = 1000 * 2us parameter MAX_2s = 19'd999; //2s = 1000 * 2ms reg [9:0] cnt_2us; reg [18:0] cnt_2ms; reg [18:0] cnt_2s; reg [1:0] flag; //状态转变标志,判断是从暗到亮还是从亮到暗 wire add_cnt_2us; //计数器开始信号 wire end_cnt_2us; //计数器结束信号 wire add_cnt_2ms; wire end_cnt_2ms; wire add_cnt_2s; wire end_cnt_2s; always @(negedge rst_n or posedge clk) begin if (!rst_n) begin cnt_2us <= 6'd0; end else if (add_cnt_2us) begin if (end_cnt_2us) begin cnt_2us <= 6'd0; end else begin cnt_2us <= cnt_2us + 6'd1; end end else begin cnt_2us <= cnt_2us; end end assign add_cnt_2us = 1'd1; assign end_cnt_2us = add_cnt_2us && cnt_2us == MAX_2us; always @(negedge rst_n or posedge clk) begin if (!rst_n) begin cnt_2ms <= 6'd0; end else if (add_cnt_2ms) begin if (end_cnt_2ms) begin cnt_2ms <= 6'd0; end else begin cnt_2ms <= cnt_2ms + 6'd1; end end else begin cnt_2ms <= cnt_2ms; end end assign add_cnt_2ms = end_cnt_2us; assign end_cnt_2ms = add_cnt_2ms && cnt_2ms == MAX_2ms; always @(negedge rst_n or posedge clk) begin if (!rst_n) begin cnt_2s <= 6'd0; end else if (add_cnt_2s) begin if (end_cnt_2s) begin cnt_2s <= 6'd0; end else begin cnt_2s <= cnt_2s + 6'd1; end end else begin cnt_2s <= cnt_2s; end end assign add_cnt_2s = end_cnt_2ms; assign end_cnt_2s = add_cnt_2s && cnt_2s == MAX_2s; //每隔两秒,信号翻转,进入下一状态 always @(posedge clk or negedge rst_n)begin if(!rst_n)begin flag <= 1'b0; end else if(end_cnt_2s)begin flag <= ~flag;//1s取反 end else begin flag <= flag; end end always @(negedge rst_n or posedge clk) begin if (!rst_n) begin breath_led <= 4'b0000; end //状态一:从暗到亮 else if (!flag)begin breath_led <= (cnt_2s > cnt_2ms)?4'b1111:4'b0000; end //状态二:从亮到暗 else if (flag) begin breath_led <= (cnt_2s > cnt_2ms)?4'b0000:4'b1111; end else begin breath_led <= breath_led; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

八、仿真代码

`timescale 1ns/1ns module breath_led_tb (); //激励信号 reg clk; reg rst_n; //响应信号 wire [3:0] breath_led; parameter CYCLE = 20; //完整代码中的计数时间长,故在此重新赋予短时的参数,以便观察结果 parameter MAX_2us = 10; parameter MAX_2ms = 20; parameter MAX_2s = 20; //产生时钟信号 always #(CYCLE/2) clk = ~clk; //产生激励 initial begin clk = 1'b0; rst_n = 1'b0; #(CYCLE); rst_n = 1'b1; #(2*(MAX_2us)*(MAX_2ms)*(MAX_2s)*CYCLE);//检测一个大周期:从暗到亮,从亮到暗 $stop; end //实例化 breath_led #( .MAX_2us(MAX_2us), .MAX_2ms(MAX_2ms), .MAX_2s(MAX_2s) ) u_breath_led( .clk(clk), .rst_n(rst_n), .breath_led(breath_led) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

九、板级验证效果

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/791184

推荐阅读

相关标签