- 1【毕业设计】大数据房价数据分析可视化 - python_爬取房屋信息可视化毕业设计

- 2pyspark+anaconda配置

- 3Mac小技巧之解除百度云盘限速_mac百度云盘怎么解除限速

- 4IKEv2协议协商流程: (IKE-SA-INIT 交换)第二包_ikev2交互过程

- 5Spring框架——介绍与基本概念!_spring框架最简单解释

- 6c++模拟实现动态分区存储管理_模拟实现动态分区存储管理 可变分区管理方式将内存除操作系统占用区域外的空间看

- 7PicGo+码云Gitee建立国内高速图床

- 8不安全的文件上传(任意文件上传)---服务端验证和绕过(MIME)_无限制上传危险类型的文件

- 9知名企业管理咨询品牌——乔诺是如何选择项目管理工具的?_乔诺咨询 背景

- 10人脸识别数据集的建立(dlib+opencv)及人脸识别

XILINX时序报告重要参数的含义_如何看xilinx的时序告警

赞

踩

本文讲解XILINX FPGA生成时许报告后各参数的含义,综合完后打开Report Timing Summary ,跟ISE不一样的是Vivado综合后的时序报告是可信的,但注意要将约束添加好,如果在综合时没有添加约束,可以在综合后添加,添加后可以直接查看时序报告,不用重新综合,

打开时序报告界面如下:

此处注意Check Timing里的叹号都要关注一下,重点关注有没有未约束的时钟和有没有LOOP。下面是Intra-Clock Path和Inter-Clock Path,在跨时钟域都约束好了的前提下重点关注Intra-Clock Path,此处以建立时间为例讲解各参数的含义。

选择一条路径,用原理图的方式打开如下所示:

这是一个典型的时序模型,由发起寄存器、组合逻辑、捕获寄存器3部分组成,时序路径包括源时钟路径、数据路径、目的时钟路径。时序报告包括4部分Summary、Source Clock Path、Data Path、Destination Clock Path。首先是Summary:

Slack:表示建立时间裕量,大于0表示建立时间满足,小于0表示建立时间不满足,Slack = Require Time - Arrive Time。

Data Path Delay:表示数据路径的延时,包括逻辑延时和布线延时,如果过大会导致建立时间不满足,此处给出了逻辑延时和布线延时所占的比重,可以帮助我们定位问题。

Logic Levels:表示组合逻辑的级数,级数过大会导致延时过大,从而导致建立时间违例。

Clock Path Skew:表示时钟抖动,一般不小于-0.5ns,如果小于-0.5就要定位问题并解决。

Clock Uncertainty:表示时钟不确定性,一般不大于0.1ns,大于0.1ns就占比过大,需要定位并解决。

下面是Source Clock Path和Data Path:

此处可以看出是以时钟发起沿为起点,数值以此累加最后得到Arrive Time。

下面是Destination Clock Path:

可以看到时钟沿到来时间为40ns,代表主频跑的是25M

可以看到最后加上-0.304ns后得到 Require Time,0.304就是建立时间,Require Time将建立时间减掉了,时钟在44.433ns的时候已经到了,如果此时数据还没到,建立时间肯定就不能满足了。

例如下面的代码

reg [31:0] sum_temp[SUM_NUM -1:0];

generate

genvar ii;

for(ii=0;ii<8;ii=ii+1)

begin

always@(posedge clk)begin

if(!rst_n)begin

sum_temp[ii] <= 0;

end

else if(state_c == SUM1)begin

sum_temp[ii] <= window[ii*8]+window[ii*8+1]+window[ii*8+2]+window[ii*8+3]+window[ii*8+4]+window[ii*8+5]+window[ii*8+6]+window[ii*8+7];

end

end

end

endgenerate

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

一个时钟周期内做了8个24bit的数据累加,此段代码跑50M的时候是没有时序违例的,当把时钟提高到200M,

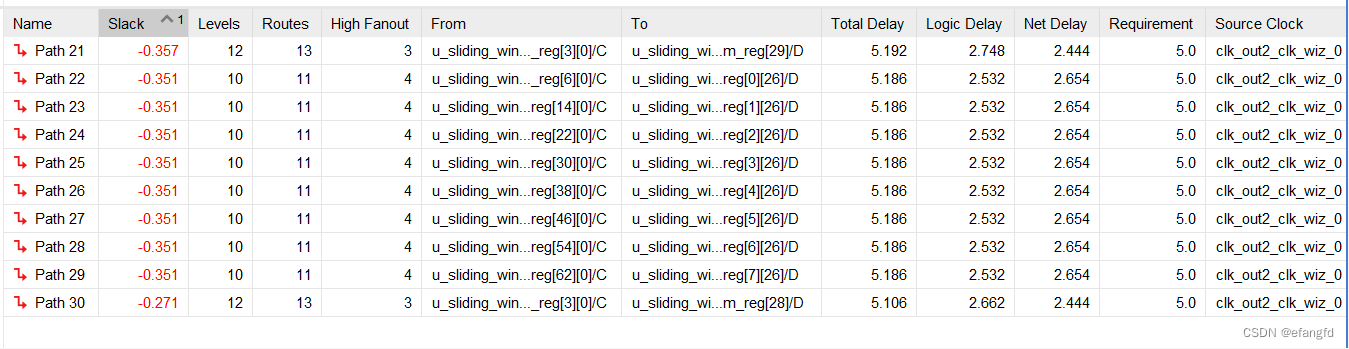

可以看到slck为负数了

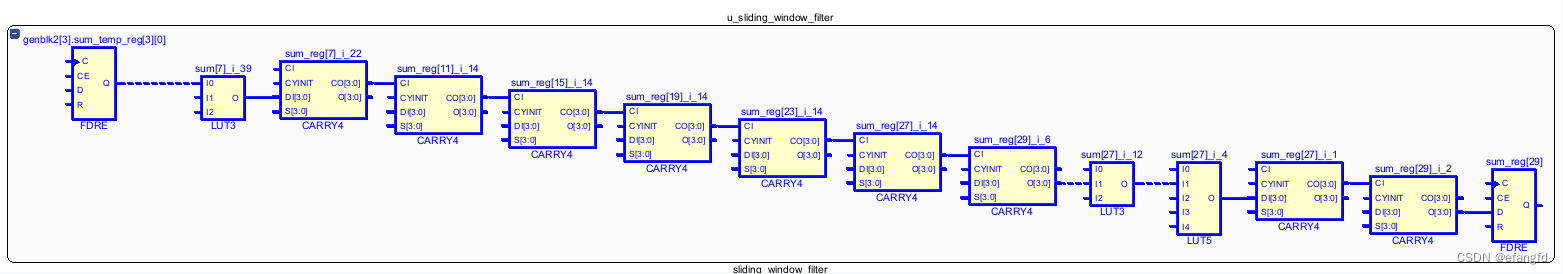

用原理图的方式看一下

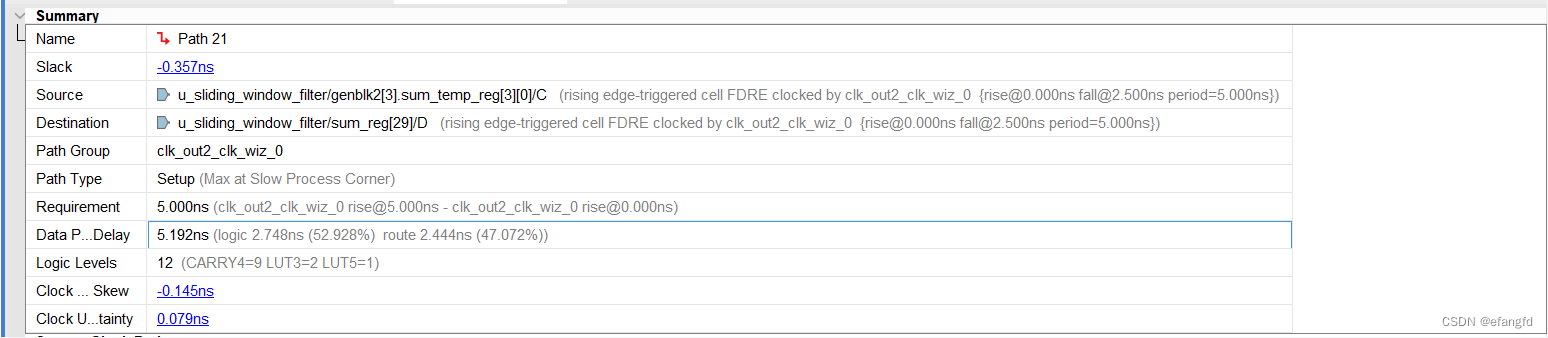

可以看到中间的组合逻辑级数非常多,延时非常大,看看时序报告里的summary

逻辑级数12级,数据路径延时达到了5.129ns,而我们的时钟周期是5ns,所以建立时间肯定是不满足的,

解决此问题的方法就是将求和改为流水线的方式。