热门标签

热门文章

- 1Halcon和Opencv区别和在视觉检测中的应用分析_opencv halcon 扫码对比

- 2java数组总结_Java数组知识点总结

- 3【数据分析实战经验】航空公司客户价值分析 LRMFC 模型(K-means聚类,工具python)_lrfmc模型

- 42024年数学建模深圳杯(东三省)A题(无人机编队)助攻论文&支撑材料.doc

- 5一款专业的音乐制作软件Studio One 6.6中文版怎么破解激活_studio one6.6

- 6又一个对标Sora的AI视频工具,Dream Machine,开始免费试用

- 7按钮级别权限管理数据库设计及后台接口实现

- 8使用Unity开发MetaQuest相关笔记教程_meta quest unity

- 9游族马寅龙:常见信息安全风险及应对方案_互联网收口

- 10Python抓取高考网图片

当前位置: article > 正文

FPGA时序分析和时序约束_fpga时钟约束的作用

作者:Monodyee | 2024-06-17 01:11:58

赞

踩

fpga时钟约束的作用

FPGA时序分析和时序约束

1时序分析和时序约束

时序分析的目的:

通过分析FPGA设计中各个寄存器之间的数据和时钟传输路径,来分析数据延迟和时钟延迟的关系。一个良好的设计系统,必然能够保证整个系统中的所有寄存器都能够正确的寄存数据。

数据和时钟路径是由EDA软件,通过对特定器件布局布线得到的。

时序约束的目的:

(1)告知EDA软件,本设计需要达到怎样的时序指标,然后EDA软件会根据时序的各个参数,尽量优化布局,以达到该指标。

(2)协助EDA软件进行分析设计的时序路径,以产生相应的时序报告。

2例子分析

2.1实现代码

`timescale 1ns / 1ps // module top( input sys_clk, input [0:0] a, input [0:0] b, output reg [0:0] c ); reg [0:0] a_reg; reg [0:0] b_reg; wire [0:0] c_wire; always@(posedge sys_clk) begin a_reg<=a; b_reg<=b; end assign c_wire=a_reg & b_reg; always@(posedge sys_clk) begin c<=c_wire; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

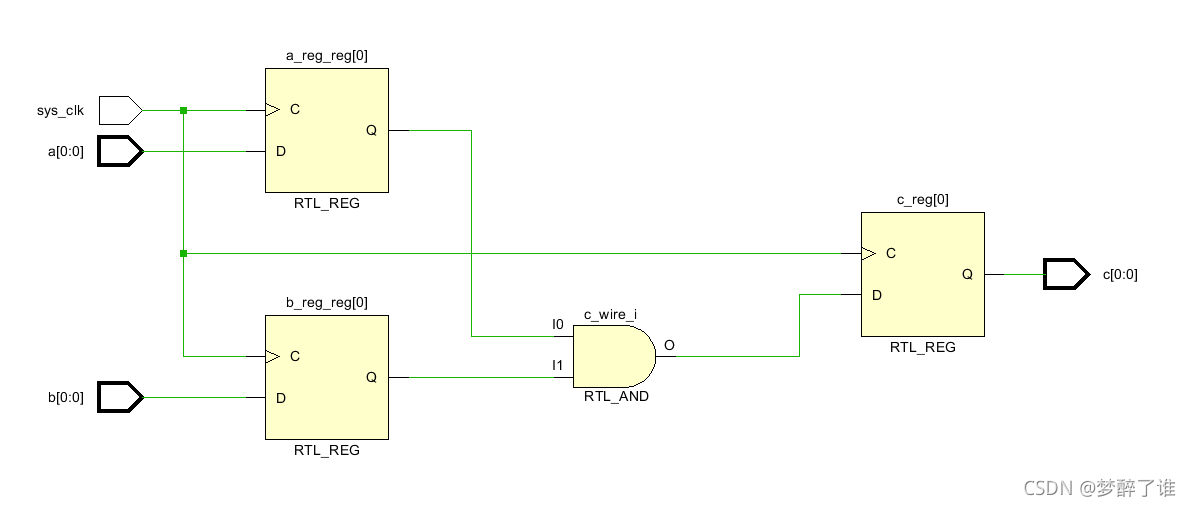

2.2时序分析的基本模型

D触发器需要用到DFF,与门需要用到LUT。

延迟产生原因:

(1)内部连线走线延迟;

(2)组合逻辑电路延迟。

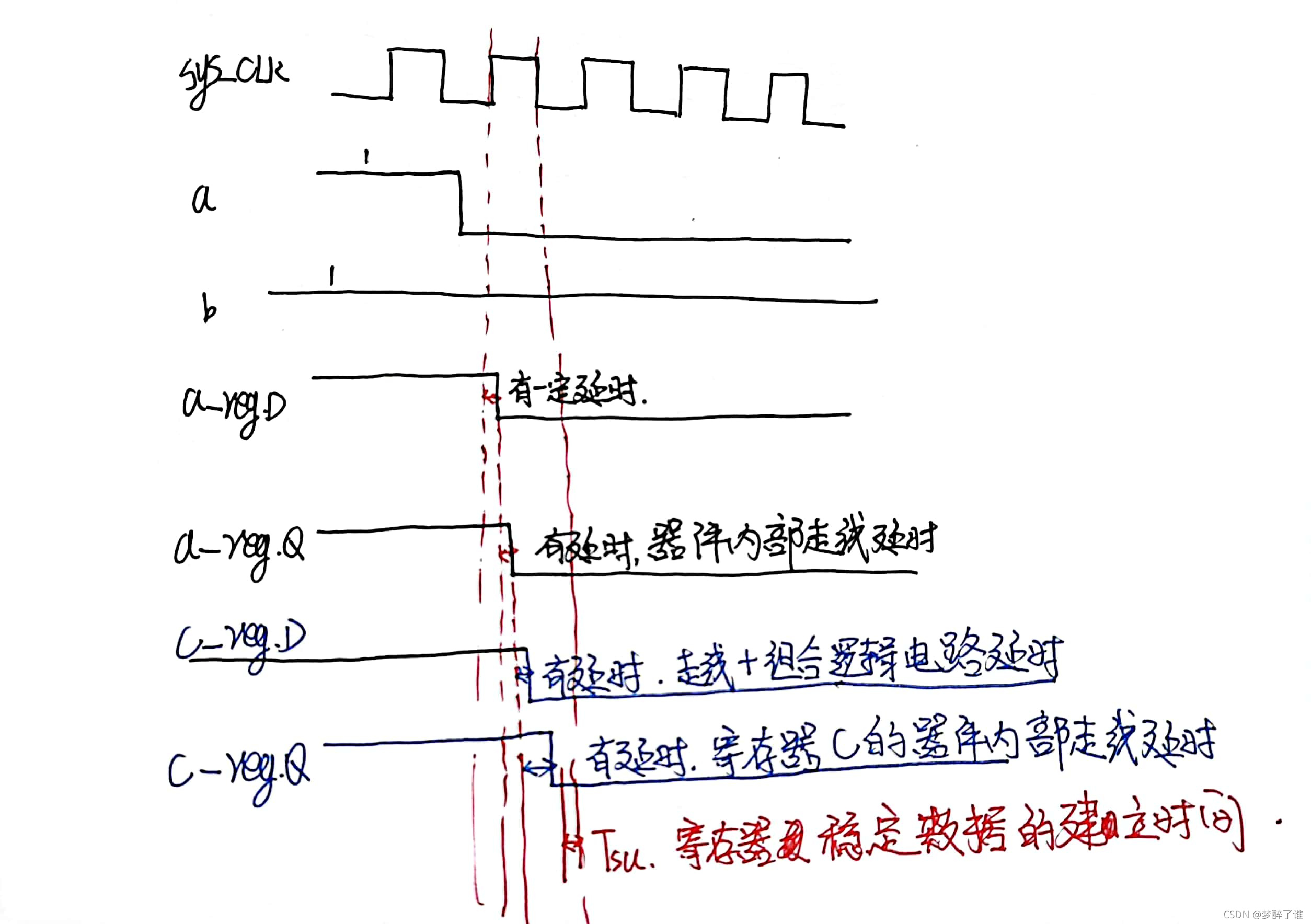

Tco:时钟上升沿到达D触发器的D端 到 数据输出到Q端的延迟。

Tsu:寄存器稳定数据的建立时间,由目的寄存器自身的特性决定。在时钟信号的上升沿到达时钟接口时,触发器的数据输入端(D)必须提前N纳秒稳定下来,否则无法保证数据正确存储。也就是说,D触发器D端口的数据必须比时钟上升沿提前Nns到达D触发器的端口。

为了保证正确接收数据,内部连线走线延迟+组合逻辑电路延迟必须小于sys_clk- Tsu。如下图所示。

例子分析:

a=1,b=1;间隔一定的时间,a变成0;

图中,a_reg_D指的是寄存器a的D端,a_reg_Q指的是寄存器a的Q端。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Monodyee/article/detail/729021

推荐阅读

相关标签