热门标签

热门文章

- 1OPENCV中的LBPH算法_lbph算法原理说明

- 24天轻松玩转Docker|阿里手写笔记。_4 天轻松玩转 docker

- 3Mina 单双向认证_mina 单向认证

- 4Java-Spring Boot 集成海康威视明眸门禁 布防|报警|回调|获取事件|查询用户信息_明眸门禁设备代码

- 5Postfix+Dovecot+Roundcube开源邮件系统搭建系列5:Roundcube安装配置(含Nginx+PHP部署配置)

- 6c语言常量以及变量的应用_start experimental instance of visual studio 2022

- 7如何使用 ChatGPT 总结书籍、文章或研究论文?_chatgpt总结论文

- 8【AIGC新职业】之:什么是AIGC?其对创意设计行业有什么重要意义?_aigc+传统专业

- 9Python采集热搜评论数据,制作词云分析,又是吃瓜的一天_python怎么做用户评论的词云图分析

- 10大学生发展规划与就业指导(三)万学网答案_万学企业求职深度准备答案

当前位置: article > 正文

FPGA学习笔记——AXI总线协议解析_fpgaaxi

作者:IT小白 | 2024-07-10 12:17:19

赞

踩

fpgaaxi

简介

AXI(Advanced eXtensible Interface)是一种总线协议,该协议是ARM公司提出的AMBA3.0协议中的一部分。AXI总线目前已经发展到AXI5,在FPGA平台上常用的是AXI4。

AXI4接口有三种类型:

- AXI4(AXI4-Full):满足高性能内存映射需求。支持256长度突发(burst)传输。

- AXI4-Lite:对于简单的、低吞吐量的内存映射通信。突发长度只能为1,数据位宽只支持32位或者64位。

- AXI4-Stream:用于高速流数据。不需要地址,允许无限的数据突发大小。

读写通道

AXI-Full和AXI-Lite都包含五个不同的通道:

- 写地址通道(Write Address Channel)

- 写数据通道(Write Data Channel)

- 写响应通道(Write Response Channel)

- 读地址通道(Read Address Channel)

- 读数据通道(Read Data Channel)

注意:没有读响应通道,因为写地址和写数据方向都是主->从,那么需要额外建立一个从->主的通道来响应写入成功。而读地址方向是主->从,读数据方向是从->主,所以不需要额外的通道。所以没有读响应通道,但是有读响应信号。

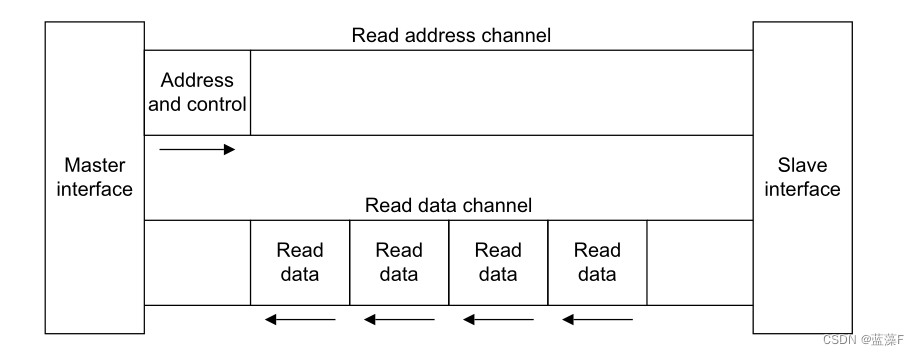

AXI4读地址和读数据通道示意:

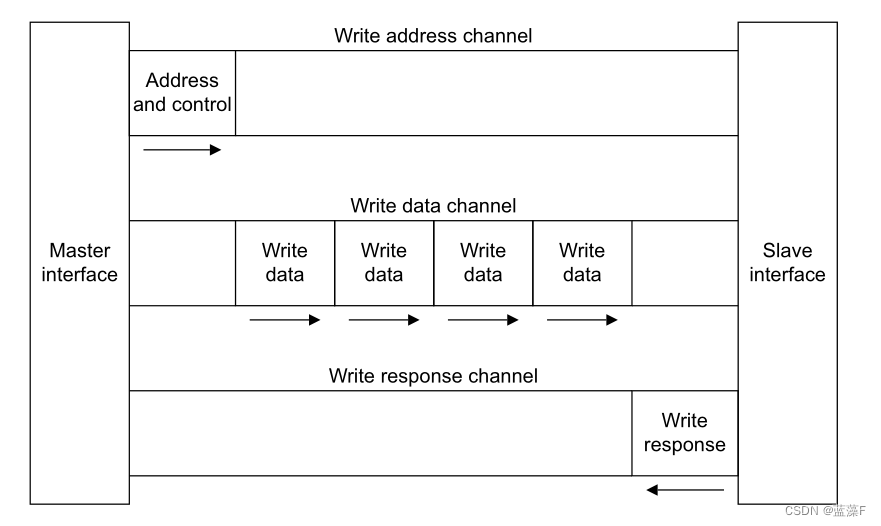

AXI4写地址,写数据和写响应通道示意:

握手信号

AXI每个通道都有两个握手信号:VALID和READY。为了防止死锁,在任何事务中VALID信号不能依赖于另一个组件的READY信号,READY信号可以等待VALID信号。实际上,在比如Xilinx BRAM等IP中,都是先给VALID,对应的READY才会拉高,所以等READY再使能VALID是不对的工作时序。

声明:本文内容由网友自发贡献,转载请注明出处:【wpsshop】

推荐阅读

相关标签