- 1秋招提前批!大厂offer的捷径!_校招提前批要投简历吗

- 2【软件工程作业】 习题三_银行计算机储蓄系统

- 3动态规划(带图)——查找两个字符串a,b中的最长公共子串_求两个字符串的最长公共子串时间复杂度

- 4IntelliJ Idea 常用快捷键列表 _idea匿名内部类快捷键

- 5燃气管道老化,怎样能实时监测管网情况?

- 6Android Telephony Radio Layer Interface _telephone-radio唤醒

- 7mysql语句及优化之----join以及join的优化_a 和 b 两个表做等值连接(inner join) 怎么优化

- 8python gui是什么_python gui是什么?

- 9五年Java开发经验,4面阿里成功拿下offer,分享一下个人面经!_5年经验的java开发

- 10oracle 12c rac-单机 dg搭建_oracle 12c dg 部署

MCU软核 2. Xilinx Artix7上运行tinyriscv_xilinx spi核

赞

踩

0. 环境

- ubuntu18

- win10 + vivado 2018.3

- git desktop

- XC7A35TV12核心板

- ft2232hl小板(用于程序烧录)

1. git克隆源码

Git Desktop -> File -> Clone repository ->

-> URL: https://gitee.com/liangkangnan/tinyriscv/

-> Local path: D:\Workspaces\GitHub\tinyriscv

2. vivado创建工程

Create Project -> Next ->

-> Project name: tinyriscv

-> Project location: E:/Workspaces/vivado2018/XC7A35TV12/

-> 勾选 Create project subdirectory

-> RTL Project

-> Next -> Next

-> xc7a35tftg256-1

-> finish

添加源码

Add Sources -> Add or create design sources -> Next

-> Add Directories -> D:\Workspaces\GitHub\tinyriscv\rtl

-> 勾选 Copy sources into project

添加约束文件

Add Sources -> Add or create constrains -> Next

-> Add Files -> D:\Workspaces\GitHub\tinyriscv\fpga\constrs\tinyriscv.xdc修改约束文件,用到的每个引脚都需要添加约束。jtag、gpio、spi都使用开发板引出的但未被使用的引脚。

- set_property PACKAGE_PIN D4 [get_ports clk]

- set_property PACKAGE_PIN C4 [get_ports rst]

- # uart to usb

- set_property PACKAGE_PIN C7 [get_ports uart_rx_pin]

- set_property PACKAGE_PIN M14 [get_ports uart_tx_pin]

- set_property PACKAGE_PIN D11 [get_ports uart_debug_pin] # D11 S1按键

- # led

- set_property PACKAGE_PIN K12 [get_ports over]

- set_property PACKAGE_PIN L14 [get_ports succ]

- set_property PACKAGE_PIN L13 [get_ports halted_ind]

- # jtag

- set_property PACKAGE_PIN M15 [get_ports jtag_TCK]

- set_property PACKAGE_PIN R16 [get_ports jtag_TMS]

- set_property PACKAGE_PIN P16 [get_ports jtag_TDI]

- set_property PACKAGE_PIN R15 [get_ports jtag_TDO]

- # gpio

- set_property PACKAGE_PIN P15 [get_ports {gpio[0]}]

- set_property PACKAGE_PIN T15 [get_ports {gpio[1]}]

- # SPI

- set_property PACKAGE_PIN P14 [get_ports spi_miso]

- set_property PACKAGE_PIN T14 [get_ports spi_mosi]

- set_property PACKAGE_PIN N14 [get_ports spi_ss]

- set_property PACKAGE_PIN N12 [get_ports spi_clk]

-

- set_property IOSTANDARD LVCMOS33 [get_ports clk]

- set_property IOSTANDARD LVCMOS33 [get_ports rst]

- set_property IOSTANDARD LVCMOS33 [get_ports over]

- set_property IOSTANDARD LVCMOS33 [get_ports succ]

- set_property IOSTANDARD LVCMOS33 [get_ports halted_ind]

- set_property IOSTANDARD LVCMOS33 [get_ports uart_rx_pin]

- set_property IOSTANDARD LVCMOS33 [get_ports uart_tx_pin]

- set_property IOSTANDARD LVCMOS33 [get_ports uart_debug_pin]

- set_property IOSTANDARD LVCMOS33 [get_ports jtag_TCK]

- set_property IOSTANDARD LVCMOS33 [get_ports jtag_TMS]

- set_property IOSTANDARD LVCMOS33 [get_ports jtag_TDI]

- set_property IOSTANDARD LVCMOS33 [get_ports jtag_TDO]

- set_property IOSTANDARD LVCMOS33 [get_ports {gpio[0]}]

- set_property IOSTANDARD LVCMOS33 [get_ports {gpio[1]}]

- set_property IOSTANDARD LVCMOS33 [get_ports spi_miso]

- set_property IOSTANDARD LVCMOS33 [get_ports spi_mosi]

- set_property IOSTANDARD LVCMOS33 [get_ports spi_ss]

- set_property IOSTANDARD LVCMOS33 [get_ports spi_clk]

-

- set_property BITSTREAM.CONFIG.UNUSEDPIN Pullnone [current_design]

- set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

- set_property BITSTREAM.CONFIG.SPI_FALL_EDGE YES [current_design]

- set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

-

- set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jtag_TCK_IBUF]

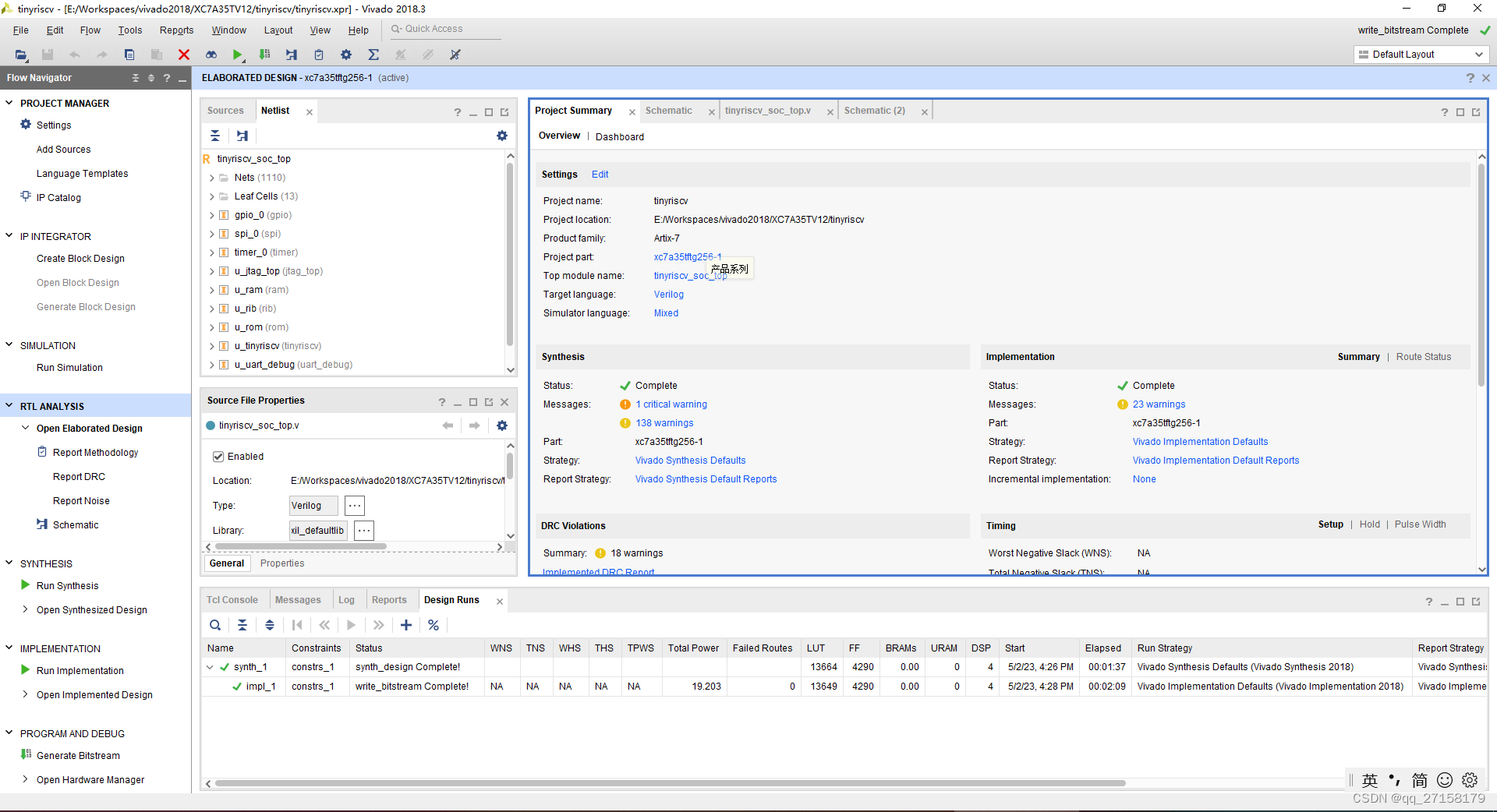

编译

-> Run Systhesis

-> Run Implementation

-> Generate Bitstream

下载

Open Hardware Manager -> Open Target -> Auto Connect -> 右键Hardware栏内的xc7a35t_0 -> 点击Program device

-> Bitstream file: E:/Workspaces/vivado2018/XC7A35TV12/tinyriscv/tinyriscv.runs/impl_1/tinyriscv_soc_top.bit

固化

Tools -> Generate Memory Configuration File ->

-> MCS

-> 128MB

-> File name: E:/Workspaces/vivado2018/XC7A35TV12/tinyriscv/tinyriscv.runs/impl_1/tinyriscv_soc_top.mcs

-> Interface: SPIx4

-> 勾选 Load bitstream files

-> Bitfile: E:/Workspaces/vivado2018/XC7A35TV12/tinyriscv/tinyriscv.runs/impl_1/tinyriscv_soc_top.bit

请先手动删除

E:/Workspaces/vivado2018/XC7A35TV12/tinyriscv/tinyriscv.runs/impl_1

下的

tinyriscv_soc_top.mcs

tinyriscv_soc_top.prm

-> OK

-> Add Configuration Memory Device -> 输入n25q128-3.3v -> OK

烧写

-> Configuration file: E:/Workspaces/vivado2018/XC7A35TV12/tinyriscv/tinyriscv.runs/impl_1/tinyriscv_soc_top.mcs

-> PRM file: E:/Workspaces/vivado2018/XC7A35TV12/tinyriscv/tinyriscv.runs/impl_1/tinyriscv_soc_top.prm

-> OK

3. c语言程序编译

git clone https://gitee.com/liangkangnan/tinyriscv/

安装交叉编译工具

到这里下载xpack-riscv-none-embed-gcc-10.2.0-1.2-linux-x64.tar.gz

https://github.com/xpack-dev-tools/riscv-none-elf-gcc-xpack/releases/

拷贝到虚拟机下的

/home/xxjianvm/work/xpack-riscv-none-embed-gcc-10.2.0-1.2-linux-x64.tar.gz

解压

tar -zvxf xpack-riscv-none-embed-gcc-10.2.0-1.2-linux-x64.tar.gz配置环境变量

修改common.mk

把

RISCV_PATH := $(TOOLCHAIN_DIR)/tools/gnu-mcu-eclipse-riscv-none-gcc-8.2.0-2.2-20190521-0004-win64/

修改为

- # RISCV_PATH := $(TOOLCHAIN_DIR)/tools/gnu-mcu-eclipse-riscv-none-gcc-8.2.0-2.2-20190521-0004-win64/

- RISCV_PATH := /home/xxjianvm/work/xpack-riscv-none-embed-gcc-10.2.0-1.2/

验证:

riscv-none-embed-gcc -v编译

- cd /home/xxjianvm/work/tinyriscv/tests/example/uart_tx

- make

-

- cd /home/xxjianvm/work/tinyriscv/sim

- python sim_new_nowave.py ../tests/example/uart_tx/uart_tx.bin inst.data

Python 错误 SyntaxError: Non-ASCII character ‘\xe4’ in file

代码最顶部加一句 #coding:utf-8

python sim_new_nowave.py ../tests/example/uart_tx/uart_tx.bin inst.data3. openocd

win10下操作。需要连接ft2232hl和 tinyriscv的 jtag

3.1 运行

下载最新的openocd

https://gnutoolchains.com/arm-eabi/openocd/

打开命令行

- cd mcu tinyriscv\openocd-20230202\OpenOCD-20230202-0.12.0\bin

- G:

- openocd -f ft2232h.cfg -f tinyriscv.cfg

- mcu tinyriscv\openocd-20230202\OpenOCD-20230202-0.12.0\bin>openocd -f ft2232h.cfg -f tinyriscv.cfg

- Open On-Chip Debugger 0.12.0 (2023-02-02) [https://github.com/sysprogs/openocd]

- Licensed under GNU GPL v2

- libusb1 09e75e98b4d9ea7909e8837b7a3f00dda4589dc3

- For bug reports, read

- http://openocd.org/doc/doxygen/bugs.html

- DEPRECATED! use 'adapter driver' not 'interface'

- DEPRECATED! use 'ftdi vid_pid' not 'ftdi_vid_pid'

- DEPRECATED! use 'ftdi channel' not 'ftdi_channel'

- DEPRECATED! use 'adapter speed' not 'adapter_khz'

- DEPRECATED! use 'ftdi layout_init' not 'ftdi_layout_init'

- DEPRECATED! use 'ftdi layout_signal' not 'ftdi_layout_signal'

- DEPRECATED! use 'ftdi layout_signal' not 'ftdi_layout_signal'

- DEPRECATED! use 'adapter speed' not 'adapter_khz'

- DEPRECATED! use 'adapter srst pulse_width' not 'adapter_nsrst_assert_width'

- DEPRECATED! use 'adapter driver' not 'interface'

- Warn : Interface already configured, ignoring

- Warn : Transport "jtag" was already selected

- Error: libusb_open() failed with LIBUSB_ERROR_NOT_SUPPORTED

- Info : clock speed 1000 kHz

- Info : JTAG tap: riscv.cpu tap/device found: 0x1e200a6f (mfg: 0x537 (Wuhan Xun Zhan Electronic Technology), part: 0xe200, ver: 0x1)

- Info : datacount=3 progbufsize=1

- Info : Examined RISC-V core; found 2 harts

- Info : hart 0: XLEN=32, misa=0x1b0

- Info : starting gdb server for riscv.cpu on 3333

- Info : Listening on port 3333 for gdb connections

- Info : Listening on port 6666 for tcl connections

- Info : Listening on port 4444 for telnet connections

3.2 telnet

win10 -> 控制面板 -> 程序 -> 程序和功能 -> 启用或关闭Windows 功能 -> telnet客户端 -> 确认

打开命令行

telnet localhost 4444将固件下载到FPGA

load_image C:/Users/qjfen/Desktop/uart_tx.bin 0x0 bin 0x0 0x1000000使用verify_image命令来校验是否下载成功,如下所示:

verify_image C:/Users/qjfen/Desktop/uart_tx.bin 0x0 bin 0x0如果下载出错的话会有提示的,没有提示则说明下载成功。

最后执行以下命令让程序跑起来:

resume 0- > load_image C:/Users/qjfen/Desktop/uart_tx.bin 0x0 bin 0x0 0x1000000

- 2244 bytes written at address 0x00000000

- downloaded 2244 bytes in 0.058930s (37.187 KiB/s)

-

- > verify_image C:/Users/qjfen/Desktop/uart_tx.bin 0x0 bin 0x0

- verified 2244 bytes in 0.106216s (20.632 KiB/s)

-

- > resume 0

- >

注意:这种方法下载请拉低uart_debug_en引脚。这个串口引脚有点像UART BOOT。

退出

quit3.3 ft2232h.cfg内容

- #

- # FT2232HL for openOCD Device

- #

- # According to the sch file, it uses BDBUS.

- #

- interface ftdi

- ftdi_vid_pid 0x0403 0x6010

- # ftdi_channel 0 is port ADBUS, ftdi_channel 1 is port BDBUS.

- ftdi_channel 1

- transport select jtag

- adapter_khz 1000

- ftdi_layout_init 0x00F8 0x00fb

- ftdi_layout_signal nSRST -oe 0x0040

- ftdi_layout_signal ntRST -oe 0x0010

3.4 tinyriscv.cfg内容

- adapter_khz 1000

-

- reset_config srst_only

- adapter_nsrst_assert_width 100

-

- interface cmsis-dap

-

- transport select jtag

-

- #debug_level 3

-

- set _CHIPNAME riscv

- jtag newtap $_CHIPNAME cpu -irlen 5 -expected-id 0x1e200a6f

-

- set _TARGETNAME $_CHIPNAME.cpu

- target create $_TARGETNAME riscv -chain-position $_TARGETNAME

-

- riscv set_reset_timeout_sec 1

-

- init

-

- halt

参考:Windows 10操作系统上使用telnet命令(图文),https://blog.csdn.net/m0_46015143/article/details/119379275

参考:FT2232作为JTAG烧录器的使用步骤详解,https://blog.csdn.net/windyhigh/article/details/128406376